百兆以太网IC IP101G规格书

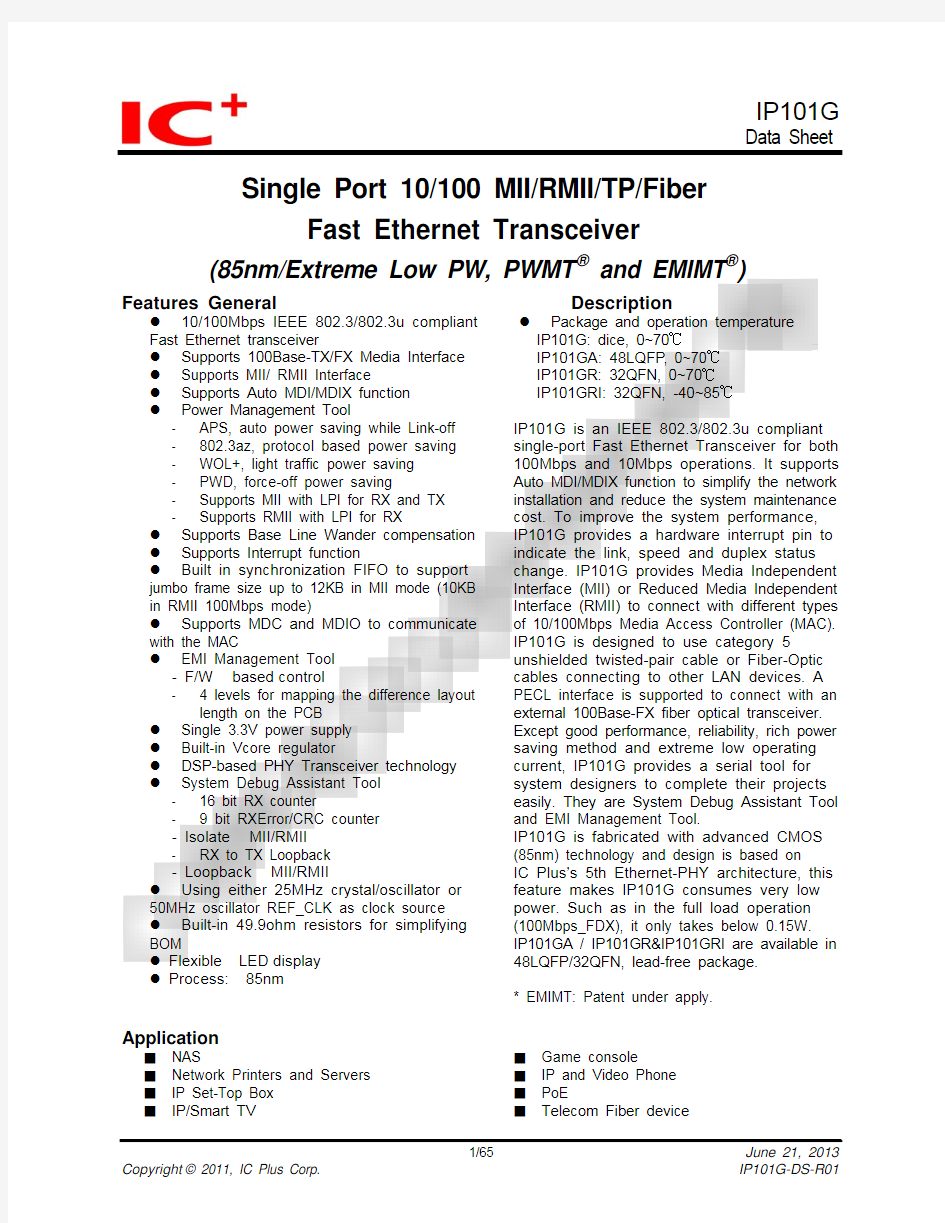

Single Port 10/100 MII/RMII/TP/Fiber

Fast Ethernet Transceiver

(85nm/Extreme Low PW, PWMT ? and EMIMT ?)

Features General Description

z 10/100Mbps IEEE 802.3/802.3u compliant Fast Ethernet transceiver

z Supports 100Base-TX/FX Media Interface z Supports MII/ RMII Interface

z Supports Auto MDI/MDIX function z Power Management Tool

- APS, auto power saving while Link-off - 802.3az, protocol based power saving - WOL+, light traffic power saving - PWD, force-off power saving

- Supports MII with LPI for RX and TX - Supports RMII with LPI for RX

z Supports Base Line Wander compensation z Supports Interrupt function

z Built in synchronization FIFO to support jumbo frame size up to 12KB in MII mode (10KB in RMII 100Mbps mode)

z Supports MDC and MDIO to communicate with the MAC

z EMI Management Tool - F/W based control

- 4 levels for mapping the difference layout

length on the PCB

z Single 3.3V power supply z Built-in Vcore regulator

z DSP-based PHY Transceiver technology z System Debug Assistant Tool - 16 bit RX counter

- 9 bit RXError/CRC counter - Isolate MII/RMII - RX to TX Loopback - Loopback MII/RMII

z Using either 25MHz crystal/oscillator or 50MHz oscillator REF_CLK as clock source

z Built-in 49.9ohm resistors for simplifying BOM

z Flexible LED display z Process: 85nm

z

Package and operation temperature

IP101G: dice, 0~70℃

IP101GA: 48LQFP , 0~70℃ IP101GR: 32QFN, 0~70℃ IP101GRI: 32QFN, -40~85℃

IP101G is an IEEE 802.3/802.3u compliant single-port Fast Ethernet Transceiver for both 100Mbps and 10Mbps operations. It supports Auto MDI/MDIX function to simplify the network installation and reduce the system maintenance cost. To improve the system performance, IP101G provides a hardware interrupt pin to indicate the link, speed and duplex status change. IP101G provides Media Independent Interface (MII) or Reduced Media Independent Interface (RMII) to connect with different types of 10/100Mbps Media Access Controller (MAC). IP101G is designed to use category 5 unshielded twisted-pair cable or Fiber-Optic cables connecting to other LAN devices. A PECL interface is supported to connect with an external 100Base-FX fiber optical transceiver. Except good performance, reliability, rich power saving method and extreme low operating current, IP101G provides a serial tool for system designers to complete their projects easily. They are System Debug Assistant Tool and EMI Management Tool.

IP101G is fabricated with advanced CMOS (85nm) technology and design is based on

IC Plus’s 5th Ethernet-PHY architecture, this feature makes IP101G consumes very low power. Such as in the full load operation (100Mbps_FDX), it only takes below 0.15W. IP101GA / IP101GR&IP101GRI are available in 48LQFP/32QFN, lead-free package.

* EMIMT: Patent under apply.

Application

■ NAS

■ Network Printers and Servers ■ IP Set-Top Box ■

IP/Smart TV

■ Game console

■ IP and Video Phone ■ PoE

■

Telecom Fiber device

Table Of Contents

Table Of Contents (2)

List of Figures (4)

List of Tables (5)

Revision History (6)

Features comparison between IP101G and IP101A/IP101AH (7)

Transmit and Receive Data Path Block Diagram (8)

1Pin diagram (9)

2Dice pad information (11)

3Pin description (12)

3.1IP101GA pin description (12)

3.2IP101GR/GRI pin description (16)

4Register Descriptions (19)

4.1Register Page mode Control Register (20)

4.2MII Registers (20)

4.3MMD Control Register (30)

4.4MMD Data Register (31)

4.5RX Counter Register (34)

4.6LED Pin Control Register (35)

4.7WOL+ Control Register (36)

4.8UTP PHY Specific Control Register (39)

4.9Digital IO Pin Control Register (39)

5Function Description (41)

5.1Major Functional Block Description (41)

5.1.1Transmission Description (41)

5.1.2MII and Management Control Interface (42)

5.1.3RMII Interface (43)

5.1.4Flexible Clock Source (45)

5.1.5Auto-Negotiation and Related Information (45)

5.1.6Auto-MDIX function (46)

5.2PHY Address Configuration (46)

5.3Power Management Tool (47)

5.3.1Auto Power Saving Mode (47)

5.3.2IEEE802.3az EEE (Energy Efficient Ethernet) (48)

5.3.3Force power down (48)

5.3.4WOL+ operation mode (48)

5.4LED Mode Configuration (52)

5.5LED Blink Timing (52)

5.6Repeater Mode (52)

5.7Interrupt (52)

5.8Miscellaneous (52)

5.9Serial Management Interface (53)

5.10Fiber Mode Setting (54)

5.11Jumbo Frame (54)

6Layout Guideline (55)

6.1General Layout Guideline (55)

6.2Twisted Pair recommendation (55)

7Electrical Characteristics (56)

7.1Absolute Maximum Rating (56)

7.2DC Characteristics (56)

7.3Crystal Specifications (57)

7.4AC Timing (58)

7.4.1Reset, Pin Latched-in, Clock and Power Source (58)

7.4.2MII Timing (59)

7.4.3RMII Timing (60)

7.4.4SMI Timing (61)

7.5Thermal Data (61)

8Order Information (62)

9Physical Dimensions (63)

9.148-PIN LQFP (63)

9.232-PIN QFN (64)

List of Figures

Figure 1 Flow chart of IP101G (8)

Figure 2 IP101GA 48 Pin Diagram (9)

Figure 3 IP101GR/GRI 32 Pin Diagram (10)

Figure 4 IP101G dice pad information (11)

Figure 5 LPI transition (43)

Figure 6 IP101G/GA/GR/GRI MII Mode with LPI transition Block Diagram (43)

Figure 7 IP101G/GA/GR/GRI MII Mode without LPI transition Block Diagram (43)

Figure 8 IP101G RMII Mode with internal clock Block Diagram (44)

Figure 9 IP101G RMII Mode with external clock Block Diagram (44)

Figure 10 IP101G RMII Clock Application Circuit (45)

Figure 11 IP101G link speed and EEE ability programming guide (46)

Figure 12 PHY Address Configuration (47)

Figure 13 Magic Packet Format (49)

Figure 14 Sleep or wake up automatically programming guide (50)

Figure 15 MAC control sleep or wake up programming guide (51)

Figure 16 MDC/MDIO Format (53)

Figure 17 IP101G Fiber Mode Setting (54)

Figure 18 Reset, Pin Latched-In, Clock and Power Source Timing Requirements (58)

Figure 19 MII Transmit Timing Requirements (59)

Figure 20 MII Receive Timing Specifications (59)

Figure 21 RMII Transmit Timing Requirements (60)

Figure 22 RMII Receive Timing Specifications (60)

Figure 23 SMI Timing Requirements (61)

Figure 24 48-PIN LQFP Dimension (63)

Figure 25 32-PIN QFN Dimension (64)

List of Tables

Table 1 Features comparison between IP101G and IP101A/IP101AH (7)

Table 2 Register Map (19)

Table 3 Flexible Clock Source Setting (45)

Table 4 PHY Address Configuration (47)

Table 5 WOL+ operation mode (49)

Table 6 LED Mode 1 Function (52)

Table 7 LED Mode 2 Function (52)

Table 8 LED Blink Timing (52)

Table 9 SMI Format (53)

Table 10 DC Characteristics (56)

Table 11 I/O Electrical Characteristics (56)

Table 12 Pin Latched-in Configuration Resistor (57)

Table 13 Crystal Specifications (57)

Table 14 Reset, Pin Latched-in, Clock and Power Source Timing Requirements (58)

Table 15 MII Transmit Timing Requirements (59)

Table 16 MII Receive Timing Specifications (59)

Table 17 RMII Transmit Timing Requirements (60)

Table 18 RMII Receive Timing Specifications (60)

Table 19 SMI Timing Requirements (61)

Table 20 Thermal Data (61)

Table 21 Part Number and Package (62)

Revision History

Revision # Change Description

IP101G-DS-R01 Initial release.

IP101G-DS-R01-20120622 Add 30 seconds into the definition for register WOL_PLUS_TIMER_SEL.

IP101G-DS-R01-20120629 Add the symbol SC (Self Clear) for PHY MII register 0.15 Reset and 0.9

Restart Auto-Negotiation.

IP101G-DS-R01-20120709 1) Add LED mode 2 in the pin description and function description.

2) Correct the table of LED Blink Timing.

3) Add more description of PHY Address Configuration and IEEE 802.3az.

4) Add ESD reliability of Absolute Maximum Rating.

5) Correct the typo of function description for Auto Power Saving Mode.

6) Change register P16R16[10] description from HEART_BEAT_EN to

Reserved.

IP101G-DS-R01-20120719 Correct the table of Register Map for page selection.

IP101G-DS-R01-20120726 1) Add more description of Register RX2TX_LPBK P1R23[13] for Rx to Tx

loopback test.

2) Add more description on Fiber Mode Setting and latched-in pin signals

on AC Timing.

3) Add IP101AH into the table of features comparison.

IP101G-DS-R01-20120808 1) Correct the I/O type of IP101GA pin description to O(Ouput) for pin24

RXER.

2) Change the pin name from DVDD33_IO to VDDIO.

IP101G-DS-R01-20120821 1) Change the default value of register P16R27 from 0x0022 to 0x0012.

2) Remove I/O Slew Rate Control Register.

3) Change the register location RMII_WITH_ER from P16R29[0] to

P16R29[7].

IP101G-DS-R01-20120927 1) Add more description of low power idle (LPI) state in MII and RMII

modes.

2) Correct the typo of Physical Dimensions.

IP101G-DS-R01-20121101 Change the LED blink timing from “On 80ms -> Off (20~40)ms” to “On 26ms

-> Off 78ms”.

IP101G-DS-R01-20121113 Add more function description to support Jumbo Frame.

IP101G-DS-R01-20121127 Change the LED mode function as same as IP101A.

IP101G-DS-R01-20121224 Add the notice that does not let these PHY address pins floating for the

latched-in settings after the power is ready.

IP101G-DS-R01-20130206 Change the AC timing Tclk_MII_rdy in Table 14 from 10ms Min. to 10ms Max. IP101G-DS-R01-20130312 1) Add more Min. and Max value on the AC Timing table.

2) Add thermal data on the Table 20.

IP101G-DS-R01-20130507 Add LED Pin Driving Control Register

IP101G-DS-R01-20130621 Add GRI 2.5V I/O power supply

Disclaimer

This document probably contains the inaccurate data or typographic error. In order to keep this document correct, IC Plus reserves the right to change or improve the content of this document.

Features comparison between IP101G and IP101A/IP101AH

Table 1 Features comparison between IP101G and IP101A/IP101AH

Product Name IP101GR IP101G IP101GA IP101A IP101AH Package Type 32pin QFN Dice 48pin LQFP48pin LQFP

REGOUT(1) Output Voltage and location 1.0V, pin28 1.0V, pad5

and pad11

1.0V, pin8

2.5V, pin32

REGIN Input Voltage and location NA(2) 1.0V,

pad23

and pad26

NA 2.5V,

pin8

RMII mode setting Pin4 Pad18 Pin1 Pin1 and pin44

Fiber mode setting: Fiber FXSD signal: Pin19

Pin1

Pad39

Pad13

Pin22

Pin43

NA Pin24 and pin48

Pin37

Number of LED 2 4 4 5

LED mode 1 and 2 1 and 2

LED Blink Timing On 26ms -> Off 78ms On 26ms -> Off 78ms

PHY address number(3) Single: 0 ~ 1

Multi: 2 ~ 31Single: 0 ~ 7

Multi: 8 ~ 31

Single: 0 ~ 31

Center-tap of transformer Do not connect to any power 2.5V input power

Built-in 49.9ohm resistors Yes No

Power

consumption ~150mW ~480mW Process 85nm

0.25μm

IEEE 802.3az Yes No

10Base TX amplitude ~1.75V (10Base-Te) ~2.5V

(10Base-T) WOL+ (Wake On LAN Plus) Yes No

Analog OFF Yes No

16 bit RX counter Yes No

9 bit RXER/CRC counter Yes No

RX to TX Loopback Yes No

Loopback MII/RMII Yes Yes

SNI mode No Yes

Note 1: Regulator voltage output is for internal use only. Do not supply to any other device.

Note 2: Not available for this function. The 1.0V is supplied by the regulator that built-in the chip.

Note 3: Do not let these PHY address pins floating for the latched-in settings after the power is ready.

Transmit and Receive Data Path Block Diagram

Figure 1 Flow chart of IP101G

1

Pin diagram

RXER CRS/LEDMOD

RXDV/CRS_DV/FX_HEN X1X2RXD2

RXD3RXCLK/50M_CLKO DGND

RXD0

NC

RESET_N IP101GA (LQFP-48)

2423222120

19181716

NC NC TXER/FXSD

NC Those pins in "blue "are different from IP101A.

NC Note:

RXD1INTR

NC DGND

NC LED3/PHY_AD3

VDDIO

Figure 2 IP101GA 48 Pin Diagram

IP101GR/GRI

(VQFN-32)

(GND on bottom of chip)

RXD3

TXCLK/50M_CLKI RXCLK/50M_CLKO LED0/PHY_AD0LED3/PHY_AD3161514131211109

RESET_N

ISET REGOUT MDI_TN MDI_TP MDI_RP MDI_RN RXD2AVDD33

Figure 3 IP101GR/GRI 32 Pin Diagram

2

Dice pad information

IC Logo

Pad 1Pad 44

Pad 11

Pad 45

Pad 24Pad 31

Pad 12

Pad 22

Pad 23

REGIN

PHYAD_LED028PHYAD_LED129VSS

30PHYAD_LED231PHYAD_LED332VDDIO 33RX_CLK REGOUT 34VSSIO RESET_N 35RXD[3]TXER_FXSD 36RXD[2]VSSIO 37RXD[1]15X138RXD[0]

16X239RXDV_FIBMOD 17INTR

40CRS

18COL_RMII 41RXER_INTR 19TX_EN 4220TXD[3]21TXD[2]22TXD[1]23

REGIN

Figure 4 IP101G dice pad information

3 Pin description

Type Description

Type Description

LI Latched Input in power up or reset PD Internal Pull-Down 104K ? I/O

Bi-directional input and output

PU

Internal Pull-Up 222K ?

I Input Hi-Z High impedance

O Output P Power OD Open Drain

3.1 IP101GA pin description

IP101GA

Pin no. Label

Type Reset State

Description

Serial Management Interface Pins 25 MDC I Hi-Z Management Data Interface Clock: This pin provides a

clock reference to MDIO. The clock rate can be up to 2.5MHz.

26 MDIO I/O (PU) I (PU)Management Data interface Input/Output:The

function of this pin is to transfer management information

between PHY and MAC.

MII/RMII Pins

2 TXEN I (PD) I (PD)

Transmit Enable or Signal Detect.

43 TXER/FXSD I (PD) I (PD)Transmit Error or FXSD:

This is a dual-function pin which is determined by the

media type selection. If RXDV/CRS_DV/FX_HEN is

latched as “0 (default)” upon reset, the TP interface is

selected and its function as TXER. If the fiber interface is selected, this pin’s function as FXSD.

FXSD:

0: Fiber link down; 1: Fiber link up

Transmit Enable:

TXEN TXER Description 1 1 Transmission error

propagation.

0 1 Combine TXD[3:0] that equal

to 0001 for request PHY to enter LPI mode.

1 0 0 0

Normal operation

This pin TXER must be either floating or connecting to GND in RMII mode.

7 TXCLK/50M_CLKI I/O Hi-Z Transmit Clock output or 50M clock input:

In MII mode, this pin provides a continuous 25MHz clock at 100Base-TX and 2.5MHz at 10Base-T .

In RMII mode, a 50Mhz clock should input to this pin for the timing reference of the internal circuit.

3,4,5,6 TXD[3:0] I Hi-Z Transmit Data Input:

IP101GA

Pin no.

Label

Type Reset

Description

State

In MII mode, TXD[3:0] is synchronous to TXCLK.

In RMII mode, TXD[1:0] is synchronous to 50M_CLKI.

22 RXDV/CRS_DV/ FX_HEN O/LI (PD) I (PD)Receive Data Valid or Media Type Selection:

FX_HEN

The input state is latched upon reset to determine whether TP or fiber interface is selected. If it is at logic “0” (default) state upon reset, the TP interface is selected; otherwise the fiber interface is selected. RXDV/CRS_DV

In MII mode, this pin indicates the Receive Data Valid function.

In RMII mode, this pin indicates the Carrier Sense and Receive Data Valid function.

16 RXCLK/ 50M_CLKO O Hi-Z Receive Clock:

In MII mode, this pin provides 25MHz for 100BT or

2.5MHz for 10BT.

In RMII mode, this pin output a 50 MHz clock for the timing reference of MAC side.

18,19, 20,21 RXD[3:0] O Hi-Z Receive Data: In MII mode, RXD[3:0] is synchronous to RXCLK.

In RMII mode, RXD[1:0] is synchronous to 50M_CLKI.

24 RXER O Hi-Z Receive error:

RXDV RXER Description

1 1 Decoding error of the

received signal

0 1 Combine RXD[3:0] equal to

0001 indicates PHY is

receiving LPI.

1 0 0 0

Normal operation

This pin RXER is an optional input for MAC/CPU device.

1 COL/RMII O/LI (PD) I (PD)Collision Detected:During the normal operation, this

pin outputs a high status signal it means collision is

detected.

RMII Mode Selection: During the power on reset, this

pin status is latched to determine what kind MAC interface will be used. Logic “1” is for RMII mode and logic “0” is for MII mode.

23 CRS/LEDMOD O/LI (PD) I (PD)Carrier Sense: When signal output from this pin is high

indicates the transmission or reception is in process and

at low status means the line is in idle state.

LEDMOD: During power on reset, this pin status is latched to determine which either LED mode 1 or 2is selected, please refer to the LED pins description.

Cable Transmission Interface 34,33 MDI_TP MDI_TN I/O I/O Hi-Z Transmit Output Pair: Differential pair shared by

100Base-TX and 10Base-T modes. When configured as

100Base-TX, output is an MLT-3 encoded waveform. When configured as 10Base-T , the output is Manchester

IP101GA

Pin no. Label Type Reset Description

State

code.

31,30 MDI_RP

MDI_RN I/O

I/O

Hi-Z Receive Input Pair: Differential pair shared by 100Base-TX and 10Base-T modes.

Clock and Miscellaneous Pins

47 X2 O O 25MHz Crystal Output: Connects to crystal to provide

the 25MHz output. It must be left open when X1 is driven

with an external 25MHz oscillator.

46 X1 I I 25MHz Crystal Input: Connects to crystal to provide the

25MHz crystal input. If a 25MHz oscillator is used,

connect X1 to the oscillator’s output. If a 50MHz clock is

applied to pin7 TXCLK/50M_CLKI, X1 must be

connected to GND or AGND33.

42 RESET_N I I

(PU)RESET_N: Enable a low status signal will reset the chip. For a complete reset function. 25MHz clock (x1) must be active for a minimum of 10 clock cycles before the rising edge of RESET_N. Chip will be able to operate after 2.5ms delay of the rising edge of RESET_N. The 2.5ms extension is to ensure the stability of system power.

28 ISET I I Bandgap Circuit Resistor: This pin should be

connected to GND via a 6.19K? (1%) resistor to define

the standard current of the internal circuit.

48 INTR OD Hi-Z Interrupt: Programmable Interrupt Output, this is an

open drain output, and an external pulled-up resistor is

needed for normal mode operation. Another operation

mode is Rx to Tx loopback debugging test (reflect on

Register P1R23[13] RX2TX_LPBK) when connect INTR

pin to GND.

9 LED0/PHY_AD0 O/LI Hi-Z LED 0 and PHY Address [0]

LED 0

LED mode

1 2

LED0Link Link

/ACT(blinking)

10 LED1/PHY_AD1 O/LI Hi-Z LED 1 and PHY Address [1]

LED1

LED mode

1 2

LED1Duplex Duplex /COL (blinking)

12 LED2/PHY_AD2 O/LI Hi-Z LED 2 and PHY Address [2]

LED2

LED mode

1 2

LED210M Link /ACT10M Link

13 LED3/PHY_AD3 O/LI

(PD) Hi-Z LED 3 and PHY Address [3]

LED3

LED mode

1 2

LED3100M Link /ACT 100M Link

27 TEST_ON I I Test Enable: Set this pin to high to enable Test mode.

IP101GA

Pin no. Label Type Reset Description

State

(PD) (PD)For normal operation, this pin doesn’t need to be

connected.

Power and Ground

32 NC -- -- It’s a NC pin.

8 REGOUT P P Regulator Power Output: This is a regulator power

output. A 10uF and 0.1uF should be connected to this pin

to filter the power noise.

14 VDDIO P P Digital Power input:

Either 3.3V or 2.5V for I/O power supply.

36 AVDD33 P P 3.3V Analog power input: This is a 3.3V power supply

for analog circuitry, and it should be decoupled carefully.

35 AGND33 P P Ground.

29 AGND1V P P Ground

45,11,17 DGND P P Ground.

3.2 IP101GR/GRI pin description

IP101GR/GRI

Pin no. Label Type Reset

State

Description

Serial Management Interface Pins

22 MDC I Hi-Z Management Data Interface Clock: This pin provides a

clock reference to MDIO. The clock rate can be up to

2.5MHz.

23 MDIO I/O

(PU)

I

(PU)

Management Data interface Input/Output:The

function of this pin is to transfer management information

between PHY and MAC.

MII/RMII Pins

5 TXEN I

(PD)

I

(PD)

Transmit Enable or Signal Detect.

1 TXER/FXSD I

(PD)

I

(PD)

Transmit Error or FXSD:

This is a dual-function pin which is determined by the

media type selection. If RXDV/CRS_DV/FX_HEN is

latched as “0 (default)” upon reset, the TP interface is

selected and its function as TXER. If the fiber interface is

selected, this pin’s function as FXSD.

FXSD:

0: Fiber link down; 1: Fiber link up

Transmit Enable:

TXEN TXER Description

1 1 Transmission

error

propagation.

0 1 Combine

TXD[3:0]

that

equal

to 0001 for request PHY to

enter LPI mode.

1 0

0 0

Normal operation

This pin TXER must be either floating or connecting to

GND in RMII mode.

10 TXCLK/50M_CLKI I/O Hi-Z Transmit Clock output or 50M clock input:

In MII mode,this pin provides a continuous 25MHz clock

at 100Base-TX and 2.5MHz at 10Base-T.

In RMII mode, a 50Mhz clock should input to this pin for

the timing reference of the internal circuit.

6,7,8,9 TXD[3:0] I Hi-Z Transmit Data Input:

In MII mode, TXD[3:0] is synchronous to TXCLK.

In RMII mode, TXD[1:0] is synchronous to 50M_CLKI.

19 RXDV/CRS_DV/

FX_HEN O/LI

(PD)

I

(PD)

Receive Data Valid or Media Type Selection:

FX_HEN

The input state is latched upon reset to determine

whether TP or fiber interface is selected. If it is at logic

“0” (default) state upon reset, the TP interface is

selected; otherwise the fiber interface is selected.

RXDV/CRS_DV

In MII mode, this pin indicates the Receive Data Valid

IP101GR/GRI

Pin no.

Label

Type Reset

Description

State

function.

In RMII mode, this pin indicates the Carrier Sense and Receive Data Valid function.

14 RXCLK/ 50M_CLKO O Hi-Z Receive Clock:

In MII mode, this pin provides 25MHz for 100BT or

2.5MHz for 10BT.

In RMII mode, this pin output a 50 MHz clock for the timing reference of MAC side.

15,16, 17,18 RXD[3:0] O Hi-Z Receive Data: In MII mode, RXD[3:0] is synchronous to RXCLK.

In RMII mode, RXD[1:0] is synchronous to 50M_CLKI.

21 RXER/INTR_32 O/OD

Hi-Z The multiplex function of this pin is set by the register

SEL_INTR32, page 16,29[2]. The default function is RXER.

Receive error:

RXDV RXER Description 1 1 Decoding error of the

received signal

0 1 Combine RXD[3:0] equal to

0001 indicates PHY is receiving LPI.

1 0 0 0

Normal operation

This pin RXER is an optional input for MAC/CPU device.Interrupt: Programmable Interrupt Output, this is an open drain output, and an external pulled-up resistor is needed.

4 COL/RMII O/LI (PD) I (PD)Collision Detected:During the normal operation, this

pin outputs a high status signal it means collision is

detected.

RMII Mode Selection: During the power on reset, this

pin status is latched to determine what kind MAC interface will be used. Logic “1” is for RMII mode and logic “0” is for MII mode.

20 CRS/LEDMOD O/LI (PD) I (PD)Carrier Sense:When signal output from this pin is high

indicates the transmission or reception is in process and

at low status means the line is in idle state.

LEDMOD: During power on reset, this pin status is latched to determine which either LED mode 1 or 2is selected, please refer to the LED pins description.

Cable Transmission Interface 30,29 MDI_TP MDI_TN I/O I/O Hi-Z Transmit Output Pair: Differential pair shared by

100Base-TX and 10Base-T modes. When configured as

100Base-TX, output is an MLT-3 encoded waveform. When configured as 10Base-T , the output is Manchester code.

27,26 MDI_RP MDI_RN I/O I/O Hi-Z Receive Input Pair: Differential pair shared by

100Base-TX and 10Base-T modes.

Clock and Miscellaneous Pins

IP101GR/GRI

Pin no. Label Type Reset Description

State

3 X2 O O 25MHz Crystal Output: Connects to crystal to provide

the 25MHz output. It must be left open when X1 is driven

with an external 25MHz oscillator.

2 X1 I I 25MHz Crystal Input: Connects to crystal to provide the

25MHz crystal input. If a 25MHz oscillator is used,

connect X1 to the oscillator’s output. If a 50MHz clock is

applied to pin10 TXCLK/50M_CLKI, X1 must be

connected to GND.

32 RESET_N I I

(PU)RESET_N: Enable a low status signal will reset the chip. For a complete reset function. 25MHz clock (x1) must be active for a minimum of 10 clock cycles before the rising edge of RESET_N. Chip will be able to operate after 2.5ms delay of the rising edge of RESET_N. The 2.5ms extension is to ensure the stability of system power.

25 ISET I I Bandgap Circuit Resistor: This pin should be

connected to GND via a 6.19K? (1%) resistor to define

the standard current of the internal circuit.

11 LED0/PHY_AD0 O/LI Hi-Z LED 0 and PHY Address [0]

LED 0

LED mode

1 2

LED0Link Link

/ACT(blinking)

12 LED3/PHY_AD3 O/LI

(PD) Hi-Z LED 3 and PHY Address [3]

LED3

LED mode

1 2

LED3100M Link /ACT 100M Link

24 TEST_ON I

(PD)

I

(PD)

Test Enable: Set this pin to high to enable Test mode.

For normal operation, this pin doesn’t need to be

connected.

Power and Ground

28 REGOUT P P Regulator Power Output: This is a regulator power

output. A 10uF and 0.1uF should be connected to this pin

to filter the power noise.

13 VDDIO P P Digital Power input:

IP101GR/GRI: Either 3.3V or 2.5V for I/O power supply.

31 AVDD33 P P 3.3V Analog power input: This is a 3.3V power supply

for analog circuitry, and it should be decoupled carefully.

Bottom PAD GND P

P

Ground.

4 Register Descriptions

Table 2 Register Map

Page Register Description Default Note

Register 0x0010

X 20 Page

Control

Register 0x3100

-- 0 Control

Register 0x7849

-- 1 Status

-- 2 PHY Identifier 1 Register 0x0243

-- 3 PHY Identifier 2 Register 0x0C54

Advertisement Register 0x01E1

-- 4 Auto-Negotiation

-- 5 Auto-Negotiation Link Partner Ability Register 0x0000

-- 6 Auto-Negotiation Expansion Register 0x0004

-- 7 Auto-Negotiation Next Page Transmit Register 0x2001

-- 8 Auto-Negotiation Link Partner Next Page Register 0x0000

-- 13 MMD Access Control Register 0x0000

-- 14 MMD Access Address Data Register 0x0000

16 16 PHY Specific Control Register 0x0002

16 17 PHY Interrupt Ctrl/Status Register 0x0F00

16 18 PHY Status Monitoring Register 0x0208

16 26 Digital IO Pin Driving Control Register 0x1249

16 27 Digital IO Pin Driving Control Register 0x0012

16 28 LED Pin Driving Control Register 0x0001

16 29 Digital I/O Specific Control Register 0x0082

16 30 PHY MDI/MDIX Control and Specific Status Register 0x0000

-- MMD 3.0 PCS Control 1 Register 0x0000

-- MMD 3.1 PCS Status 1 Register 0x0000

-- MMD 3.20 EEE Capability Register 0x0002

-- MMD 3.22 EEE Wake Error Count Register 0x0000

-- MMD 7.60 EEE Advertisement Register 0x0002

-- MMD 7.61 EEE Link Partner Ability Register 0x0000

1 17 PHY Specific Control Register 0x0000

1 18 RX CRC Error Counter Register 0x0000

1 2

2 Linear Regulator Output Control Register 0x2020

1 23 UTP PHY Specific Control Register 0x8000

2 18 RX Packet Counter Register 0x0000

3 16 LED Mode Control Register 0x0000

4 16 WOL+ Control Register 0x5F40

4 22 Digital IO Pin Driving Control Register 0x4000

5 1

6 PHY WOL+ MAC Address Register 0x0000

8 17 RX Counter Control Register 0x7000

Page Register Description

Default Note 11 18 UTP PHY Interrupt Control/Status Register 0x0000 17 17 PHY WOL+ Status Register

0x0000 18

17

RX Counter Interrupt Control/Status Register

0x0000

Register descriptions

R/W = Read/Write, SC = Self-Clearing, RO = Read Only, LL = Latching Low, LH = Latching High (TP): for twisted pair operation. (FX): for fiber operation. (e-fuse): only available for IP101G (dice).

4.1 Register Page mode Control Register

MII register 20 PHY

MII

ROM

R/W

Description

Default

Page Control Register -- 20[4:0] -- R/W Reg16~31_Page_Sel[4:0] Register Page Select

0x10

The other Registers are reserved registers. User is inhibited to access to these registers. It may introduce abnormal function to write these registers.

4.2 MII Registers

Bit

Name

Description/Usage

Default value (h): 3100

Register 0 : Control Register 15 Reset

When set, this action will bring both status and control registers of the PHY to default state. This bit is self-clearing. 1 = Software reset 0 = Normal operation

0, RW/SC 14 Loopback

This bit enables loopback of transmit data to the receive data path, i.e., TXD to RXD. 1 = enable loopback 0 = normal operation

0, RW 13 Speed Selection

This bit sets the speed of transmission. 1 = 100Mbps 0 = 10Mbps

After completing auto-negotiation, this bit will reflect the speed status.(1: 100Mbps, 0: 10Mbps)

1, RW 12 Auto-

Negotiation Enable This bit determines the auto-negotiation function. 1 = enable auto-negotiation; bits 13 and 8 will be ignored. 0 = disable auto-negotiation; bits 13 and 8 will determine the link speed and the data transfer mode, under this condition.

1, RW (TP) 0, RO (FX) 11 Power Down

This bit will turn down the power of the PHY chip and the internal crystal oscillator circuit if this bit is enabled. The MDC and MDIO are still activated for accessing to the MAC. 1 = power down

0 = normal operation

0, RW 10 Isolate

1=electrically Isolate PHY from MII but not isolate MDC and 0,RW

中控考勤机详细操作说明书

中控考勤机说明书 1考勤机的使用 1.1登记指纹 1.2考勤机功能介绍(通讯,参数设置,系统信息,U盘管理) 2考勤软件的使用 2.1 软件的安装 2.2 软件使用 2.2.1 增加设备 2.2.2 从设备下载人员信息 2.2.3 修改人员信息(改名字,调动部门等) 2.2.4 上传人员信息到设备 2.2.5 下载考勤数据 2.2.6 时间段设置 2.2.7 班次管理 2.2.8 人员排班 2.2.9 统计报表 一考勤机快速使用 1.1登记指纹(分彩屏跟黑白屏) 从设备上采集指纹: (1)彩屏:长按M/OK键--“用户管理”点OK--“新增用户”点OK--选择工号,- 往下翻在“指纹登记”上点OK,同一个手指按三次,完成后再点击OK键,再放上另一个手指按三次--往下翻到完成上点OK。(如果要再登记指纹可在‘用户管理‘点OK--’管理用户‘点M/OK---点M/OK选择’---- 查找用户‘—输入工号点OK—点M/OK选择“编辑用户”然后选择登记指纹,登记完成后---往下翻到完成上点M/OK。 (2)黑白屏录指纹的跟彩屏类似就不再说了。录备用指纹的话跟彩

屏有点区别:按M/OK—用户登记—指纹登记—提示新登记—按ESC键—跳出备份登记—输入工号—登记指纹。。 1.2机器的功能介绍 (1)通讯设置—设置通讯方式有RS232/485通讯,TCP/IP,USB 通讯 (2)系统设置—参数设置(包含提示声音,键盘声音,时间设置算法切换(高端机器如iclock360, S20等)--数据维护(删除考勤机上的记录数据【记录要定时去删除】,清除管理权限【管理员破解】,清除全部数据----恢复设置(恢复出厂设置【不会删除考勤机上的数据只是恢复机器出厂的通讯设置等】; (3)系统信息—可以查看设备的人员登记数跟指纹数及考勤记录数-------设备信息可以查看设备的序列号、算法版本、MAC地址、出厂时间等。 (4)U盘功能(包含下载跟上传的功能) <1>(1)把U盘插到考勤机上--长按M/OK键进入菜单--选择U盘管理--下载数据--下载用户数据--下载完成后退出然后把U盘拿下来插到电脑上。 <2> (1)打开考勤软件--点击软件最左上角数据--选择菜单里“USB闪盘管理”,然后选择菜单里对应的选项(黑白屏机器选择第一项,彩屏机器选择第三项)--在对话框的左上角第一栏“导入用户数据到电脑”上点击--最后再点击“从U盘导入用户数据”--导入完成后关闭。

光纤收发器原理技术详解

光纤收发器原理技术详解 1 光纤收发器原理技术详解 本文详细对光纤收发器原理进行讲解,分析了光纤收发器的发展趋势以及如何采购光纤收发器,下面进行阐述: 首先什么是光纤收发器 光纤收发器是一种将短距离的双绞线电信号和长距离的光信号进行互换的以太网传输媒体转换单元,在很多地方也被称之为光电转换器。企业在进行信息化基础建设时,通常更多地关注路由器、交换机乃至网卡等用于节点数据交换的网络设备,却往往忽略介质转换这种非网络核心但必不可少的设备。特别是在一些要求信息化程度高、数据流量较大的政府机构和企业,网络建设时需要直接上连到以光纤为传输介质的骨干网,而企业内部局域网的传输介质一般为铜线,确保数据包在不同网络间顺畅传输的介质转换设备成为必需品。 目前国外和国内生产光纤收发器的厂商很多,产品线也极为丰富。为了保证与其他厂家的网卡、中继器、集线器和交换机等网络设备的完全兼容,光纤收发器产品必须严格符合IEEE802.3太网标准,除此之外,在EMC防电磁辐射方面应符合FCC及CE 的相关规定,如烽火网络公司的光纤收发器已经通过FCC及CE认证。时下由于国内各大运营商正在大力建设小区网、校园网和企业网,因此光纤收发器产品的用量也在不断提高,以更好地满足接入网的建设需 随着信息化建设的突飞猛进,人们对于数据、语音、图像等多媒体通信的需求日益旺盛,以太网宽带接入方式因此被提到了越来越重要的位置。但是传统的5类线电缆只能将以太网电信号传输100米,在传输距离和覆盖范围方面已不能适应实际网络环境的需要。与此同时,光纤通信以其信息容量大、保密性好、重量轻、体积小、无中继、传输距离长等优点在广域网等大型网络中得到了广泛的应用。 在一些规模较大的企业,网络建设时直接使用光纤为传输介质建立骨干网,而内部局域网的传输介质一般为铜线,如何实现局域网同光纤主干网相连呢?这就需要在不同端口、不同线形、不同光纤间进行转换并保证链接质量。 光纤收发器的出现,将双绞线电信号和光信号进行相互转换,确保了数据包在两个网

中控考勤机详细操作说明书

中控考勤机说明书1考勤机的使用 1.1登记指纹 1.2考勤机功能介绍(通讯,参数设置,系统信息,U盘管理) 2考勤软件的使用 2.1 软件的安装 2.2 软件使用 2.2.1 增加设备 2.2.2 从设备下载人员信息 2.2.3 修改人员信息(改名字,调动部门等) 2.2.4 上传人员信息到设备 2.2.5 下载考勤数据 2.2.6 时间段设置 2.2.7 班次管理 2.2.8 人员排班 2.2.9 统计报表 一考勤机快速使用 1.1登记指纹(分彩屏跟黑白屏) 从设备上采集指纹: ??? (1)彩屏:长按M/OK键--“用户管理”点OK--“新增用户”点OK--选择工号,- 往下翻在“指纹登记”上点OK,同一个手指按三次,完成后再点击OK键,

再放上另一个手指按三次--往下翻到完成上点OK。(如果要再登记指纹可在‘用户管理‘点OK--’管理用户‘点M/OK---点M/OK选择’---- 查找用户‘—输入工号点OK—点M/OK选择“编辑用户”然后选择登记指纹,登记完成后---往下翻到完成上点M/OK。 (2)黑白屏录指纹的跟彩屏类似就不再说了。录备用指纹的话跟彩屏有点区别:按M/OK—用户登记—指纹登记—提示新登记—按ESC键—跳出备份登记—输入工号—登记指纹。。 1.2机器的功能介绍 (1)通讯设置—设置通讯方式有RS232/485通讯,TCP/IP,USB通讯(2)系统设置—参数设置(包含提示声音,键盘声音,时间设置算法切换(高端机器如iclock360, S20等)--数据维护(删除考勤机上的记录数据【记录要定时去删除】,清除管理权限【管理员破解】,清除全部数据----恢复设置(恢复出厂设置【不会删除考勤机上的数据只是恢复机器出厂的通讯设置等】;(3)系统信息—可以查看设备的人员登记数跟指纹数及考勤记录数-------设备信息可以查看设备的序列号、算法版本、MAC地址、出厂时间等。(4)U盘功能(包含下载跟上传的功能) <1>(1)把U盘插到考勤机上--长按M/OK键进入菜单--选择U盘管理--下载数据--下载用户数据--下载完成后退出然后把U盘拿下来插到电脑上。 <2> (1)打开考勤软件--点击软件最左上角数据--选择菜单里“USB闪盘管理”,然后选择菜单里对应的选项(黑白屏机器选择第一项,彩屏机器选择第三项)--在对话框的左上角第一栏“导入用户数据到电脑”上点击--最后再点击“从U盘导入用户数据”--导入完成后关闭。

以太网光纤收发器的故障案例及设置经验交流

以太网光纤收发器的故障案例及设置经验交流太网光纤收发器因它的维护方便、低成本等优势越来越多的用到杭州电信网客户末端,光纤收发器由于是末端的低端设备,维护人员往往会忽略它的设置。本文通过分析近期由于光纤收发器设置不当造成的故障案例,来提醒维护及施工人员重视以太网光纤收发器的设置。希望通过本文和各位维护人员交流,提出简洁、实用的设置规范。 例1:某用户申请了34M带宽的长途电路,业务运行一段时间后,用户申告带宽不足。 此电路为MSTP电路,维护人员检查了大通道上的带宽设置,时隙绑定等参数,没发现问题。用仪表到客户用户转接局测试结果也是34M,用户还是称带宽不足。末端用的艾赛VX230光纤收发器由于是光口,没有用仪表测试。 检查光纤收发器的设置: 光纤收发器转接局设置为自适应,末端设置为强制。 两端光纤收发器速率设置了10Mbps。 修改两端光纤收发器的设置,两端都设置成:强制100Mbps全双工后,用户称带宽正常。 例2:某客户申告电路有丢包。 检查光纤收发器的设置:为半双工模式引起用户设备PING有大量丢包。 修改两端光纤收发器的设置,两端都设置成:强制100Mbps全双工后,用户设备PING包正常。 以上案例说明:任何两个直连的以太网端口间都存在端口速率与双工模式的适配要求,非正常配置将导致通信故障。 故障现象为: 1.带宽不足。 2.有丢包或时延过大现象。 3.有短暂网络通信中断等故障现象。 以太网光纤收发器的设置建议及注意事项: 1.两端电口设置为同样的速率和双工模式(100M/全双工),以保证匹配良 好。

2.电口强制模式建议优先设置成“强制”模式,这种工作模式能和绝大部分 对接设备良好匹配。个别出现链路起不来现象时,检查对接设备的工作模式(包括用户设备),建议本设备设置为与对接设备同样工作模式,以保证匹配良好。 3.特别注意:状态变更后,必须重新上电设置方能生效。 4.设置完毕后,最后检查:自局端交换机至用户交换机(路由器)链路上的 所有以太网端口都以双工模式工作于用户租用的数据速率上,确保用户的带宽及通信质量。 以上仅供维护人员交流,各维护人员在实际应用中有不同现象,或不同的处理方式,往及时交流、探讨。

MEMORY存储芯片STM32F103C8T6中文规格书

Features ?ARM? 32-bit Cortex?-M3 CPU Core –72 MHz maximum frequency, 1.25 DMIPS/MHz (Dhrystone 2.1) performance at 0 wait state memory access –Single-cycle multiplication and hardware division ?Memories –64 or 128 Kbytes of Flash memory –20 Kbytes of SRAM ?Clock, reset and supply management – 2.0 to 3.6 V application supply and I/Os –POR, PDR, and programmable voltage detector (PVD) –4-to-16 MHz crystal oscillator –Internal 8 MHz factory-trimmed RC –Internal 40 kHz RC –PLL for CPU clock –32 kHz oscillator for RTC with calibration ?Low-power –Sleep, Stop and Standby modes –V BAT supply for RTC and backup registers ? 2 x 12-bit, 1 μs A/D converters (up to 16 channels) –Conversion range: 0 to 3.6 V –Dual-sample and hold capability –Temperature sensor ?DMA –7-channel DMA controller –Peripherals supported: timers, ADC, SPIs, I2Cs and USARTs ?Up to 80 fast I/O ports –26/37/51/80 I/Os, all mappable on 16 external interrupt vectors and almost all 5 V-tolerant ?Debug mode –Serial wire debug (SWD) & JTAG interfaces ?7 timers –Three 16-bit timers, each with up to 4 IC/OC/PWM or pulse counter and quadrature (incremental) encoder input –16-bit, motor control PWM timer with dead-time generation and emergency stop – 2 watchdog timers (Independent and Window) –SysTick timer 24-bit downcounter ?Up to 9 communication interfaces –Up to 2 x I2C interfaces (SMBus/PMBus) –Up to 3 USARTs (ISO 7816 interface, LIN, IrDA capability, modem control) –Up to 2 SPIs (18 Mbit/s) –CAN interface (2.0B Active) –USB 2.0 full-speed interface ?CRC calculation unit, 96-bit unique ID ?Packages are ECOPACK? Table 1. Device summary Reference Part number STM32F103x8 STM32F103C8, STM32F103R8 STM32F103V8, STM32F103T8 STM32F103xB STM32F103RB STM32F103VB, STM32F103CB, STM32F103TB 找Memory、FPGA、二三极管、连接器、模块、光耦、电容电阻、单片机、处理器、晶振、传感器、滤波器, 上深圳市美光存储技术有限公司 August 2015

光纤收发器基本连接方式

光纤收发器基本连接方式 光纤收发器是一种将短距离的双绞线电信号和长距离的光信号进行互换的以太网传输媒体转换单元,在很多地方也被称之为光电转换器。产品一般应用在以太网电缆无法覆盖、必须使用光纤来延长传输距离的实际网络环境中,且通常定位于宽带城域网的接入层应用。 在传统的以太网中起连接作用的介质主要是双绞线。双绞线传输距离的极限大约为200米左右,如此短的传输距离制约了网络的发展,同时双绞线受电磁干扰的影响较大,这也无疑使数据通讯质量受到较大的影响。光纤收发器的运用,将以太网中的连接介质换为光纤。光纤的低损耗、高抗电磁干扰性,在使网络传输距离从200米扩展到2公里甚至几十公里,乃至于上百公里的同时,也使数据通讯质量有了较大提高。他使服务器、中继器、集线器、终端机与终端机之间的互联更加简捷。 在实际的应用中,光纤收发器主要有下面三种基本连接方式: 一、环形骨干网 环形骨干网是利用SPANNING TREE特性构建城域范围内的骨干,这种结构可以变形为网状结构,适合于城域网上高密度的中心小区,形成容错的核心骨干网络。环形骨干网对IEEE.1Q 及ISL网络特性的支持,可以保证兼容诰 蠖嗍 髁鞯墓歉赏 纾 缈缃换换 腣LAN、TRUNK 等功能。环形骨干网可为金融、政府、教育等行业组建宽带虚拟专网。

二、链形骨干网 链形骨干网利用链形的联接可以节省大量的骨干光线数量,适合于在城市的边缘及所属郊县地区构造高带宽低价位的骨干网络,该模式同时可用于高速公路、输油、输电线路等环境。链形骨干网对IEEE802.1Q及ISL网络特性的支持,可以保证兼容于绝大多数的骨干网络,可为金融、政府、教育等行业组建宽带虚拟专网。链形骨干网是可以提供图像、语音、数据及实时监控综合传输的多媒体网络。 三、用户接入系统 用户接入系统利用10Mbps/100Mbps自适应及10Mbps/100Mbps自动转换功能,可以联接任意的用户端设备,无需准备多种光纤收发器,可为网络提供平滑的升级方案。同时利用半双工/全双工自适应及半双工/全双工自动转换功能,可以在用户端配置廉价的半双工HUB,几十倍的降低用户端的组网成本,提高网络运营商的竞争力。同时,设备内置的交换核心提高接入设备的传输效率,减少网络广播、控制流量、检测传输故障。 相信看过这篇文章之后,大家对光纤收发器工作时候的连接方式有大概的了解了吧,如果还有什么问题,欢迎大家到论坛里来讨论。

光纤收发器的参数(精)

10/100M 自适应以太网光纤收发器,采用最新美国 KENDIN 芯片,高品质光收发一体模块,性能稳定,质量优良。适用于电信、广电、宽带网络等需要高性能、高可靠性的网络及一般光纤网络环境中。 ? 1个RJ45 电口和1个SC/ST/FC 光口,实现双绞线和光纤之间的光电信号转换。 ? 符合 IEEE802.3 10Base-T 和 IEEE802.3u 100Base-TX , 100Base-FX 标准。 ? 具有 10M/100M 自适应能力。 ? 电口能自适应直通线 / 交叉线连接方式。 ? 支持全双工 / 半双工工作模式。 ? 支持 IEEE802.3X 全双工流量控制和半双工背压流量控制。 ? 支持最大 1916 Bytes 数据幀。 ? 支持防止广播风暴功能。 ? 内置防雷电路,可大大减少雷电感应造成的损坏。 ? 双绞线最长 100 米 , 多模光纤最长 2 或 5 公里 ( 全双工 , 单模光纤最长 120 公里。 ? 有 6 个 LED 指示灯: Power , TX 100 , TX Link/Act , FX 100 , FX Link/Act , FDX/Col ;便于监测收发器的工作状态和判断故障原因。 ? 有外置、内置电源两种类型: AC100 ~ 265V / DC5V 开关电源。 ? 工作环境温度: 0 ~ 50 ℃。 ? 储存环境温度: - 40 ~ 70 ℃。

? 收发器尺寸:电源外置式 70×26×93mm ;内置式120×30×140mm 。 光纤部分参数: 型号光纤接口发射波长发射功率接收灵敏度传输距离允许损耗 HTB-1100 多模ST/SC 850/1310nm -20~-12dBm -30dBm 2km 10dBm HTB-1100-5 多模ST/SC 850/1310nm -12~-6dBm -32dBm 5km 20dBm HTB-1100S-10 单模SC 1310nm -22~-14dBm -31dBm 10km 9dBm HTB-1100S-25 单模ST/SC 1310nm -14~-8dBm -32dBm 25km 18dBm HTB-1100S-40 单模SC 1310nm -8~-3dBm -33dBm 40km 25dBm HTB-1100S-60 单模SC 1310nm -3~0dBm -38dBm 60km 35dBm HTB-1100S-80 单模SC 1550nm -8~-3dBm -35dBm 80km 27dBm HTB-1100S-100单模SC 1550nm -5~0dBm -36dBm 100km 31dBm HTB-1100S-120单模SC 1550nm -3~3dBm -38dBm 120km 35dBm 定货信息产品型号产品描述 HTB-1100 10/100M 自适应以太网多模光纤收发器,光纤接口有 ST 和 SC 两种;光波长有 850 、 1310nm 两种,光纤最大距离有 2KM 和 5KM 两种。 HTB-1100S-xx(公里) 10/100M 自适应以太网单模光纤收发器,光纤接口有 ST 、 SC 、 FC 和 LC 等数种;光纤最大距离有 25 、 40 、 60 、 80 、 100 和 120KM 等款,型号中的 XX 为距离数。 60 公里及以下为 FP 激光器, 60 公里以上为 DFB 激光器。

中控考勤机详细操作说明书

中控考勤机详细操作说 明书 The manuscript was revised on the evening of 2021

中控考勤机说明书 1考勤机的使用 1.1登记指纹 1.2考勤机功能介绍(通讯,参数设置,系统信息,U盘管理) 2考勤软件的使用 软件的安装 软件使用 2.2.1 增加设备 2.2.2 从设备下载人员信息 2.2.3 修改人员信息(改名字,调动部门等) 2.2.4 上传人员信息到设备 2.2.5 下载考勤数据 2.2.6 时间段设置 2.2.7 班次管理 2.2.8 人员排班 2.2.9 统计报表 一考勤机快速使用 登记指纹(分彩屏跟黑白屏) 从设备上采集指纹: (1)彩屏:长按M/OK键--“用户管理”点OK--“新增用户”点OK--选择工号,- 往下翻成后再点击OK键,再放上另一个手指按三次--往下翻到完成上点OK。(如果要再登记点M/OK选择’---- 查找用户‘—输入工号点OK—点M/OK选择“编辑用户”然后选择登(2)黑白屏录指纹的跟彩屏类似就不再说了。录备用指纹的话跟彩屏有点区别:ESC键—跳出备份登记—输入工号—登记指纹。。 机器的功能介绍 (1)通讯设置—设置通讯方式有RS232/485通讯,TCP/IP,USB通讯 (2)系统设置—参数设置(包含提示声音,键盘声音,时间设置算法切换(高端机上的记录数据【记录要定时去删除】,清除管理权限【管理员破解】,清除全部数据--数据只是恢复机器出厂的通讯设置等】; (3)系统信息—可以查看设备的人员登记数跟指纹数及考勤记录数-------设备信息可厂时间等。 (4)U盘功能(包含下载跟上传的功能) <1>(1)把U盘插到考勤机上--长按M/OK键进入菜单--选择U盘管理--下载数据--下插到电脑上。 <2> (1)打开考勤软件--点击软件最左上角数据--选择菜单里“USB闪盘管理”,然后选择

光纤收发器在网络组建过程中的使用

光纤收发器在网络组建过程中的使用? 一、多模光纤收发器、多模光纤 光纤收发器是一种将以太网的电信号和光信号进行互换的以太网传输媒质转换设备,而在网络上传输数据的光纤分为多模光纤和单模光纤,多模光纤的纤芯直径为50~62.5μm,包层外直径125μm,与相对应的单模光纤的纤芯直径为8.3μm,包层外直径125μm.但是这些技术数据对于我们来说不是很直观,其实要区别多模光纤与单模光纤,看颜色就可以。多模光纤的尾纤(即从是终端盒引出接光纤收发器那一段线路)的颜色是桔红色,如图1所示 图1 而单模光纤的尾纤的颜色为黄色,如图2所示: 图2

从组网应用上,由于多模光纤无法进行长距离的传输,一般只能用于楼宇内部及楼宇间的联网,但由于多模光纤及对应的光纤收发器比较便宜,所以还是在一定范围内得到了应用。比如祥子所在单位的办公大楼内综合布线采用的就是多模光纤,另外,很多学校组建内部的校园网时也是使用的多模光纤。 二、单模光纤收发器系列 随着技术的进步,单模光纤开始进入长距离的组网操作(从几公里至一百多公里),而且发展势头非常迅猛,没几年的时间,从就高端应用进入了寻常百姓家,从祥子所从事的工程来看,现在某些重点客户家里开通网络时都是直接使用的光纤收发器(所谓的FTTH模式,光纤到户),使用光纤收发器组网已经成为广电开展增值业务非常普遍的一种形式。下面介绍的各种型号的光纤收发器,都是基于单模光纤的。 (一)双纤单网口 所谓双纤单网口光纤收发器,就是利用两根光纤(一收一发),一组光纤收发器实现电信号至光信号、光信号再到电信号的转换,设备通常如图3所示: 图3 记得应该是2000年左右,当时这种设备还是一种高端设备,一对光纤收发器要几千元,但是能够实现长距离传输很神奇,而且相比电缆传输(MODEM拨号、DDN)有抗干扰能力强,信号质量好的特点,所以在开通业务时特别受用户的欢迎,当时听到用户对于光纤联网的肯定,我们作为工程技术人员心里也是美滋滋的。 这里的网络设备可能是交换机,也可能是服务器,那么光纤收发器输出的那根网线,究竟是直通线还是交叉线呢,这个问题当时可算是一个大问题,祥子每次都要翻阅说明书,查看说明书里面介绍的这款型号具体对于服务器还是交换机是直通线还是交叉线,但是后来随着组网经验的积累,发现了一个规律,那就是可以将光纤收发器当作一台PC机看,PC 机与交换机相连是直通线,PC机与服务器相连是交叉线,那么光纤收发器与交换机相连就是直通线,与服务器相连就是交叉线。当然,现在随着技术进步,光纤收发器的网口也一般做成了自适应模式(自动匹配交叉线和直通线),工程使用时也相应方便了很多。 (二)单纤单网口 随着业务的不断发展,我们面临着一个不可回避的问题,那就是光纤资源紧张,有些单

光纤收发器技术指标

1、盒式工业级一光四电型单纤光纤收发器技术指标 (1)单模单纤双向,发送波长 1310nm,传输距离范围0-25km,输出光功率 -15~-8dBm,接收灵敏度≤-36dBm,SFP 或 DSC; *(2)端口数量:4 个百兆自适应电口+1 个 100M 光接口,背板带宽≥1Gbps;电口直通或交叉连接自适应; #(3)以太网电口支持端口隔离、全双工流量控制功能,须隔离各端口数据及流量; (4)设备功耗<10W; *(5)采用工业级芯片、工业级电源模块、无风扇散热设计; #(6)支持宽温工作环境,工作温度范围-40℃~75℃,存储温度范围-40℃~75℃。防潮,耐腐蚀,工作环境的相对湿度范围5%~95% RH,无凝露。工作温度范围提供公安部安防类检测报告复印件并加盖投标人公章,提供报告编号,以备检验; *(7)支持 IP40 防护等级。提供公安部安防类检测报告复印件并加盖投标人公章,提供报告编号,以备检验; (8)支持接口保护(端口保护); #(9)设备支持标准的 SNMP 网管协议,提供网管平台统一监控远端设备运行状态及告警等,提供5 张网管功能展示界面截图。提供网管 MIB 文件库,配合区平台进行网管功能开发测试工作; #(10)支持单端口多个 VLAN 划分; #(11)支持双冗余供电,直流或交流电源宽电压输入; #(12)支持巨帧的传输,转发帧长9000bytes; (13)设备端口平均抖动时延1us; *(14)设备支持四级级联全程网管; #(15)提供光纤收发器工信部进网许可证复印件并加盖投标人公章; (16)工业指标符合 GB/T 2423 电工电子产品环境试验标准; #(17)工业指标符合 GB/T 17626 电磁兼容国家标准。静电放电和浪涌冲击须提供公安部检测报告复印件并加盖投标人公章,提供报告编号,以备检验。

考勤机使用说明书范文

K1 考勤机使用说明书 注意事项及使用要求: 1.刷卡判断身份时将卡在本机感应区轻轻一晃即可,切勿用卡片拍打机器。 2.在初始化系统时,机器将会丢失原有参数设置,恢复出厂时的参数。 3 ?本机采用TCP和UDP通讯方式,按标准以太网布线方式进行布线。4.本机采集记录时要保证网络通讯的畅通。 5.经常保持机器清洁,防止水、油烟、灰尘、腐蚀性气体等侵入机内,以免影响机器的正常工作。 6.机壳表面沾有污垢和灰尘时,用干燥的细布擦干净,不得使用清洁液及其它化学溶剂,以免腐蚀机壳表面和流入机内损坏元器件。 7.本机发生故障,非专业人员不得打开机器,应与本机的供应商联系解决。 8.申请技术服务时,请提供本机购货合同号、产品序列号、故障现象。 第一章产品功能及技术参数 产品简介: 本机采用非接触式IC 卡感应技术进行身份识别,采用TCP 和UDP 通讯方式,具有快速的实时通讯功能。该机操作简单,方便易用,以考勤为主,附带开门功能。主要有以下功能:1.考勤功能。记录刷卡人员的刷卡时间,卡流水号等;刷卡时显示卡片上的中文姓名和卡编号(由用户定义,如工号,学号等) 2.门禁功能:刷卡时若是合法的身份卡则自动开门。还有密码开门、按钮开门功能。3.系统查看功能:可以查看每一条未采集的刷卡记录;查看记录总数,剩余空间;可以查看机器号和MAC地址;可以查询设备的IP地址和通讯端口。 4.系统设置功能:可以设置机器时间、机器号、开门密码、维护密码、网络参数。 5.维护检测功能:可以检测按键、刷卡检测、初始化系统等功能。 (以上功能操作,可见相关的操作说明) 产品特点: 1.用Mifare One IC 卡,射频信号交换数据,免接触,具有高保密、高可靠性。 2.LCD 大显示屏,可显示时间、日期、星期,刷卡时可以显示用户姓名(仅限中文),时间,卡编号等等。 3.采用触摸键盘输入数据,密封防尘,使用简单! 4.采用TCP 和UDP 通讯方式,可以与公司的局域网直接相连,方便易用。 5.实时通讯强。刷卡记录可以实时采集,同时可以对用户刷卡后立刻进行信息发布,如:生日快乐或任务安排等等。(信息发布功能视客户的考勤软件而定,需要软件的支持。 ) 6.与计算机联网使用(推荐联网使用),也可以脱机单独运行。

光猫、协转、光纤收发器、光端机等接入设备如何区别

光猫、协转、光纤收发器、光端机等接入设备如何区别 光端机:下行业务为2M(E1),可分PDH,SDH光端机,相对来说时钟恢复和复用比较复杂,需要很多交叉,复用,时钟提取定时等多种芯片一起应用. 光猫:属于接口转换器类型,下行可接2M(E1),以太网,V.35业务,就用个转换器芯片就能完成光纤收发器:这个下行业务只有以太网.硬件设计也是最简单的,自己编写一个FPGA代码做程序就OK了.光猫是一种类似于基带MODEM(数字调制解调器)的设备,和基带MODEM不同的是接入的是光纤专线,是光信号。用光电信号的转换和接口协议的转换后接入路由器,他属于是广域网接入的一种,也就是常常说到的光纤接入,只要存在光纤的地方都需要光猫对光信号进行转换。 光电收发器是用局域网中光电信号的转换,而仅仅是信号转换,没有接口协议的转换。一般用在园区网内较长距离,不适于布双绞线的环境。不过随着网络技术的发展,光电转换器和光猫的概念越来越模糊,近期两者基本可以统一为同一种设备了,光电转换器也成为光猫的学名。 协议转换器主要有E1转V.35和E1转以太网两种类型。 光端机,就是将多个E1(一种中继线路的数据传输标准,通常速率为2.048Mbps,此标准为中国和欧洲采用)信号变成光信号并传输的设备(它的作用主要就是实现电-光和光-电转换)。光端机根据传输E1口数量的多少,价格也不同。一般最小的光端机可以传输4个E1,目前最大的光端机可以传输 4032个E1。

光猫是一种类似于基带MODEM(数字调制解调器)的设备,和基带MODEM不同的是接入的是光纤专线,是光信号。 用于广域网中光电信号的转换和接口协议的转换,接入路由器,是广域网接入。光电收发器是用局域网中光电信号的转换,而仅仅是信号转换,没有接口协议的转换。一般用在园区网内较长距离,不适于布双绞线的环境。为了说清楚光猫、光电收发器。我们有必要介绍它们所运用的环境。 光Modem也称为单端口光端机,是针对特殊用户环境而设计的产品,它利用一对光纤进行单E1或单V.35或单10BaseT点到点式的光传输终端设备。该设备作为本地网的中继传输设备,适用于基站的光纤终端传输设备以及租用线路设备。而对于多口的光端机一般会直称作“光端机”,对单端口光端机一般使用于用户端,工作类似常用的广域网专线(电路)联网用的基带MODEM,而有称作“光MODEM”、“光猫”、“光调制解调器”。 在这里我举一个产品的例子:广州华信通信设备有限公司生产的HS-OPT122 V.35光端机(见图1),该设备提供了1路V.35数据通道,此接口可接入路由器的V.35数据接口。光端机的E1和V.35接口速率都可通过拨码开关任意调节,可透传2M数据。HS-OPT122 V.35光端机可作为本地网的中继传输设备,尤其适合作为移动通信网基站的光纤终端传输设备以及租用设备。 我这里所指的光端机仅仅是在数据通信上的产品,实际光端机的产品五花八门,有用有线电视传输的,有用于电话传输的,有用工业

产品样本(大全)-06-以太网光纤收发器及光交换机

六、以太网光纤收发器及光交换机 6.1 以太网光纤收发器 以太网光纤收发器系列产品是江苏新创自主研发创新,专门为以太网信号在单模或多模光纤上远距离可靠传输而设计的。 该系列产品的以太网接口为10/100M 或10/100/1000M。 该系列产品具有点对点式、双纤备份式、总线级联式、环路自愈式等组网方式。 点对点式光纤收发器通过1芯或2芯单模或多模光纤实现以太网信号的远程传输。 双纤备份式光纤收发器通过2芯或4芯单模或多模光纤构成高可靠冗余、主从备份式的光纤网络,这样当任意主光纤、光接口出现断裂或故障时,收发器就会立刻切换到备份光纤和光接口,两点间的通信仍然能够自动恢复而不中断,自动切除故障点;当故障消除时,收发器会自动切回主光纤和光接口工作状态,这样大大提高了现场网络通信的高可靠性,也极大地方便了现场维护。 总线级联式光纤收发器通过1芯或2芯单模或多模光纤构成的光纤总线,可以将远距离总线分布的各个节点上的局域网连接起来,从而节约光纤资源。 环路自愈式光纤收发器通过1芯或2芯单模或多模光纤构成的光纤闭合环路,可以将远距离总线分布的各个节点上的局域网连接起来,构成一个闭合的光纤环路分布式多节点局域网络,这样当任意节点间有一段光纤出现断裂或故障时,或某一个节点的收发器断电或出现故障时,所有节点通信仍然能够自动恢复而不中断,自动切除故障点,这样大大提高了现场网络通信的高可靠性,也极大地方便了现场维护。 该系列产品提供1个或多个以太网电接口,方便用户多个以太网设备同时高效接入。电接口可以是共享的,也可以是物理隔离的。对于共享的收发器,电接口和光接口具有2层交换功能。光接口具有高达1000M的全双工吞吐能力,因此非常适合在高带宽的视频压缩传输网络和业务繁忙的主干高可靠网络中传输。 该系列产品具有极低的传输延迟和超强的以太网包封转发能力,采用完全透明的底层光电转换技术,因此能够透明支持任意以太网协议。以太网电接口具有10/100/1000M自适应能力和线缆自动交叉功能,因此能够与任何10/100/1000M局域网、计算机和交换机相互联。 该系列产品能够透明传输最大10KByte的Jumbo Frame超长帧,端口帧缓冲空间高达

20V转5V,20V转3.3V的LDO芯片规格书

40V高输入电压LDO线性稳压器一般说明 PW6206系列是一款高精度,高输入电压,低静态电流,高速,低压降线性稳压器具有高纹波抑制。在VOUT=5V&VIN=7V时,输入电压高达40V,负载电流高达300mA,采用BCD工艺制造。PW6206提供过电流限制、软启动和过热保护,以确保设备在良好的条件下工作 PW6206调节器有标准SOT89-3L和SOT23-3L封装。标准产品无铅无卤。 特点 ?输入电压:4.75V~40V ?输出电压:1.8V~5.7V ?输出精度:<±2% ?输出电流:150mA(典型值) ?最高300mA@VIN=7V,VOUT=5V,PW6206B50HV封装 ?电源抑制比:60dB@100Hz ?跌落电压:600mV@IOUT=100mA ?静态电流:4.2μA@VIN=12V(典型值) ?ESD HBM:8KV ?推荐电容器:10uF 应用芯片135代2845理8039 Mr。郑,技术工程FAE ?智能电表 ?车内娱乐 ?电动自行车 典型应用电路

应用信息 输入电容器 VIN 和GND 引脚之间需要10μF 的输入电容。电容器应尽可能靠近VIN 引脚,建议使用电解电容器。必须考虑公差和温度系数,以确保电容器在整个温度和工作条件范围内工作。 输出电容器

在实际应用中,选择输出电容器以保证其稳定运行是非常重要的。稳定和正确操作的最小电容为1μF。电容公差应在工作温度范围内±30%或更好。建议电容器类型为MLCC。 空载稳定性 PW6206将在无外部负载的情况下保持稳定和调节。这在CMOS RAM保持活动应用中尤其重要。 典型电路 下图显示了PW6206设备的典型应用电路。根据应用情况,应仔细选择外部组件的值。在插拔应用中,由于芯片上电源的插入和拔出引起的过冲会损坏芯片,因此建议VIN小于30V,输入电压峰值不超过45V。 在封堵应用中,建议R、Cin选用如下: 1Cin=10UF~100UF电解电容器,最大电压大于50V,R=0; 2Cin=1UF~10UF MLCC,最大电压V大于50V,R=2Ω,1206型电阻器应仔细选择,以确保有足够的裕度来承受插入期间的浪涌电流。

1光4电 千兆以太网光纤收发器

系列产品是工业级4口10/100/10000Base-T到1000Base-X的光纤转换,主要用于光纤网络远距离(20/40/60/80/100公里)传输。此款产品提供1路千兆光口;4路百兆以太网电口,并共享千兆带宽。具备完善的告警功能,整机工作稳定可靠,功耗低,集成度高,体积小。 自动适应10/100/1000Mbps环境,支持10/100/1000M自适应、全/半双工方式、支持双绞线口交叉直连自动选择;便于网络的升级/系统调试安装; 设备提供4路千兆以太网电口,1路千兆光口,共享千兆带宽,传输带宽为线速1000M,千兆光口支持2,40、60、80KM及100KM距离传输; 具有广播风暴保护、平衡流量、隔离冲突、检测差错及死机自复位等功能,适合于视频传输等大流量数据应用; 支持VLAN超长数据包的传输,可以与支持IEEE802.1Q协议的交换机产品匹配使用,支持最大为9K字节的以太包; 支持全双工和半双工网络通信,带有自动协商能力; 外置AC220/5V电源适配器,也可外置DC-48V/5V电源适配器;

◆光以太接口 工作波长:1310nm、1550nm 速率:1000M,全双工模式 协议:支持IEEE802.3,IEEE802.1Q(VLAN) MAC地址表:可以学习4096个MAC地址 物理接口:FC/SC 光纤传输的距离受限于光学路径的损耗以及由于连接端子、接头、接插板而造成的附加损耗。 传输距离也可能受到光纤带宽的限制 ◆以太网接口 协议:符合IEEE802.3az,IEEE802.1Q(VLAN) 速率:10/100/1000M自适应,全/半双工完全自适应 MAC地址表:可以学习4096个MAC地址 物理接口:RJ45座,支持Auto-MDIX(交叉/直通线自适应) ◆电气和机械特性 系统电源:AC180V~260V 功耗:≤5W 外观结构:(长×宽×高)93*70*25mm ◆环境指标 工作温度:-10℃—+70℃或-40℃—+85℃(工业级) 储存温度:-40℃—+85℃ 工作湿度:0%—95%(无凝结) MTBF:>100,000小时 产品名称1路千兆光口转4路千兆以太网电口 产品功能描述1路千兆光口转4*10/100/1000M以太网电口;袖珍型,外置电源 业务端口描述1个1*9千兆光口,4个千兆电口 电源AC220V或DC-48V(电源可选)

中控考勤5.0系统操作说明书

1 中控考勤系统操作说明书 一、部门设置 1、点击系统界面左侧一栏【部门表】 2、在新界面选定【总公司】单击【新设部门】 3、在打开的对话框里面输入要设置的部门。点击确认 4、按照步骤2-3设置其他部门

2 二、员工入职录入 1、在系统界面上侧打开【人员维护】 2.在新打开对话框选定员工所在部门,点击【增加按钮】 3、在新打开页面输入员工信息,并记录该员工考勤号码 4、凭系统中刚输入的该员工考勤号码到其部门考勤机录入指纹即可。 三、排班设置 为了方便进行考勤数据统计分析,需要对员工上下班时间,打卡时间进行设置,也就是班次设置。因每个部门上班时间不同,需要进行早晚班三个班次设置。现以早班为例进行班次设置并进行人员排班。 1、首先进行上下班时间段设置,在考勤系统界面左下角单击【时间段维护】

3 2、在新打开界面输入时间段信息,输入完毕后,点击保存。 3、再次点击【增加】按钮进行设置下午早班,晚上早班,周三早班、周六早班(因公司周三、周六晚班下班时间不同,所以稍微麻烦) 4、输入完成后,如下图: 5、按照1-3的步骤可进行晚班、正常班的时间段设置。然后进行班次管理 6、回至考勤系统界面,点击右下角【班次管理】 7、在新开界面,单击【新增班次】—【修改】输入班次信息—【保存】

8、点击下方【增加时间段】按钮 9、进行周一周二周四周五周天上午、下午、晚上时间段设置,去掉周三、周 六前面的√,选定上午早班、下午早班、晚上早班并点击【确认】。如图: 4 10、点击【增加时间段】添加周三时间段,去掉周一周二周四周五周六 周天前面的√,选定上午早班、下午早班、周三早班时间段,并点击【确认】

(2020)(考勤管理)考勤机软件说明书

(考勤管理)考勤机软件说明书

说明 欢迎使用《考勤人事系统V2.0》,本说明书适用于55系列射频卡考勤机及V/C和Q7系列指纹考勤机,在使用考勤软件前请仔细阅读此说明书,有不明之处请与当地的分公司或经销商联系。 目录 1 系统简介┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉4 2 系统组成┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉4 3 系统安装与卸载 3.1 软件安装步骤┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉5 3.2 数据库的安装┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉8

3.3 数据库设置┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉15 3.4 初使化数据库┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉16 4 人事资料管理 4.1 公司信息设置┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉18 4.2 公司部分设置┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉18 4.3 员工信息设置┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉20 4.4 登记员工离职┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉28 4.5 员工离职查询┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉39 4.6 员工工种设置┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉30 4.7 学历资料设置┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉31 4.8 民族资料设置┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉32 4.9 籍贯资料设置┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉33 4.10 职位资料设置┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉34 4.11 职称资料设置┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉35 4.12 政治面貌设置┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉36 4.13 员工宿舍设置┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉36

5 考勤管理 5.1 考勤规则┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉38 5.2 设置规则┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉40 5.3 班次定义┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉42 5.4 上班规律┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉43 5.5 开始排班┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉44 5.6 总排班表┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉46 5.7 假日登记┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉48 5.8 请假登记┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉49 5.9 加班登记┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉50 5.10 手工补卡┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉52 5.11 计算规则┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉53 6 统计报表 6.1 考勤资料分析┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉54 6.2 考勤日报表┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉┉55

10和100和1000M光纤收发器

名称:10/100/1000M光纤收发器 编号:Pro200721091422 型号:YD-10/100/1000M 厂商:武汉易德网络技术有限公司 转换延长网络的传输距离,同时使网络的带宽扩充到 1000M。凡符合以太网标准协议的千兆网络设备如交换机、路由器等均可与之互通。支持小区接入、综合办公楼接入和企业用户接入。 主要特性 ◇内置电源式采用单插槽结构,可兼容10/100M收发器机架,满配16个模块 ◇采用低功耗芯片设计,单台功耗≤5W; ◇发热量比其他公司同类产品低很多,基本接近10/100M收发器的温度; ◇产品兼容性强,可兼容目前市面上所有厂家的网卡和交换机; ◇可选择双纤双向或单纤双向光纤收发器模块 ◇电口支持MDI/MDIX自动识别; ◇1000M产品可向下兼容10M、100M网络; ◇支持1000Base-SX/LX/LH/ZX光纤传输标准,可与其他产品互通; ◇支持超长帧传输(1936byte/帧); ◇电源可选择AC 220V或DC -48V; 产品规格 ◇外型尺寸155mm×125mm×33mm ◇电源特性输入工作电压:220VAC或-48VDC ◇功耗 5W ◇重量0.85Kg ◇工作温度0℃~60℃ ◇保存温度-10℃~70℃ ◇工作湿度5%~95%(无冷凝) 产品兼容协议 ◇IEEE802.3 以太网(10Mbps) ◇IEEE802.3u 快速以太网(100Mbps) ◇IEEE802.3ab 千兆以太网(1000Mbps) ◇IEEE802.1d 生成树协议 ◇IEEE802.1Q VLAN标记 ◇IEEE802.1p QOS优先级 ◇IEEE802.3x 全双工流量控制 ◇CISCO ISL和VTP协议 订购信息