ADC0832芯片介绍

这一课我们来学习ADC0832芯片的应用。模-数(AD)和数-模(DA)转换是模拟电路和数字电路进行沟通的渠道,从前面的课程我们知道,数字电路里,电平只有高和低两种状态,比如5V和0V,对应着1和0;模拟电路里,电平则理论上有无数个状态,比如0V、0.1V、0.2V…等等。如何将模拟电平值在数字电路里表达出来呢?这就需要AD转换过程,同理的,也有DA转换过程。这一课,我们就利用实验板上的ADC0832芯片来实AD转换这一过程。

ADC0832是美国国家半导体公司生产的一种8位分辨率、双通道A/D转换芯片。由于它体积小,兼容性强,性价比高而深受单片机爱好者及企业欢迎,其目前已经有很高的普及率。学习并使用ADC0832可是使我们了解A/D转换器的原理,有助于我们单片机技术水平的提高。

ADC0832具有以下特点:

● 8位分辨率;

● 双通道A/D转换;

● 输入输出电平与TTL/CMOS相兼容;

● 5V电源供电时输入电压在0~5V之间;

● 工作频率为250KHZ,转换时间为32μS;

● 一般功耗仅为15mW;

● 8P、14P—DIP(双列直插)、PICC多种封装;

● 商用级芯片温宽为0°C to +70°C?,工业级芯片温宽为40℃ to +85℃

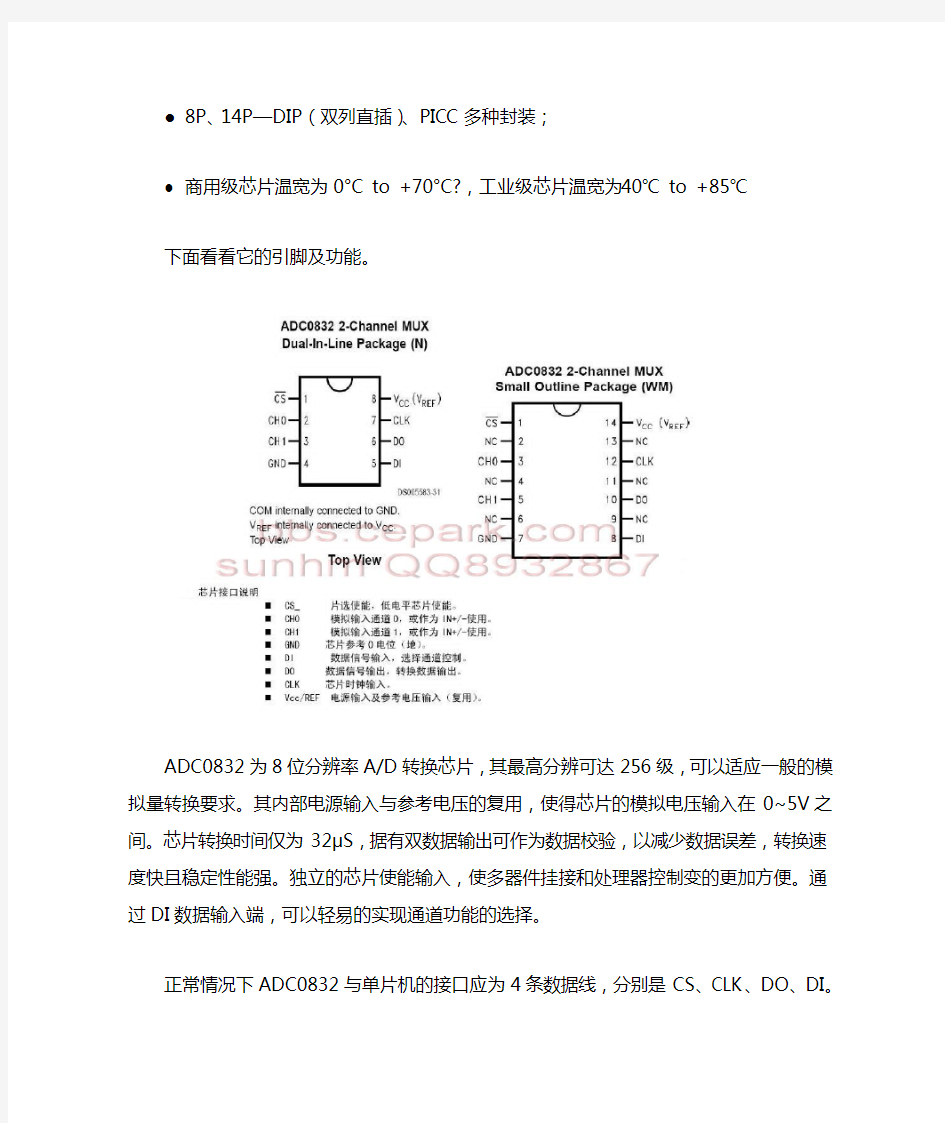

下面看看它的引脚及功能。

ADC0832为8位分辨率A/D转换芯片,其最高分辨可达256级,可以适应一般的模拟量转换要求。其内部电源输入与参考电压的复用,使得芯片的模拟电压输入在0~5V之间。芯片转换时间仅为32μS,据有双数据输出可作为数据校验,以减少数据误差,转换速度快且稳定性能强。独立的芯片使能输入,使多器件挂接和处理器控制变的更加方便。通过DI数据输入端,可以轻易的实现通道功能的选择。

正常情况下ADC0832与单片机的接口应为4条数据线,分别是CS、CLK、DO、DI。但由于DO端与DI端在通信时并未同时有效并与单片机的接口是双向的,所以电路设计时可以将DO和DI并联在一根数据线上使用。我们看看在实验板上它是怎么连接的。

ADC0832的控制引脚CS、CLK、DO、DI占用了P20、P36、P37三个个IO口。其中,DO和DI共用一条数据线。象前二课一样,我们来通过它的时序图来学习对它进行

控制。

与DS1302非常相似,CS作为选通信号,在时序图中可以看到,以CS置为低电平开始,一直到置为高电平结束。CLK提供时钟信号,我们要注意看CLK的信号的箭头指向,向上为上升沿有效,向下为下降沿有效。DI、DO作为数据端口。

当ADC0832未工作时其CS输入端应为高电平,此时芯片禁用,CLK和DO/DI的电平可任意。当要进行A/D转换时,须先将CS使能端置于低电平并且保持低电平直到转换完全结束。此时芯片开始转换工作,同时由处理器向芯片时钟输入端CLK输入时钟脉冲,DO/DI端则使用DI端输入通道功能选择的数据信号。在第1个时钟脉冲的下沉之前DI端必须是高电平,表示启始信号。在第2、3个脉冲下沉之前DI 端应输入2位数据(SGL、Odd)用于选择通道功能,当此2位数据为“1”、“0”时,只对CH0进行单通道转换。当2位数据为“1”、“1”时,只对CH1进行单通道转换。当2位数据为“0”、“0”时,将CH0作为正输入端IN+,CH1作为负输入端IN-进行输入。当2位数据为“0”、“1”时,将CH0作为负输入端IN-,CH1作为正输入端IN+进行输入。

在完成输入启动位、通道选择之后,就可以开始读出数据,转换得到的数据会被送出二次,一次高位在前传送,一次低位在前传送,连续送出。在程序读取二个数据后,我们可以加上检验来看看数据是否被正确读取。

下面,我们看看这部分程序该怎么写。

这个是读取数值的子函数,二通道独立读取,入口参数是通道值(0或1),出口参数则是读取的结果,里面对两次读取的值进行判断,实际应用中,可以灵活处理,要不要判断、如果数值不一致要不要返回标志,这些留给大家思考。

应用时,只要写成变量名=GetValue0832(通道值); 即可返回转换值。

由于ADC0832是8位分辨率,返回的数值在0~255之间,对应模拟数值为0~5V,因此每一档对应的电压值约为0.0196V。大家可以在通道输入端引入模拟信号(0~5V)进行测试,比如可以在通道脚和地之间接入电池来测试电池电压值。

从LCD1602、DS1302和ADC0832这三个器件的控制上,我们可以看到,LCD1602属于并行数据传送方式,它的数据在进行传送时,是同时送到数据口上的(P0口,8位同时送出),而DS1302、ADC0832则是通过串行方式进行传送,它的特点是数据传送每次只传送一位。因此,在同一时钟频率下,并行传送方式要比串行传送方式快得多,但它的缺点是占用IO口比较多(数据口要8位),而串行传送方式数据口只要1位,各有各优缺点,视乎实际应用的需要来选择器件。

这一课到此结束,大家课后把LCD1602显示结合起来,在上面显示读取的数值,

尝试做出一个电压测量仪。

常用系列芯片功能

常用4000 系列芯片功能 CD4000 双3 输入端或非门单非门 CD4001 四2 输入端或非门 CD4002 双4 输入端或非门 CD4006 18 位串入/串出移位寄存器 CD4007 双互补对加反相器 CD4008 4 位超前进位全加器 CD4009 六反相缓冲/变换器 CD4010 六同相缓冲/变换器 CD4011 四2 输入端与非门 CD4012 双4 输入端与非门 CD4013双主-从D型触发器 CD4014 8 位串入/并入-串出移位寄存器 CD4015 双4位串入/并出移位寄存器 CD4016 四传输门 CD4017 十进制计数/分配器 CD4018 可预制1/N 计数器 CD4019 四与或选择器 CD4020 14 级串行二进制计数/分频器 CD4021 08 位串入/并入-串出移位寄存器CD4022 八进制计数/分配器 CD4023 三3 输入端与非门 CD4024 7 级二进制串行计数/分频器 CD4025 三3 输入端或非门 CD4026 十进制计数/7 段译码器 CD4027 双J-K 触发器 CD4028 BCD 码十进制译码器 CD4029 可预置可逆计数器 CD4030 四异或门 CD4031 64 位串入/串出移位存储器 CD4032 三串行加法器 CD4033 十进制计数/7 段译码器 CD4034 8 位通用总线寄存器 CD4035 4 位并入/串入-并出/串出移位寄存CD4038 三串行加法器 CD4040 12 级二进制串行计数/分频器 CD4041 四同相/反相缓冲器 CD4042 四锁存D 型触发器 CD4043 三态R-S 锁存触发器("1"触发)CD4044 四三态R-S 锁存触发器("0"触发)

NDAM-4017数据手册

NDAM 系列模块不支持热插拔,请不要带电拆装模块! NDAM-4017 ——————————————概述 NDAM 是全新一代基于网络通讯的刀片式数据采集控制系统。采用积木化结构,简单、灵活,通讯模块和各种数据采集控制模块自由组合,应对各种现场应用。可以通过以太网、RS-485/RS-422/RS-232或CAN-bus 等通讯方式组建网络。 NDAM-4017是模拟量输入模块,可以同时采集6路差分信号和2路单端信号,采样精度高达16位。适用于采集工业现场的各种电压和电流信号。例如来自各种传感器、变送器的信号都可以通过它来采集。 NDAM-4017采用电气隔离技术和看门狗技术,有效保障设备安全可靠运行。 ——————————————产品特性 ◆ 32位ARM 处理器; ◆ 嵌入式实时操作系统; ◆ 输入通道数:6路差分输入,2路单端输入; ◆ 输入信号范围:±10V 、±5V 、±2.5V 、 ±500mV 、±150mV ; ◆ AD 转换分辨率:16位; ◆ 采样速率:10次/秒(全通道); ◆ 隔离耐压:1000 V DC ; ◆ ESD 保护; ◆ 支持远程升级; ◆ 工作温度范围:-20℃~+85℃; ◆ 工业级塑料外壳,标准DIN 导轨安装。 ————————————产品应用 工业现场控制 远程监控与数据采集 电力通讯 仓储与监控 电子产品制造 食品和饮料行业 包装和物料转移 安防产品 —————————————订购信息 ————————————————————————————————典型应用

修订历史

目录 1. NDAM分布式数据采集控制系统简介 (1) 2. NDAM-4017模拟量输入模块 (3) 2.1 功能简介 (3) 2.1.1 光电隔离 (3) 2.1.2 电源隔离 (3) 2.1.3 嵌入式实时操作系统和看门狗 (3) 2.1.4 高速采集 (4) 2.1.5 可变增益 (4) 2.2 技术指标 (4) 2.2.1 模拟量输入 (4) 2.2.2 系统参数 (4) 2.3 原理框图 (5) 2.4 端子信息 (6) 2.4.1 端子排列 (6) 2.4.2 端子描述 (6) 2.5 电气参数 (7) 2.6 机械规格 (8) 2.6.1 机械尺寸 (8) 2.6.2 安装方法 (8) 3. 免责声明 (10)

ITCP-4017数据采集用户手册

目录 1. ITCP-4017功能简介 (1) 1.1 主要技术指标 (2) 1.1.1 模拟量输入 (2) 1.1.2 数字量输出 (2) 1.1.3 系统参数 (2) 1.2 原理框图 (3) 1.3 端子信息 (4) 1.3.1 端子排列 (4) 1.3.2 端子描述 (4) 1.4 电气参数 (5) 1.5 通信参数配置 (5) 1.6 信号指示灯 (6) 1.7 电源和通讯线的连接 (6) 1.7.1 电源连接 (6) 1.7.2 网络连接 (6) 1.8 机械规格 (7) 1.8.1 机械尺寸 (7) 1.8.2 安装方式 (7) 2. ITCP-4017的模拟量输入功能 (9) 2.1 模拟量输入 (9) 2.2 输入采样原理 (9) 2.3 输入接线 (9) 2.4 采样值计算 (9) 2.4.1 最高位符号位 (9) 2.4.2 ADC数据类型 (10) 2.4.3 有符号整型 (10) 2.4.4 量程百分比 (10) 2.5 模拟量输入通道控制 (10) 3. ITCP-4017的数字量输出功能 (11) 3.1 输出原理 (11) 3.2 输出接线方式 (11) 3.3 数字量输出通道控制 (12) 4. ITCP-4017应用示例 (13) 4.1 安装设备 (13) 4.2 操作设备 (13) 4.2.1 ITCP系列模块通信参数的修改 (13) 4.2.2 RJ-45以太网主机通信参数设置 (14) 4.2.3 模块信息配置 (14) 4.2.4功能操作 (16) 4.2.4.1模拟量输入 (17)

5. ITCP-4017 命令简析 (18) 5.1 MODBUS/TCP协议命令结构 (18) 5.2 MODBUS/TCP命令码介绍 (19) 5.3 ITCP资源地址说明 (19) 5.3.1 ITCP-4017的资源地址 (19) 6免责声明 (20)

CD4017引脚图,引脚功能及工作时序图

CD4017引脚图,引脚功能及工作时序图 CD4017功能简述: CD4017是5位Johnson计算器,具有10个译码输出端,CP,CR,INH输入端。时钟输入端的斯密特触发器具有脉冲整形功能,对输入时钟脉冲上升和下降时间无限制。INH为低电平时,计算器在时钟上升沿计数;反之,计数功能无效。CR为高电平时,计数器清零。Johnson 计数器,提供了快速操作,2输入译码选通和无毛刺译码输出。防锁选通,保证了正确的计数顺序。译码输出一般为低电平,只有在对应时钟周期内保持高电平。在每10个时钟输入周期CO信号完成一次进位,并用作多级计数链的下级脉动时钟。 CD4017的引脚图 CD4017引脚功能: CD4017内部是除10的计数器及二进制对10进制译码电路。CD4017有16支脚,除电源脚VDD及VSS为电源接脚,输入电压范围为3–15V 之外,其余接脚为: A、频率输入脚:CLOCK(Pin14),为频率信号的输入脚。 B、数据输出脚: a、Q1-Q9(Pin3,2,4,7,10,1,5,6,9,11),为*后的时进制输出接脚,被计数到的值,其输出为Hi,其余为Lo电位。

b、CARRY OUT(Pin12),进位脚,当4017计数10个脉冲之后,CARRY OUT将输出一个脉波,代表产生进位,共串级计数器使用。 D、控制脚: a、CLEAR(Pin15):清除脚或称复位(Reset)脚,当此脚为Hi时,会使CD4017的Q0为”1”,其余Q1-Q9为”0”。 b、CLOCK ENABLE(Pin13),时序允许脚,当此脚为低电位,CLOCK 输入脉波在正缘时,会使CD4017计数,并改变Q1-Q9的输出状态。 CD4017工作时序

74系列芯片功能大全

74系列芯片功能大全7400 TTL 2输入端四与非门 7401 TTL 集电极开路2输入端四与非门 7402 TTL 2输入端四或非门 7403 TTL 集电极开路2输入端四与非门 7404 TTL 六反相器 7405 TTL 集电极开路六反相器 7406 TTL 集电极开路六反相高压驱动器 7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器 74109 TTL 带预置清除正触发双J-K触发器 7411 TTL 3输入端3与门 74112 TTL 带预置清除负触发双J-K触发器 7412 TTL 开路输出3输入端三与非门 74121 TTL 单稳态多谐振荡器 74122 TTL 可再触发单稳态多谐振荡器 74123 TTL 双可再触发单稳态多谐振荡器 74125 TTL 三态输出高有效四总线缓冲门 74126 TTL 三态输出低有效四总线缓冲门 7413 TTL 4输入端双与非施密特触发器 74132 TTL 2输入端四与非施密特触发器 74133 TTL 13输入端与非门 74136 TTL 四异或门 74138 TTL 3-8线译码器/复工器 74139 TTL 双2-4线译码器/复工器 7414 TTL 六反相施密特触发器 74145 TTL BCD—十进制译码/驱动器 7415 TTL 开路输出3输入端三与门 74150 TTL 16选1数据选择/多路开关 74151 TTL 8选1数据选择器 74153 TTL 双4选1数据选择器 74154 TTL 4线—16线译码器 74155 TTL 图腾柱输出译码器/分配器 74156 TTL 开路输出译码器/分配器 74157 TTL 同相输出四2选1数据选择器 74158 TTL 反相输出四2选1数据选择器 7416 TTL 开路输出六反相缓冲/驱动器 74160 TTL 可预置BCD异步清除计数器 74161 TTL 可予制四位二进制异步清除计数器 74162 TTL 可预置BCD同步清除计数器 74163 TTL 可予制四位二进制同步清除计数器 74164 TTL 八位串行入/并行输出移位寄存器 74165 TTL 八位并行入/串行输出移位寄存器 74166 TTL 八位并入/串出移位寄存器

4017芯片

数字电路CD4017的原理及应用电路 2008/10/18 00:26 数字电路CD4017是十进制计数/分频器,它的内部由计数器及译码器两部分组成,由译码输出实现对脉冲信号的分配,整个输出时序就是Q0、Q1、Q2、…、Q9依次出现与时钟同步的高电平,宽度等于时钟周期。 CD4017有10个输出端(Q0~Q9)和1个进位输出端~Q5-9。每输入10个计数脉冲,~Q5-9就可得到1个进位正脉冲,该进位输出信号可作为下一级的时钟信号。 CD4017有3个输(MR、CP0和~CP1),MR为清零端,当在MR端上加高电平或正脉冲时其输出Q0为高电平,其余输出端(Q1~Q9)均为低电平。CP0和~CPl是2个时钟输入端,若要用上升沿来计数,则信号由CP0端输入;若要用下降沿来计数,则信号由~CPl端输入。设置2个时钟输入端,级联时比较方便,可驱动更多二极管发光。由此可见,当CD4017有连续脉冲输入时,其对应的输出端依次变为高电平状态,故可直接用作顺序脉冲发生器。 CD4017有两个时钟端 CP 和 EN,若用时钟脉冲的上沿计数,则信号从 CP 端输入;若用下降沿计数,则信号从 EN 端输入。设置两个时钟端是为了级联方便。 CD4017 与 CD4022 是一对姊妹产品,主要区别是 CD4022 是八进制的,所以译码输出仅有 Y0~Y7,每输入 8 个脉冲周期,就可得到一个进位输出,它们的管脚相同,不过 CD4022 的 6、9 脚是空脚。

cd4017方框 图 cd4017引 脚图 一、用一个CD4017制成的彩灯电路 1.用一个CD4017制作的彩灯电路如图1 所示。 cd4017电路图 2.电路工作原理 CD4017输出高电平的顺序分别是③、②、④、⑦、⑩、①、⑤、⑥、⑨脚,故③、②、④、⑦、⑩、①脚的高电平使6串彩灯向右顺序发光,⑤、⑥、③脚的高电平使6串彩灯由中心向两边散开发光。各种发光方式可按自己的需要进行具体的组合,若要改变彩灯的闪光速度,可改变电容C1的大小。 二、用三个CD4O17彩灯电路图 CD4017的级连,如图2所示。

数字电路CD4017的原理及应用电路

数字电路CD4017得原理及应用电路 数字电路CD4017就是十进制计数/分频器,它得内部由计数器及译码器两部分组成,由译码输出实现对脉冲信号得分配,整个输出时序就就是Q0、Q1、Q2、…、Q9依次出现与时钟同步得高电平,宽度等于时钟周期。 CD4017有10个输出端(Q0~Q9)与1个进位输出端~Q5-9。每输入10个计数脉冲,~Q5-9就可得到1个进位正脉冲,该进位输出信号可作为下一级得时钟信号。 CD4017有3个输(MR、CP0与~CP1),MR为清零端,当在MR端上加高电平或正脉冲时其输出Q0为高电平,其余输出端(Q1~Q9)均为低电平。CP0与~CPl 就是2个时钟输入端,若要用上升沿来计数,则信号由CP0端输入;若要用下降沿来计数,则信号由~CPl端输入。设置2个时钟输入端,级联时比较方便,可驱动更多二极管发光。由此可见,当CD4017有连续脉冲输入时,其对应得输出端依次变为高电平状态,故可直接用作顺序脉冲发生器。 CD4017有两个时钟端 CP 与 EN,若用时钟脉冲得上沿计数,则信号从 CP 端输入;若用下降沿计数,则信号从 EN 端输入。设置两个时钟端就是为了级联方便。 CD4017 与 CD4022 就是一对姊妹产品,主要区别就是 CD4022 就是八进制得,所以译码输出仅有 Y0~Y7,每输入 8 个脉冲周期,就可得到一个进位输出,它们得管脚相同,不过 CD4022 得 6、9 脚就是空脚。 cd4017方框图cd4017引脚图 一、用一个CD4017制成得彩灯电路 1、用一个CD4017制作得彩灯电路如图1 所示。

cd4017电路图 2、电路工作原理 CD4017输出高电平得顺序分别就是③、②、④、⑦、⑩、①、⑤、⑥、⑨脚,故③、②、④、⑦、⑩、①脚得高电平使6串彩灯向右顺序发光,⑤、⑥、③脚得高电平使6串彩灯由中心向两边散开发光。各种发光方式可按自己得需要进行具体得组合,若要改变彩灯得闪光速度,可改变电容C1得大小。 二、用三个CD4O17彩灯电路图 CD4017得级连,如图2所示。 cd4017级联原理图 CD4017级连后可以顺序输出24个高电平,同上理可组合出各种不同得发光方式,见图3,可使6串彩灯向右流水发光,再向左流水发光,中心向两边散开后再向中心靠拢发光,1、3、5、2、4、6串间隔发光等等 CD4511就是一个用于驱动共阴极 LED (数码管)显示器得 BCD 码—七段码译码器,特点:具有BCD转换、消隐与锁存控制、七段译码及驱动功能得CMOS电路能

CD4017资料

CD4017引脚图,电路图,原理图资料 十进制计数/分频器CD4017,其内部由计数器及译码器两部分组成,由译码输出实现对脉冲信号的分配,整个输出时序就是O0、O1、O2、…、O9依次出现与时钟同步的高电平,宽度等于时钟周期。 CD4017有10个输出端(O0~O9)和1个进位输出端~O5-9。每输入10个计数脉冲,~O5-9就可得到1个进位正脉冲,该进位输出信号可作为下一级的时钟信号。 CD4017有3个输入(MR、CP0和~CP1),MR为清零端,当在MR端上加高电平或正脉冲时其输出O0为高电平,其余输出端(O1~O9)均为低电平。CP0和~CPl是2个时钟输入端,若要用上升沿来计数,则信号由C P0端输入;若要用下降沿来计数,则信号由~CPl端输入。设置2个时钟输入端,级联时比较方便,可驱动更多二极管发光。 由此可见,当CD4017有连续脉冲输入时,其对应的输出端依次变为高电平状态,故可直接用作顺序脉冲发生器。

CD4017引脚图 一、用一个CD4017制成的彩灯电路 1.用一个CD4017制作的彩灯电路如图1 所示。

.电路工作原理 CD4017输出高电平的顺序分别是③、②、④、⑦、⑩、①、⑤、⑥、⑨脚,故③、②、④、⑦、⑩、①脚的高电平使6串彩灯向右顺序发光,⑤、⑥、③脚的高电平使6串彩灯由中心向两边散开发光。各种发光方式可按自己的需要进行具体的组合,若要改变彩灯的闪光速度,可改变电容C1的大小。 二、用三个CD4O17彩灯电路图 CD40 17的级连,如图2所示。 2.CD4017级连后可以顺序输出24个高电平,同上理可组合出各种不同的发光方式,见图3,可使6串彩灯向右流水发光,再向左流水发光,中心向

4017 详细功能

CD4017引脚功能参数图,电路图,原理图资料 十进制计数/分频器CD4017,其内部由计数器及译码器两部分组成,由译码输出实现对脉冲信号的分配,整个输出时序就是O0、O1、O2、…、O9依次出现与时钟同步的高电平,宽度等于时钟周期。 CD4017有10个输出端(O0~O9)和1个进位输出端~O5-9。每输入10个计数脉冲,~O5-9就可得到1个进位正脉冲,该进位输出信号可作为下一级的时钟信号。 CD4017有3个输(MR、CP0和~CP1),MR为清零端,当在MR端上加高电平或正脉冲时其输出O0为高电平,其余输出端(O1~O9)均为低电平。CP0和~CPl是2个时钟输入端,若要用上升沿来计数,则信号由CP0端输入;若要用下降沿来计数,则信号由~CPl端输入。设置2个时钟输入端,级联时比较方便,可驱动更多二极管发光。 由此可见,当CD4017有连续脉冲输入时,其对应的输出端依次变为高电平状态,故可直接用作顺序脉冲发生器。 此主题相关图片如下:1111.jpg CD4017引脚图 一、用一个CD4017制成的彩灯电路 1.用一个CD4017制作的彩灯电路如图1所示。

此主题相关图片如下:222.jpg 2.电路工作原理 CD4017输出高电平的顺序分别是③、②、④、⑦、⑩、①、⑤、⑥、⑨脚,故③、②、④、⑦、⑩、①脚的高电平使6串彩灯向右顺序发光,⑤、⑥、③脚的高电平使6串彩灯由中心向两边散开发光。各种发光方式可按自己的需要进行具体的组合,若要改变彩灯的闪光速度,可改变电容C1的大小。 二、用三个CD4O17彩灯电路图 CD4017的级连,如图2所示。 此主题相关图片如下:3333.gif CD4017原理图电路 2.CD4017级连后可以顺序输出24个高电平,同上理可组合出各种不同的发光方式,见图3,可使6串彩灯向右流水发光,再向左流水发光,中心向两边散开后再向中心靠拢发光,1、3、5、2、4、6串间隔发光等等

系列芯片功能大全

74系列芯片功能大全 7400 TTL 2输入端四与非门 7401 TTL 集电极开路2输入端四与非门 7402 TTL 2输入端四或非门 7403 TTL 集电极开路2输入端四与非门 7404 TTL 六反相器 7405 TTL 集电极开路六反相器 7406 TTL 集电极开路六反相高压驱动器 7407 TTL 集电极开路六正相高压驱动器 7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门 7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器 74109 TTL 带预置清除正触发双J-K触发器 7411 TTL 3输入端3与门 74112 TTL 带预置清除负触发双J-K触发器 7412 TTL 开路输出3输入端三与非门 74121 TTL 单稳态多谐振荡器 74122 TTL 可再触发单稳态多谐振荡器 74123 TTL 双可再触发单稳态多谐振荡器 74125 TTL 三态输出高有效四总线缓冲门 74126 TTL 三态输出低有效四总线缓冲门 7413 TTL 4输入端双与非施密特触发器 74132 TTL 2输入端四与非施密特触发器 74133 TTL 13输入端与非门 74136 TTL 四异或门 74138 TTL 3-8线译码器/复工器 74139 TTL 双2-4线译码器/复工器 7414 TTL 六反相施密特触发器 74145 TTL BCD—十进制译码/驱动器 7415 TTL 开路输出3输入端三与门 74150 TTL 16选1数据选择/多路开关 74151 TTL 8选1数据选择器 74153 TTL 双4选1数据选择器 74154 TTL 4线—16线译码器 74155 TTL 图腾柱输出译码器/分配器 74156 TTL 开路输出译码器/分配器 74157 TTL 同相输出四2选1数据选择器 74158 TTL 反相输出四2选1数据选择器 7416 TTL 开路输出六反相缓冲/驱动器 74160 TTL 可预置BCD异步清除计数器 74161 TTL 可予制四位二进制异步清除计数器 74162 TTL 可预置BCD同步清除计数器 74163 TTL 可予制四位二进制同步清除计数器 74164 TTL 八位串行入/并行输出移位寄存器 74165 TTL 八位并行入/串行输出移位寄存器 74166 TTL 八位并入/串出移位寄存器

各种芯片功能表

各种芯片功能表 74系列:: 74LS00 TTL 2输入端四与非门 74LS01 TTL 集电极开路2输入端四与非门74LS02 TTL 2输入端四或非门 74LS03 TTL 集电极开路2输入端四与非门74LS04 TTL 六反相器 74LS05 TTL 集电极开路六反相器 74LS06 TTL 集电极开路六反相高压驱动器74LS07 TTL 集电极开路六正相高压驱动器74LS08 TTL 2输入端四与门 74LS09 TTL 集电极开路2输入端四与门 74LS10 TTL 3输入端3与非门 74LS107 TTL 带清除主从双J-K触发器 74LS109 TTL 带预置清除正触发双J-K触发器74LS11 TTL 3输入端3与门 74LS112 TTL 带预置清除负触发双J-K触发器74LS12 TTL 开路输出3输入端三与非门 74LS121 TTL 单稳态多谐振荡器 74LS122 TTL 可再触发单稳态多谐振荡器 74LS123 TTL 双可再触发单稳态多谐振荡器74LS125 TTL 三态输出高有效四总线缓冲门74LS126 TTL 三态输出低有效四总线缓冲门74LS13 TTL 4输入端双与非施密特触发器74LS132 TTL 2输入端四与非施密特触发器74LS133 TTL 13输入端与非门 74LS136 TTL 四异或门 74LS138 TTL 3-8线译码器/复工器 74LS139 TTL 双2-4线译码器/复工器 74LS14 TTL 六反相施密特触发器 74LS145 TTL BCD—十进制译码/驱动器 74LS15 TTL 开路输出3输入端三与门 74LS150 TTL 16选1数据选择/多路开关 74LS151 TTL 8选1数据选择器 74LS153 TTL 双4选1数据选择器 74LS154 TTL 4线—16线译码器 74LS155 TTL 图腾柱输出译码器/分配器 74LS156 TTL 开路输出译码器/分配器

4017芯片引脚功能

4017芯片引脚功能 、用一个CD4017制成的彩灯电路 1.用一个CD4017制作的彩灯电路如图1 所示。

CMOS集成电路CD4017C采用标准的双列直插式脚塑封,它的引脚排列如图1所示。CC4017 是国标型号,它与国外同类产品CD4017 在逻辑功能、引出端和电参数等方面完全相同,可以直接互换。其引脚功能如1: ①脚(Y5),第5输出端; ②脚(Y1),第1输出端; ③脚(Y0),第0输出端,电路清零时,该端为高电平; ④脚(Y2),第2输出端; ⑤脚(Y6).第6输出端; ⑥脚(y7),第7输出端; ⑦脚(Y3),第3输出端; ⑧脚(vss).电源负端; ⑨脚(Y8),第8输出端; ⑩脚(Y4).第4输出端; 脚(Y9).第9输出端; 脚(Qco),级联进位输出端,每输入10 个时钟脉冲,就可得一个进位输出脉冲,因此进位输出信号可作为下一级计数器的时钟信号。 脚(EN),时钟输入端,脉冲下降沿有效; 脚(CP),时钟输入端.脉冲上升沿有效; 脚(R),清零输入端,在“R”端加高电平或正脉冲时,CD40171C 计数器中各计数单元输出低电平“0”,在译码器中只有对应“0”状态的输出端Y0 为高电平; 脚(VDD),电源正端.3~18V 直流电压。 CD40171C 内部逻辑电原理图如图1-2 所示。它是由十进制计数器电路和时序译码电路两部分组成。其中的D 触发器Fl~F5 构成了十进制约翰逊计数器,门电路5~14构成了时序译码电路。约翰逊汁数器的结构比较简单.它实质上是一种串行移位寄存器。除了第3 个触发器是通过门电路15、16 构成的组合逻辑电路作用于F3 的D3 端以外,其余各级均是将前一级触发器的输出端连接到后一级触发器的输入端D 的,计数器最后—级的Q5 端连接到第一级的D1 端。这种计数器具有编码可靠,工作速度快、译码简单,只需由二输入瑞的与门即可译码,且译码输出无过渡脉冲干扰等特点。通常只有译码选中的那个输出端为高电平,其余输出端均为低电平。约翰逊计数器状态如表1-1所示。

芯片引脚说明

CD4017引脚图: CD4017 是5 位Johnson 计数器,具有10 个译码输出端,14(CL)、15(CR)、13(INH 或EN)输入端。时钟输入端的斯密特触发器具有脉冲整形功能,对输入时钟脉冲上升和下降时间无限制。INH 为低电平时,计数器在时钟上升沿计数;反之,计数功能无效。CR 为高电平时,计数器清零。Johnson 计数器,提供了快速操作、2 输入译码选通和无毛刺译码输出。防锁选通,保证了正确的计数顺序。译码输出一般为低电平,只有在对应时钟周期内保持高电平。在每10 个时钟输入周期CO 信号完成一次进位,并用作多级计数链的下级脉动时钟。 引出端功能符号:CO(12):进位脉冲输渊;CL:时钟输入端;(RESEST)CR:清除端;INH(EN):禁止端;Q0-Q9 计数脉冲输出端;VDD:正电源;VSS:地。 CD40110的引脚:

Ya~Yg:七段码,高电平有效; CPD(CP-):第七脚,减一、脉冲上升沿有效; CPU(CP+):第九脚,加一、脉冲上升沿有效; LE:第六脚,高电平有效,锁存数据; CT(TE):第四脚,高电平有效,禁止计数; CR(R):第五脚,高电平有效,清除计数显示。 数字式频率计 LM317:输出电压连续可调的集成稳压电源,输出电压在1.25-37V之间连续可调,输出最大电流可达1.5A。

工作原理: 电路原理图见图1。LM317输出电流为1.5A,输出电压可在1.25-37V之间连续调节,其输出电压由两只外接电阻R1、RP1决定,输出端和调整端之间的电压差为1.25V,这个电压将产生几毫安的电流,经R1、RP1到地,在RP1上分得的电压加到调整端,通过改变RP1就能改变输出电压。注意,为了得到稳定的输出电压,流经R1的电流小于3.5mA。LM317在不加散热器时最大功耗为2W,加上 200×200×4mm3散热板时其最大功耗可达15W。VD1为保护二极管,防止稳压器输出端短路而损坏IC,VD2用于防止输入短路而损坏集成电路。 (a)图是红外发射电路.NE555电路产生40kHz的脉冲经过VT放大后由红外发射管SE303向外发射. 红外遥控延时灯开关电路:该电路由红外接收器,单稳态延时电路和可控硅组成。

常见芯片的功能描述

7400 TTL 2输入端四与非门 7401 TTL 集电极开路2输入端四与非门 7402 TTL 2输入端四或非门 7403 TTL 集电极开路2输入端四与非门 7404 TTL 六反相器 7405 TTL 集电极开路六反相器 7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门 7409 TTL 集电极开路2输入端四与门 7410 TTL 3输入端3与非门 74107 TTL 带清除主从双J-K触发器 74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门 74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门 74121 TTL 单稳态多谐振荡器 74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门 74136 TTL 四异或门 74138 TTL 3-8线译码器/复工器 74139 TTL 双2-4线译码器/复工器 7414 TTL 六反相施密特触发器 74145 TTL BCD—十进制译码/驱动器 7415 TTL 开路输出3输入端三与门 74150 TTL 16选1数据选择/多路开关 74151 TTL 8选1数据选择器 74153 TTL 双4选1数据选择器 74154 TTL 4线—16线译码器 74155 TTL 图腾柱输出译码器/分配器 74156 TTL 开路输出译码器/分配器 74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器 7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器 74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器 74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器 74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器 74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器 74185 TTL 二进制—BCD代码转换器 74190 TTL BCD同步加/减计数器 74191 TTL 二进制同步可逆计数器 74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器 74195 TTL 四位并行通道移位寄存器 74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器 7420 TTL 4输入端双与非门 7421 TTL 4输入端双与门 7422 TTL 开路输出4输入端双与非门 74221 TTL 双/单稳态多谐振荡器 74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器 74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器 74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器 74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门 74260 TTL 5输入端双或非门 74266 TTL 2输入端四异或非门 7427 TTL 3输入端三或非门 74273 TTL 带公共时钟复位八D触发器 74279 TTL 四图腾柱输出S-R锁存器 7428 TTL 2输入端四或非门缓冲器 74283 TTL 4位二进制全加器 74290 TTL 二/五分频十进制计数器 74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器 74298 TTL 四2输入多路带存贮开关 74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门 7432 TTL 2输入端四或门 74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器

常用系列芯片功能

常用4000系列芯片功能 CD4000 双3输入端或非门单非门 CD4001 四2输入端或非门 CD4002 双4输入端或非门 CD4006 18位串入/串出移位寄存器 CD4007 双互补对加反相器 CD4008 4位超前进位全加器 CD4009 六反相缓冲/变换器 CD4010 六同相缓冲/变换器 CD4011 四2输入端与非门 CD4012 双4输入端与非门 CD4013 双主-从D型触发器 CD4014 8位串入/并入-串出移位寄存器CD4015 双4位串入/并出移位寄存器 CD4016 四传输门 CD4017 十进制计数/分配器 CD4018 可预制1/N计数器 CD4019 四与或选择器 CD4020 14级串行二进制计数/分频器 CD4021 08位串入/并入-串出移位寄存器CD4022 八进制计数/分配器 CD4023 三3输入端与非门 CD4024 7级二进制串行计数/分频器 CD4025 三3输入端或非门 CD4026 十进制计数/7段译码器 CD4027 双J-K触发器 CD4028 BCD码十进制译码器 CD4029 可预置可逆计数器 CD4030 四异或门 CD4031 64位串入/串出移位存储器 CD4032 三串行加法器 CD4033 十进制计数/7段译码器 CD4034 8位通用总线寄存器 CD4035 4位并入/串入-并出/串出移位寄存CD4038 三串行加法器 CD4040 12级二进制串行计数/分频器 CD4041 四同相/反相缓冲器 CD4042 四锁存D型触发器 CD4043 三态R-S锁存触发器("1"触发) CD4044 四三态R-S锁存触发器("0"触发)

74ls系列芯片功能介绍

74、74HC、74LS系列芯片资料 系列电平典型传输延迟ns 最大驱动电流(-Ioh/Lol)mA AHC CMOS 8.5 -8/8 AHCT COMS/TTL 8.5 -8/8 HC COMS 25 -8/8 HCT COMS/TTL 25 -8/8 ACT COMS/TTL 10 -24/24 F TTL 6.5 -15/64 ALS TTL 10 -15/64 LS TTL 18 -15/24 注:同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。74LSxx的使用说明如果找不到的话,可参阅74xx或74HCxx的使用说明。有些资料里包含了几种芯片,如74HC161资料里包含了74HC160、74HC161、74HC162、74HC163四种芯片的资料。找不到某种芯片的资料时, 可试着查看一下临近型号的芯片资料。 7400 QUAD 2-INPUT NAND GATES 与非门 7401 QUAD 2-INPUT NAND GATES OC 与非门 7402 QUAD 2-INPUT NOR GATES 或非门 7403 QUAD 2-INPUT NAND GATES 与非门 7404 HEX INVERTING GATES 反向器 7406 HEX INVERTING GATES HV 高输出反向器 7408 QUAD 2-INPUT AND GATE 与门 7409 QUAD 2-INPUT AND GATES OC 与门 7410 TRIPLE 3-INPUT NAND GATES 与非门 7411 TRIPLE 3-INPUT AND GATES 与门 74121 ONE-SHOT WITH CLEAR 单稳态 74132 SCHMITT TRIGGER NAND GATES 触发器与非门 7414 SCHMITT TRIGGER INVERTERS 触发器反向器 74153 4-LINE TO 1 LINE SELECTOR 四选一 74155 2-LINE TO 4-LINE DECODER 译码器 74180 PARITY GENERATOR/CHECKER 奇偶发生检验 74191 4-BIT BINARY COUNTER UP/DOWN 计数器 7420 DUAL 4-INPUT NAND GATES 双四输入与非门 7426 QUAD 2-INPUT NAND GATES 与非门 7427 TRIPLE 3-INPUT NOR GATES 三输入或非门 7430 8-INPUT NAND GATES 八输入端与非门 7432 QUAD 2-INPUT OR GATES 二输入或门 7438 2-INPUT NAND GATE BUFFER 与非门缓冲器 7445 BCD-DECIMAL DECODER/DRIVER BCD译码驱动器 7474 D-TYPE FLIP-FLOP D型触发器 7475 QUAD LATCHES 双锁存器

CD4017 结构原理

CMOS集成电路CD4017C采用标准的双列直插式脚塑封,它的引脚排列如图1所示。CC4017 是国标型号,它与国外同类产品CD4017 在逻辑功能、引出端和电参数等方面完全相同,可以直接互换。其引脚功能如1: ①脚(Y5),第5输出端; ②脚(Y1),第1输出端; ③脚(Y0),第0输出端,电路清零时,该端为高电平; ④脚(Y2),第2输出端; ⑤脚(Y6).第6输出端; ⑥脚(y7),第7输出端; ⑦脚(Y3),第3输出端; ⑧脚(vss).电源负端; ⑨脚(Y8),第8输出端; ⑩脚(Y4).第4输出端; 脚(Y9).第9输出端; 脚(Qco),级联进位输出端,每输入 10 个时钟脉冲,就可得一个进位输出脉冲,因此进位输出信号可作为下一级计数器的时钟信号。 脚(EN),时钟输入端,脉冲下降沿有效; 脚(CP),时钟输入端.脉冲上升沿有效; 脚(R),清零输入端,在“R”端加高电平或正脉冲时,CD40171C 计数器中各计数单元输出低电平“0”,在译码器中只有对应“0”状态的输出端 Y0 为高电平; 脚(VDD),电源正端.3~18V 直流电压。 CD40171C 内部逻辑电原理图如图 1-2 所示。它是由十进制计数器电路和时序译码电路两部分组成。其中的 D 触发器 Fl~F5 构成了十进制约翰逊计数器,门电路 5~14 构成了时序译码电路。约翰逊汁数器的结构比较简单.它实质上是一种串行移位寄存器。除了第 3 个触发器是通过门电路15、16 构成的组合逻辑电路作用于 F3 的 D3 端以外,其余各级均是将前一级触发器的输出端连接到后一级触发器的输入端 D 的,计数器最后—级的 Q5 端连接到第一级的 D1 端。这种计数器具有编码可靠,工作速度快、译码简单,只需由二输入瑞的与门即可译码,且译码输出无过渡脉冲干扰等特点。通常只有译码选中的那个输出端为高电平,其余输出端均为低电平。约翰逊计数器状态如表1-1所示。

CD4017工作原理及应用电路图

CD4017工作原理及应用电路图 十进制计数/分频器CD4017,其内部由计数器及译码器两部分组成,由译码输出实现对脉冲信号的分配,整个输出时序就是O0、O1、O2、…、O9依次出现与时钟同步的高电平,宽度等于时钟周期。 CD4017有10个输出端(O0~O9)和1个进位输出端~O5-9。每输入10个计数脉冲,~O5-9就可得到1个进位正脉冲,该进位输出信号可作为下一级的时钟信号。 CD4017有3个输(MR、CP0和~CP1),MR为清零端,当在MR端上加高电平或正脉冲时其输出O0为高电平,其余输出端(O1~O9)均为低电平。CP0和~CPl是2个时钟输入端,若要用上升沿来计数,则信号由CP0端输入;若要用下降沿来计数,则信号由~CPl端输入。设置2个时钟输入端,级联时比较方便,可驱动更多二极管发光。 由此可见,当CD4017有连续脉冲输入时,其对应的输出端依次变为高电平状态,故可直接用作顺序脉冲发生器。 CD4017方框图 CD4017引脚图

一、用一个CD4017制成的彩灯电路 1.用一个CD4017制作的彩灯电路如图1 所示。 CD4017电路图 2.电路工作原理 CD4017输出高电平的顺序分别是③、②、④、⑦、⑩、①、⑤、⑥、⑨脚,故③、②、④、⑦、⑩、①脚的高电平使6串彩灯向右顺序发光,⑤、⑥、③脚的高电平使6串彩灯由中心向两边散开发光。各种发光方式可按自己的需要进行具体的组合,若要改变彩灯的闪光速度,可改变电容C1的大小。 二、用三个CD4O17彩灯电路图 CD4017的级连,如图2所示。 CD4017原理图电路 CD4017级连后可以顺序输出24个高电平,同上理可组合出各种不同的发光方式,见图3,可使6串彩灯向右流水发光,再向左流水发光,中心向两边散开后再向中心靠拢发光,1、3、 5、2、4、6串间隔发光等等

各种芯片功能表,很实用的

各种芯片功能表,很实用的 贴子发表于:2008/4/27 13:03:51 74系列:: 74LS00 TTL 2输入端四与非门 74LS01 TTL 集电极开路2输入端四与非门74LS02 TTL 2输入端四或非门 74LS03 TTL 集电极开路2输入端四与非门74LS04 TTL 六反相器 74LS05 TTL 集电极开路六反相器 74LS06 TTL 集电极开路六反相高压驱动器74LS07 TTL 集电极开路六正相高压驱动器74LS08 TTL 2输入端四与门 74LS09 TTL 集电极开路2输入端四与门 74LS10 TTL 3输入端3与非门 74LS107 TTL 带清除主从双J-K触发器 74LS109 TTL 带预置清除正触发双J-K触发器74LS11 TTL 3输入端3与门 74LS112 TTL 带预置清除负触发双J-K触发器74LS12 TTL 开路输出3输入端三与非门 74LS121 TTL 单稳态多谐振荡器 74LS122 TTL 可再触发单稳态多谐振荡器 74LS123 TTL 双可再触发单稳态多谐振荡器74LS125 TTL 三态输出高有效四总线缓冲门74LS126 TTL 三态输出低有效四总线缓冲门74LS13 TTL 4输入端双与非施密特触发器74LS132 TTL 2输入端四与非施密特触发器74LS133 TTL 13输入端与非门 74LS136 TTL 四异或门 74LS138 TTL 3-8线译码器/复工器 74LS139 TTL 双2-4线译码器/复工器 74LS14 TTL 六反相施密特触发器 74LS145 TTL BCD—十进制译码/驱动器 74LS15 TTL 开路输出3输入端三与门 74LS150 TTL 16选1数据选择/多路开关

- CD4017资料

- CC4017

- CD4017工作原理及应用电路图

- 常用系列芯片功能

- 46 MN4017芯片在遥控开关中的应用

- 74系列芯片功能大全

- 各种芯片功能表

- 芯片功能大全

- 74ls系列芯片功能和参数详细介绍

- CD4017中文资料_数据手册_参数

- 数字电路CD4017的原理及应用电路

- 常用芯片功能

- CD4017 结构原理

- 74系列芯片功能大全

- ITCP4017数据采集用户手册

- CD4017引脚图,引脚功能及工作时序图

- 系列芯片功能大全

- 常见芯片的功能描述

- 各种芯片代号及作用

- ITCP-4017数据采集用户手册

- 初三年级德育课程之主题班会

- 主题班会——学校德育工作的主阵地-模板

- 中小学班主任老师德育主题班会,PPT课件大全(中小学班主任用)

- 德育教育主题班会

- 学校德育工作总结ppt模板

- 远离浮躁,静心学习主题班会设计

- 德育工作实施方案6篇

- 德育活动方案

- 2023年学校德育活动方案(精选4篇)

- 学校德育活动方案(精选5篇)

- 学校德育活动的方案(8篇)

- 学校德育的主题活动方案(精选10篇)

- 学校德育课程活动策划方案五篇(最新)

- 学校德育活动实施方案(精选10篇)

- 学校德育教育工作实施方案3篇

- 学校德育工作实施方案10篇

- 学校德育工作的实施方案(通用10篇)

- 学校德育活动方案(通用5篇)

- 学校德育实施工作方案(通用8篇)

- 学校德育活动开展方案(精选12篇)