Design of unequal Wilkinson power divider for dual-band operation with isolation stubs

Design of unequal Wilkinson power divider for dual-band operation with isolation stubs X.Li,Y.-J.Yang,L.Yang,S.-X.Gong,T.Hong,X.Chen and Y.-J.Zhang

The design of a novel unequal Wilkinson power divider for dual-band

operation is presented.The isolation stubs are introduced to reduce the

parasitic effects between the two stubs that are connected by the iso-

lation resistor.Closed-form design equations are derived based on

network theory.The validity of this analysis is con?rmed through

the design,simulation and experimental results for a power divider

for1and2.5GHz.

Introduction:Power dividers are frequently used in the design of micro-wave circuits.Owing to the trend of dual-band or multiband communi-cations,we can see a worldwide effort to develop dual-band or multiband power dividers[1–3].However,most of these cannot satisfy the unequal power dividing ratio.For the proposed unequal Wilkinson power divider[4],the single-frequency property is still a de?ciency.Moreover,the media transmission lines in these power divi-ders are placed close to each other,and as a result,the parasitic effects between transmission lines will be increased when the operating fre-quency becomes higher[5].Isolation stubs are introduced to deal with equal power dividers in[6].

In this Letter,a novel unequal power divider circuit for dual-band operation is introduced.Its main advantages include:(a)no extra lumped elements are needed for the dual-band operation other than a single resistor.A structure consisting of isolation stubs is?rst introduced in the unequal power divider,which means that the power divider can be fabricated easily and the parasitic effects can be greatly reduced.(b) Open stubs and short stubs can be chosen?exibly.For veri?cation, both simulated and experimental results of a dual-band power divider are given.

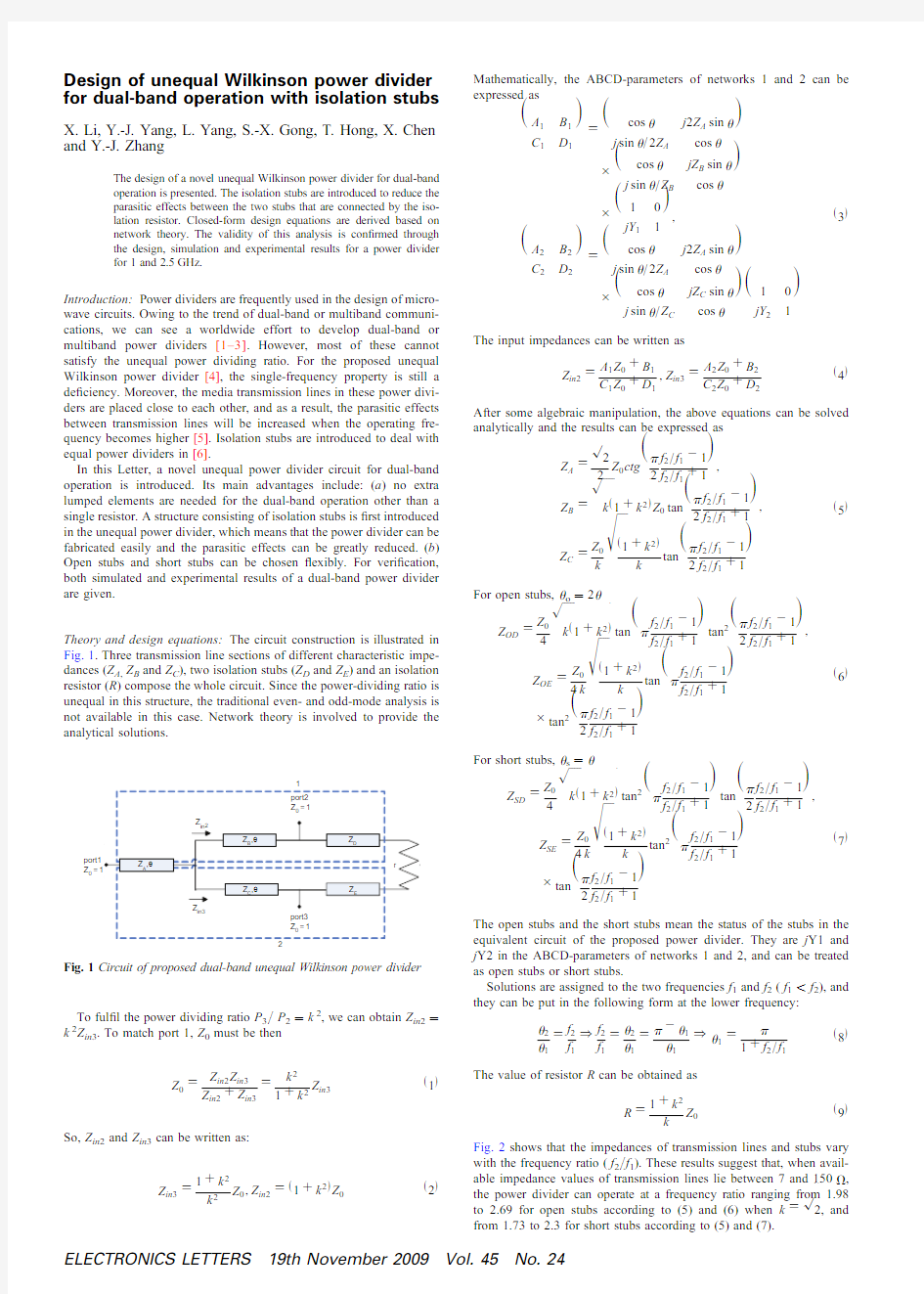

Theory and design equations:The circuit construction is illustrated in Fig.1.Three transmission line sections of different characteristic impe-dances(Z A,Z B and Z C),two isolation stubs(Z D and Z E)and an isolation resistor(R)compose the whole circuit.Since the power-dividing ratio is unequal in this structure,the traditional even-and odd-mode analysis is not available in this https://www.wendangku.net/doc/1c11666438.html,work theory is involved to provide the analytical solutions.

Z

=

Fig.1Circuit of proposed dual-band unequal Wilkinson power divider

To ful?l the power dividing ratio P3/P2?k2,we can obtain Z in2?k2Z in3.To match port1,Z0must be then

Z0?

Z in2Z in3

Z in2tZ in3

?

k2

1tk2

Z in3e1T

So,Z in2and Z in3can be written as:

Z in3?1tk2

k2

Z0;Z in2?e1tk2TZ0e2T

Mathematically,the ABCD-parameters of networks1and2can be

expressed as

A1B1

C1D1

?

cos u j2Z A sin u

j sin u=2Z A cos u

?

cos u jZ B sin u

j sin u=Z B cos u

?

10

jY11

;

A2B2

C2D2

?

cos u j2Z A sin u

j sin u=2Z A cos u

?

cos u jZ C sin u

j sin u=Z C cos u

10

jY21

e3T

The input impedances can be written as

Z in2?

A1Z0tB1

C1Z0tD1

;Z in3?

A2Z0tB2

C2Z0tD2

e4T

After some algebraic manipulation,the above equations can be solved

analytically and the results can be expressed as

Z A?

???

2

p

Z0ctg

p f2=f1à1

21

;

Z B?

???????????????????

ke1tk2T

p

Z0tan

p

2

f2=f1à1

f2=f1t1

;

Z C?

Z0

k

????????????????

e1tk2T

k

s

tan

p

2

f2=f1à1

f2=f1t1

e5T

For open stubs,u o?2u

Z OD?

Z0

4

???????????????????

ke1tk2T

p

tan p

f2=f1à1

f2=f1t1

tan2

p

2

f2=f1à1

f2=f1t1

;

Z OE?

Z0

4k

????????????????

e1tk2T

k

s

tan p

f2=f1à1

f2=f1t1

?tan2

p

2

f2=f1à1

f2=f1t1

e6T

For short stubs,u s?u

Z SD?

Z0

4

???????????????????

ke1tk2T

p

tan2p

f2=f1à1

f2=f1t1

tan

p

2

f2=f1à1

f2=f1t1

;

Z SE?

Z0

4k

????????????????

e1tk2T

k

s

tan2p

f2=f1à1

f2=f1t1

?tan

p

2

f2=f1à1

f2=f1t1

e7T

The open stubs and the short stubs mean the status of the stubs in the

equivalent circuit of the proposed power divider.They are j Y1and

j Y2in the ABCD-parameters of networks1and2,and can be treated

as open stubs or short stubs.

Solutions are assigned to the two frequencies f1and f2(f1,f2),and

they can be put in the following form at the lower frequency:

u2

1

?

f2

1

)

f2

1

?

u2

1

?

pàu1

1

)u1?

p

21

e8T

The value of resistor R can be obtained as

R?

1tk2

k

Z0e9T

Fig.2shows that the impedances of transmission lines and stubs vary

with the frequency ratio(f2/f1).These results suggest that,when avail-

able impedance values of transmission lines lie between7and150V,

the power divider can operate at a frequency ratio ranging from1.98

to2.69for open stubs according to(5)and(6)when k?

???

2

p

,and

from1.73to2.3for short stubs according to(5)and(7).

ELECTRONICS LETTERS19th November2009Vol.45No.24

1601401201008060402001.0

2.0 2.1 2.2

2. 3a b

2.4 2.5 2.6 2.7Z A Z B Z C Z O D Z O E

Z A Z B Z C Z S D Z S E

16014012010080l i n e i m p e d a n c e , 6040200

1.7 1.8 1.9

2.0 2. 1

f

2/f 1

f 2/f 1

2.2 2.3

Fig.2Circuit parameters against frequency

ratio when k ?p

2a Open stubs b Short stubs

Fig.3Photograph of fabricated power divider

0.5

–30–25–20o u t p u t r e t u r n l o s s , d B –15–10–50 1.0

1.5

2.0frequency, GHz

c

a

b

2.5

3.0

0.5

–30–25–20i n p u t r e t u r n l o s s a n d i s o l a t i o n , d B

–15–10–50 1.0

1.5

2.0frequency, GHz

2.5

3.00.5

–30–25–20t r a n s m i s s i o n ,

d B –15–10–50 1.0

1.5

2.0frequency, GHz

2.5

3.0

measured S 31

measured S 21stimulated S 21stimulated S 31measured S 33

measured S 22stimulated S 22stimulated S 33

measured

S 32

measured S 11stimulated S 11stimulated S 32Fig.4Frequency response of designed dual-band power divider a Simulated and measured input return loss b Transmission

c Simulate

d and measured output return loss

Experiment:The dual-band Wilkinson power divider has been fabri-cated on a substrate with thickness of 1mm and relative dielectric con-stant of 2.65.The power divider has been designed for f 1?1GHz and f 2?2.5GHz.The design parameters were calculated ?rst.According to (8),u ?51.48at the lower frequency (f 1).Using (5),the line impedance values are Z A ?44V ,Z B ?82V and Z C ?41V .From (6),Z D ?72V and Z E ?36V for open stubs.Fig.3shows a photo of the fabricated power divider,which occupies a size of 145?60mm.The measured S -parameter data collected from a WILTRON37269A network analyser along with simulated results using HFSS are presented in Fig.4.There is a good agreement between the simulated and measured results with the dual-band operation at 1and 2.5GHz.The return loss is 225.22dB at 1GHz and 218.03dB at 2.5GHz.The measured S 21is 24.35dB at 1GHz and 24.99dB at 2.5GHz,S 31is 21.93dB at 1GHz and 21.94dB at 2.5GHz.The isolation between ports 2and 3is 17.35dB at 1GHz and 15.02dB at 2.5GHz,respectively.It is found that the transmission values are not ideal 3dB.This small difference is mainly due to the neglect of substrate losses and the approximate values of components.

Conclusions:The design and analysis of a dual-band unequal Wilkinson power divider are presented.The isolation stubs are intro-duced in order to reduce the parasitic effects.Furthermore,open stubs and short stubs can be chosen ?exibly.The formulas used to determine the design parameters are given.The theoretical design is veri?ed through measurement on the real circuit.

#The Institution of Engineering and Technology 200930July 2009

doi:10.1049/el.2009.2137

X.Li,Y.-J.Yang,L.Yang,S.-X.Gong,T.Hong,X.Chen and Y.-J.Zhang (National Key Laboratory of Antennas and Microwave Technology,Xidian University,Xi’an,Shaanxi 710071,People’s Republic of China )E-mail:xixi1928@https://www.wendangku.net/doc/1c11666438.html, References

1Cameron,R.J.,Yu,M.,and Wang,Y.:‘Direct-coupler microwave ?lters with single and dual stopbands’,IEEE Trans.Microw.Theory Tech.,2005,53,pp.3288–3297

2Park,M.J.,and Lee,B.:‘A dual-band Wilkinson power divider’,IEEE https://www.wendangku.net/doc/1c11666438.html,pon.Lett.,2008,18,pp.85–87

3Cheng,K.K.M.,and Law,C.:‘A novel approach to the design and implementation of dual-band power divider’,IEEE Trans.Microw.Theory Tech.,2008,56,pp.487–492

4Chen,J.X.,and Xue,Q.:‘Novel 5:1unequal Wilkinson power divider using offset double-sided parallel-strip lines’,IEEE https://www.wendangku.net/doc/1c11666438.html,pon.Lett.,2007,17,pp.175–177

5Horst,S.,Bairavasubramanian,R.,Tentzeris,M.M.,and Papapolymerou,J.:‘Modi?ed Wilkinson power dividers for millimeter-wave integrated circuits’,IEEE https://www.wendangku.net/doc/1c11666438.html,pon.Lett.,2007,55,pp.2439–24466Wu,Y.,Liu,Y.,and Liu,X.:‘Dual-frequency power divider with isolation stubs’,Electron.Lett.,2008,44,pp.1407–1408

ELECTRONICS LETTERS 19th November 2009Vol.45No.24

PowerDesign图文教程

PowerDesign 6简易介绍 --taoqing 建立一个新table (1) 定义或修改表名/表结构 (2) 生成table sql script(脚本) (4) 其他 (5) 定义表索引 (5) 常用功能介绍 (5) 建立一个新table 图示 1 点击箭头所示图标,然后再点击绿色区域,一张空table即出现在屏幕上。如果需要产生多张空白table,则在绿色区域继续点击。结束产生空白table可点击Mouse右键,此时Mouse 指示会恢复为箭头形状。

定义或修改表名/表结构 图示 2 双击你需要修改的表,在弹出的窗口(图示3),定义两处内容:(Name用中文英文以便查询写程序的时候方便,Code即是你最终会产生的table name) 图示 3

点击图示 3 中的按钮[Columns] 注: (1) 表示是否为primary Key ,即主关键字 (2) 表示是否不允许为Null (即Not Null 选项) 对于需要有Default 值的字段,可以点击按钮[CHECK],例如定义”录入日期inputdate”的默认值为当前日期:

生成table sql script(脚本) 选择你需要产生的table: 1.按住用Mouse左键,然后在powerdesign绿色区域移动,可以选择多张table; 2.可以按住shift键,用Moues点击以选择多个table。 选择菜单[Database]-[Generate Database ….]或按热键Ctrl + G,出现下图: 点击[Generate Script]按钮,选择[YES],[YES],最终看到产生的脚本如下:

(完整word版)PowerDesigner16.5中文教程-数据库模型操作教程

PowerDesigner16.5中文教程-数据库模型操作教程 目录 使用POWERDESIGNER软件创建数据库概述 (2) 2 1、概念数据模型(CDM)(C ONCEPTUAL D ATA M ODEL) ............................................................................... 2 2、逻辑数据模型(LDM)................................................................................................................................... 3、物理数据模型(PDM)(P HYSICAL D ATA M ODEL)-最主要和常用的数据库模型 (3) 3 4、面向对象模型(OOM)(O BJCET O RIENTED M ODEL).......................................................................... 3 5、业务程序模型(BPM)(B USINESS P ROCESS M ODEL)......................................................................... 3 6、信息流模型(ILM)...................................................................................................................................... 3 7、企业架构模型(EAM):............................................................................................................................. 创建数据模型 (3) 3 1、创建概念数据模型 ........................................................................................................................................ 2、创建物理数据模型 (14) 模型转换 (27) 1、概念模型转为物理模型 (27) 2、物理模型转概念模型 (29) 3、不同数据库之间的转化 (30) 导入导出SQL脚本 (31) 1、物理模型导出SQL语句(生成SQL脚本) (31) 2、导入SQL脚本(反向工程)生成相应的数据库表模型图 (34) 由物理模型生成对象模型,并生成相应的GET、SET方法 (35) 建立索引、视图、存储过程 (37) 1、建立索引 (37) 2、建立视图 (39) 3、建立存储过程 (41) 生成数据库文档(开发的数据库设计文档) (42) 常规配置 (43) 1、默认字体太小,修改为10号字 (43) 2、将所有名词转化为大写 (44) 3、修改表的字段N AME的时候,C ODE不自动跟着变 (45)

quartusII图形设计过程教程

Quartus II 的使用 (2) 1 工程建立 (2) 2 原理图的输入 (5) 3 文本编辑(verilog) (15) 4 波形仿真 (16)

Quartus II 的使用 在这里,首先用最简单的实例向读者展示使用Quartus II软件的全过程。进入WINDOWS XP后,双击Quartus II图标,屏幕如图1.1所示。 图 1.1 Quartus II 管理器 1.1 工程建立 使用New Project Wizard,可以为工程指定工作目录、分配工程名称以及指定最高层设计实体的名称。还可以指定要在工程中使用的设计文件、其它源文件、用户库和EDA 工具,以及目标器件系列和器件(也可以让Quartus II 软件自动选择器件)。 建立工程的步骤如下:

(1)选择File菜单下New Project Wizard ,如图1.2所示。 图 1.2 建立项目的屏幕 (2)输入工作目录和项目名称,如图1.3所示。可以直接选择Finish,以下的设置过程可以在设计过程中完成。 图 1.3 项目目录和名称

(3)加入已有的设计文件到项目,可以直接选择Next,设计文件可以在设计过程中加入,如图1.4所示。 图 1.4 加入设计文件 (4)选择设计器件,如图1.5所示。 图 1.5 选择器件

(5)选择第三方EDA综合、仿真和时序分析工具,如图1.6所示。 图 1.6 选择EDA 工具 (6)建立项目完成,显示项目概要,如图1.7所示。 图 1.7 项目概要 1.2 原理图的输入 原理图输入的操作步骤如下:

(1)选择File 菜单下New ,新建图表/原理图文件,如图1.8 所示。 图 1.8 新建原理图文件 (2)在图1.9的空白处双击,屏幕如图1.10所示: (3)在图1.10的Symbol Name 输入编辑框中键入dff后,单击 ok按钮。此时可看到光标上粘着被选的符号,将其移到合 适的位置(参考图 1.11)单击鼠标左键,使其固定; (4)重复(2)、(3)步骤,给图中放一个input、not、output 符号,如图1.11所示;在图1.11中,将光标移到右侧input 右侧待连线处单击鼠标左键后,再移动到D触发器的左侧 单击鼠标左键,即可看到在input和D触发器之间有一条 线生成;

Quartus_II使用教程-完整实例

Quartus Ⅱ入门教程 (一个Verilog 程序得编译与功能仿真) Quartus Ⅱ 就是Altera 公司推出得专业EDA 工具,支持原理图输入、硬件描述语言得输入等多种输入方式。硬件描述语言得输入方式就是利用类似高级程序得设计方法来设计出数字系统。接下来我们对这种智能得EDA 工具进行初步得学习。使大家以后得数字系统设计更加容易上手。 第一步:打开软件 快捷工具栏:提供设置(setting),编译(pile)等快捷方式,方便用户使用,用户也可以在菜单栏得下拉菜单找到相应得选项。● 菜单栏:软件所有功能得控制选项都可以在其下拉菜单中找到。 ● 信息栏:编译或者综合整个过程得详细信息显示窗口,包括编译通过信息与报错信息。 第二步:新建工程( Project Wizard ) 1 工程名称: 快捷工具栏 菜单栏 所建工程得保存路径 工作区 资源管理窗口 任务管理窗口

dqgxo 。 2添加已有文件(没有已有文件得直接跳过next ) 3 选择芯片型号(我们选择MAX3000A 系列下得EPM3256AQC208-10芯片) (注:如果不下载到开发板上进行测试,这一步可以不用设置) 工程名称 顶层模块名(芯片级设计为实体名),要求与工程名称相同 如果有已经存在得文 件就在该过程中添加, 软件将直接将用户所添加得文件添加到工程中。

4 选择仿真,综合工具(第一次实验全部利用quartus 做,三项都选None,然后next) 5 工程建立完成(点finish ) 所选得芯片得系列型号 快速搜索所需得芯片 选择芯片 选择第三方综合工具,如果使用Quartus 内部综合工具则选择none 选择第三方仿真工具,如果使用Quartus 内部仿真工具则选择none 选择时序分析仪

powerdesigner使用心得

PowerDesigner使用心得 PowerDesigner想必没人不知道吧?著名的CASE工具,目前最新版本为15.2,用于软件建模,可以从需求直到物理模型,支持UML2.0语法,可用于UML图绘制。最大特色是能够使设计到实现无缝衔接,如:概念模型->逻辑模型->物理模型,概念模型->OOM,而且能够生成多种DBMS的脚本或代码脚本。 1 name/code默认总是一起修改,很烦躁,在tool ->general options,取消即可。 2 概念模型->物理模型转换,会为“1对1”关系自动生成两条引用,每次都要手工删除,很麻烦。在概念模型中为关系指定dominant role即可。

3 设定计算列,在物理模型中选择某个列,勾选computed,然后在detail中设置计算表达式即可 修改表达式,可引用表中的其他列。

4 设定列中数据为自增量类型,勾选列属性中的identity。 5 修改某个列的数据类型后,使用它做外键的表中相应数据类型并不会变化,如果被引用的地方多,那修改起来可是一个大工程,而且容易出错,此时可在check model设置为自动修正。

6 PD无法直接生成GUID类型的测试数据,GUID 的格式为“xxxxxxxx-xxxx-xxxx-xxxx-xxxxxxxxxxxx”,其中每个 x 是 0-9 或 a-f 范围内的一个十六进制的数字。例如: 6F9619FF-8B86-D011-B42D-00C04FC964FF 即为有效的 GUID 值。默认DBMS配置文件有问题,需要修改数据类型为VA36(= varchar(36) )、长度为36位( 32位16进制数字 + 4个“-”)。Database->edit current DBMS,修改PhysDataType中uniqueidentifier的内容为VA36.也可下载补丁: https://www.wendangku.net/doc/1c11666438.html,/source/2284780

QuartusII教程(完整版)

Quartus II 的使用 (1) 1 工程建立 (1) 2 原理图的输入 (4) 3 文本编辑(verilog) (14) 4 波形仿真 (17)

Quartus II 的使用 在这里,首先用最简单的实例向读者展示使用Quartus II软件的全过程。进入WINDOWS XP后,双击Quartus II图标,屏幕如图1.1所示。 图 1.1 Quartus II 管理器 1.1 工程建立 使用New Project Wizard,可以为工程指定工作目录、分配工程名称以及指定最高层设计实体的名称。还可以指定要在工程中使用的设计文件、其它源文件、用户库和EDA 工具,以及目标器件系列和器件(也可以让Quartus II 软件自动选择器件)。 建立工程的步骤如下:

(1)选择File菜单下New Project Wizard ,如图1.2所示。 图 1.2 建立项目的屏幕 (2)输入工作目录和项目名称,如图1.3所示。可以直接选择Finish,以下的设置过程可以在设计过程中完成。 图 1.3 项目目录和名称

(3)加入已有的设计文件到项目,可以直接选择Next,设计文件可以在设计过程中加入,如图1.4所示。 图 1.4 加入设计文件 (4)选择设计器件,如图1.5所示。 图 1.5 选择器件

(5)选择第三方EDA综合、仿真和时序分析工具,如图1.6所示。 图 1.6 选择EDA 工具 (6)建立项目完成,显示项目概要,如图1.7所示。 图 1.7 项目概要 1.2 原理图的输入 原理图输入的操作步骤如下:

(1)选择File 菜单下New ,新建图表/原理图文件,如图1.8 所示。 图 1.8 新建原理图文件 (2)在图1.9的空白处双击,屏幕如图1.10所示: (3)在图1.10的Symbol Name 输入编辑框中键入dff后,单击ok按钮。此时可看到光标上粘着被选的符号,将其移到合适的位置(参考图 1.11)单击鼠标左键,使其固定;(4)重复(2)、(3)步骤,给图中放一个input、not、output 符号,如图1.11所示;在图1.11中,将光标移到右侧input 右侧待连线处单击鼠标左键后,再移动到D触发器的左侧单击鼠标左键,即可看到在input和D触发器之间有一条线生成;

[PowerDesign]数据库设计:需求模型(RQM)的简单介绍与案例教程(二)

汪海的实验室 - - 各种图形学实验和数据结构实验以及其他一切琐碎杂乱的小笔记们都相遇在此齐聚一堂共同守候 0 error(s), 0 warning(s) 这神奇时刻的到来 [PowerDesign]数据库设计:需求模型(RQM)的简单介绍与案例教程(二) 分类: PowerDesign数据库 2013-02-15 18:07 98人阅读 评论(0) 收藏举报 上一章:[PowerDesign]数据库设计:需求模型(RQM)的简单介绍与案例教程(一) 定义Users和Groups Users(用户) 指在一个需求模型中至少和一个已定义需求有关的人的集合。 Groups(组) 指专属于开发进程中一个或多个方面的用户类别。每个用户组要与需求模型中至少一个已定义需求有关。 新建User/Group 在资源浏览窗口中,右键单击模型名称(图标)-->New--> User,打开User属性窗口: 输入相应名称和代码名,确定即完成新建。

同样也可在菜单栏选择”Model”-->Users完成新建过程。 在资源浏览窗口中,右键单击模型名称(图标)-->New--> Group,打开Group窗口创建一个新的用户组:

下一步是将相应的User与Group联系,添加进Group中。 打开相应的Group属性,选择Group Users属性栏。 点击属性工具栏中”Add Objects”工具,从中选择您要添加的User对象,当然只有在您已经建立了相应的User对象

时才会显示User成员列表。 现在选择您需要添加的User对象,确定就可以了。 建立Business rules(业务规则) 业务规则是对为了满足业务需求,模型应该包括的特定内容或关于如何构建模型方面的描述清单。 在这里的示例模型中,我们要定义关于论坛积分制度的业务规则。 在Requirement Model状态下,PowerDesgner默认Businss为不可用状态,为此我们需要通过新建 Extended model definition(扩展模型定义)来激活Business rules。 步骤如下: 选择菜单栏 Model-->Extended Model Definitions,这时打开List of Extended Model Definitions,通过选择其工具栏中”Add a Row”工具,如下图: 点击AddRow,添加一行:

FPGA入门及Quartus II使用教程(内部资料)

FPGA入门及Quartus II使用教程FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在可编程阵列逻辑PAL(Programmable Array Logic)、门阵列逻辑GAL(Gate Array Logic)等可编程器件的基础上上进一步发展的产物。 可以这样讲,ASIC(Application Specific Integrated Circuit )内部的所有资源,是用积木堆积起来的小房子,可以是一个欧美风情的房子,还可以是一个北京四合院…….而FPGA内部就可以说是一个个小积木,也就是内部有大量的资源提供给我们,根据我们的需求进行内部的设计。并且可以通过软件仿真,我们可以事先验证设计的正确性。 第一章FPGA的基本开发流程 下面我们基于Altera 公司的QuantusII 软件来说明FPGA 的开发流程。 下图是一个典型的基于Quartus II的FPGA开发整体流程框图。

1、建立工程师每个开发过程的开始,Quartus II以工程为单位对设计过程进行管 理。 2、建立顶层图。可以这样理解,顶层图是一个容器,将整个工程的各个模块包 容在里边,编译的时候就将这些模块整合在一起。也可以理解为它是一个大元件,比如一个单片机,内部包含各个模块,编译的时候就是生成一个这样的大元件。 3、采用ALTERA公司提供的LPM功能模块。Quartus软件环境包含了大量的常 用功能模块,比如计数器、累加器、比较器等等。 4、自己建立模块。由于有些设计中现有的模块功能不能满足具体设计的要求, 那就只能自己设计。使用硬件描述语言,当然也可以用原理图的输入方法,可以独立的把它们当成一个工程来设计,并且生成一个模块符号(Symbol),类似于那些LPM功能模块。这里可以理解为,如果我们需求的滤波器,没有现成的合适的,那我们可以通过LC自己来搭建一个滤波器。 5、将顶层图的各个功能模块连线起来。这个过程类似电路图设计,把各个芯片 连起来,组成电路系统。 6、系统的功能原理图至此已经基本出炉了,下一步就是选择芯片字载体,分配 引脚,设置编译选项等等。 7、编译。这个过程类似软件开发里德编译,但是实际上这个过程比软件的编译 复杂的多,因为它最终要实现硬件里边的物理结构,包含了优化逻辑的组合,综合逻辑以及布线等步骤。 8、编译后会生成2个文件,一个是*.sof文件,一个是*.pof文件,前者可以通过 JTAG方式下载到FPGA内部,可以进行调试,但断电后数据丢失;后者通过AS或者PS方式下载到FPGA的配置芯片里边(EEPROM或者FLASH),重新上电后FPGA会通过配置将数据读出。 9、对于复杂的设计,工程编译好了,我们可以通过Quartus软件或者其他仿真 软件来对设计进行反复仿真和验证,直到满足要求。(主要是时序仿真)。 第二章基于Quartus II的实例 一、建立工程 首先,打开Quartus II软件。

学习PowerDesigner创建物业系统概括的心得体会

第一篇、PowerDesigner基础学习 学习PowerDesigner创建物业系统概括的心得体会 第二篇、PowerDesigner学习--概要介绍 学习PowerDesigner创建物业系统概括的心得体会 选项设置进行改变)。在一个模型当中,实体的名字不能重复。 Code在模型转化时一般作为对象的物理名称,比如把实体属性的Code转化为数据库中的列名,当然我们现在不必为了这个实体将来叫什么而费神,一般采取与Name一致即可。Generate默认是选择状态,如果取消,则在转化为其他模型时,会忽略这个实体。 Attributes 项目 窗口中下面表格里的各项很类似于一个表结构的定义,但数据类型是经过抽象化的,采用独立的表示方法,不与任何一个具体的数据库系统相关。

在此项目中为当前实体添加属性。 后面的三列CheckBox分别代表? ? ? M此属性不允许为空值P此属性为主键标识D为可显示属性 按“Crtl+U”呼出“定制列过滤器”的窗口,可以根据自己的喜好和实际需要选择那些列出现在窗口中,那些隐藏。使用快捷键“Crtl+E”可以允许或者禁止当前过滤器。 定义关系双击关系(Relationship)的符号,进入关系的属性页, 一般最好为关系取一个贴切的名字,本例的业务关系描述如下一个部门有多个员工,我们使用“Has”作为这个关系的名字。 同样的我们也可以描述为多个员工属于一个部门,可不可以使用“Belong to”作为关系名字呢?一般不推荐这样做,在概念图中有一个约定,关系的名字采用从“1,n”中“1”所在的 方向向“n”所在一方进行读取的语义。本例即“1”在部门一方,从部门

PowerDesigner教程(完整)

前言 在CSDN上转悠经常看到有网友寻求PowerDesigner相关资料的帖子,Baidu,Google上找找还真很少;同时也有不少网友发来Email询问相关PowerDesigner问题或索要相关资料的,故下定决心制作本文档。折腾二十多天,终于输出了现在的文档,其中绝大部分内容都是依照PowerDesigner自带的帮助文档翻译过来,乐意啃英文的朋友最好还是看其”原汁”教程,同时本文档仅用于帮助分析设计人员更快熟悉掌握PowerDesigner的使用方法,不包含分析设计方面的理论,所以要作好系统的分析设计工作还是需要用户深厚的项目实践功底。 起初想尽量按照PowerDesigner自带帮助文档完整地进行,尝试了一上午的工作之后这种方案马上就被我否决,原因有二:1.内容太多,工作量太多。2.原帮助文档特别周全,个人觉得可以在内容上作很大程度的压缩。姑决定按原帮助文档写,同时加入自己目前正在做的技术论坛分析设计过程以便于理解。 对本文档内容的几点说明: 1.本文档只包括PowerDesigner部分内容(RQM,Report,CDM,PDM),内容不够全面。 2.内容尽量简略,一些相同或类似操作过程尽量不再重复。 3.部分术语参考了飞思科技产品研发中心监制电子工业出版社的《PowerDesigner数据库系统分析设计与应用》。 4.暂时没有包含OOM,XML,BPM,ILM等模型内容,我将会在后期陆续更新。 版本说明:我使用的是PowerDesigner Trial 11英文版,因此文档中一些菜单,按钮名称也用英文写出(因当心自己译出的名称和中文版上的名称不一致而造成理解不便),若是给使用中文版的朋友带来不便,我在这说声”抱歉”了!同时由于各版本不同部分操作可能会有所区别。 这里要感谢在我进行翻译工作期间给我发送Email关注的网友,感谢一直支持我的朋友们!由于第一次做翻译工作,限于水平有限,文档中肯定存在很多不足和错误之处,衷心欢迎各位网友指点迷津,期望得到您的指导! Email:dingchungao@https://www.wendangku.net/doc/1c11666438.html, dingchungao@https://www.wendangku.net/doc/1c11666438.html, QQ:330982401 Blog:http:\\https://www.wendangku.net/doc/1c11666438.html, Slash 2006.8.31 需求模型 PowerDesigner11.0.0.1363评估版 为了更好的将原文含义再现,不加入我个人语言习惯,我尽量按照原文档内容翻译。 环境简介

QuartusII入门详细教程实例讲解

Quartus II入门详细教程实例讲解 写在前面: 1.本教程适合以前没有接触过QuartusII开发软件的新手,本教程是基础的入门,后续的学习还得大家自己努力。 2.本教程非常详细手把手带大家入门,网上现存的很多教程,有的过于跳跃,难以跟上;有的遇到错误,但教程没有指出,导致我们不知道怎么做。 3.本教程首先通过简单的仿真实验带大家入门。VHDL源代码会附在文档最后。 4.本教程使用Quartus II 9.1版本进行演示,其他版本的操作差别不是太大,也可以进行学习。 目录 一、Quartus II开发软件基本介绍 1.1 Quartus Ⅱ简介 Quartus Ⅱ是Altera公司推出的专业EDA工具,支持原理图输入、硬件描述语言的输入等多种输入方式。硬件描述语言的输入方式是利用类似高级程序的设计方法来设计出数字系统。 1.2 Quartus Ⅱ开发流程 使用Quartus II 软件进行开发的流程如图1.2.1所示。需注意的是,Quartus II还可以使用命令行模式的TCL批处理脚本进行自动流程控制。

图1.2.1 Quartus Ⅱ开发流程 二、用3-8译码器的设计介绍QuartusⅡ的基本使用方法(VHDL仿真) 1.1打开软件 双击桌面安装好的QuartusⅡ 9.1图标,打开软件,主页面如图1所示。 图1 在图1中,1区为菜单栏:软件所有功能的控制选项都可以在其下拉菜单中找到。2区为快捷工具栏:提供设置(setting),编译(compile)等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。3区为资源管理窗口。4区为编译及综合的进度栏:编译和综合的时候该窗口可以显示进度,当显示100%是表示编译或者综合通过。5区为工作区。6区为信息栏:编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。

Quartus_II简明教程

Quartus II简明教程 Altera公司的Quartus II设计软件是用来进行SOPC(System-on-a-programmable-chip)设计的综合的设计环境。本教程适用于Quartus II软件的新用户,介绍使用Quartus II软件的进行FPGA设计的基本方法。需要注意,本教程并不是Quartus II软件的详尽的参考手册。 本教程包含的主要内容: 1、典型的FPGA设计流程; 2、开始 3、新建project 4、设计输入 5、编译 6、引脚分配 7、仿真 8、编程、配置FPGA器件 9、板级调试

1、 典型的FPGA 设计流程 计算机辅助设计(Computer Aided Design ,CAD )软件的使用使得使用可编程逻辑器件(Programmable Logic Device ,PLD)器件(比如Field Programmable Gate Array ,FPGA)进行数字逻辑电路设计变得非常容易。使用CAD 软件进行FPGA 设计的典型流程如图1所示。 图1 FPGA 设计的典型设计流程 Quartus II 软件支持以上设计流程的所有阶段。本教程介绍Quartus II 软件的基本特征。 2、 开始 在Quartus II 软件中设计的每个电路或者子电路都叫做项目(Project )。Quartus II 软件每次只能打开一个Project ,并且一个Project 的所有信息都必须保存在同一个文件夹。为了开始一个新逻辑电路的设计,首先第一步就是新建一个文件夹来保存此Project 的文件。为了保存本教程的设计项目Project ,新建文件夹D:\introtutorial 。本教程运行的例子是一个简单两路开关控制电路。 启动Quartus II 软件,会打开如图2所示启动画面。启动画面中包含了使用Quartus II 软件所需要的

PowerDesigner15使用时的十五个问题

简介 PowerDesigner的主要作用一般还是数据库建模,并生成对应的数据库设计文档,可以与数据库保持同步。 一般常用的有CDM,PDM,UML建模,CDM可以转为PDM。 支持正向[生成数据库]和逆向工程[从数据库中生成],并直接关联到到数据库中,PDM可以直接和数据库进行关联,并将数据库,表,视图,触发器等数据库对象生成到数据库中,也可将这些对象更新到PDM中。 PowerDesigner的几个主要常用菜单是MODEL、DATEBASE、Tool,这三个菜单下命令使用比较多,要熟悉。PD 还可以用来画用例图,序列图,类图等UML图。 也可以画企业架构图,软件应用架构图等等图形 15个问题列表: No.1:是不是一定要从CDM开始设计,然后在进行PDM的设计? NO.2:工具栏palette不见了,如何把它找出来? NO.3: 如何建立与数据库的关联? NO.4: 域和数据项有何作用? No.5: 如何生成主键的自定义增长列,SQL Server和Oracle数据分别是如何操作的? No.6: NAME和CODE联动,如何取消? NO.7. 如何实现字段的NAME和Comment属性互换? NO.8: 如何修改某个对象的命名规则,比如外键,比如主键,比如触发器等? No.9: 如何用PD生成测试数据,以便测试? No.10 如何把CODE的NAME中文也生成在脚本中,也就是列名后就是NAME的说明文字? NO.11 如何将数据库结构,表名,表的字段导出到Word中,或者生成HTML文件以便查看? No.12 如何去除生成SQL时的双引号问题,双引号在Oracle中可以保证大小写,却异常麻烦? NO.13 如何修改PD的显示样式? No.14 如何去除表名,字段的长度限制? No.15 如何进行数据库的逆向工程? 说明:本文提到的PD基于PD15.英文版。 No1:是不是一定要从CDM开始设计,然后在进行PDM的设计? 本人觉得没有必要,项目的大小、熟悉程度、起步和个人习惯不一样,熟练业务的,项目小的直接用PDM设计未尝不可。 NO2:工具栏palette不见了,如何把它找出来? 这个问题我找了所有的菜单才找到,在【Tools】-【Customize Toolbars】点击打开,列表项里的【palette】选中即可,此外,这个窗口中还可以设计对齐的方式等等。

Quartus_II_9.0_使用初级教程

Quartus Ⅱ 9.0 使用教程(初级) Quartus Ⅱ 是Altera 公司推出的专业EDA 工具,支持原理图输入、硬件描述语言的输入等多种输入方式。硬件描述语言的输入方式是利用类似高级程序的设计方法来设计出数字系统。接下来我们对这种智能的EDA 工具进行初步的学习。使大家以后的数字系统设计更加容易上手。 第一步:打开软件 ● 快捷工具栏:提供设置(setting ),编译( compile )等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。 ● 菜单栏:软件所有功能的控制选项都可以在其下拉菜单中找到。 ● 编译及综合的进度栏:编译和综合的时候该窗口可以显示进度,当 显示100%是表示编译或者综合通过。 ● 信息栏:编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。

第二步:新建工程(file>new Project Wizard ) 1 工程名称: 2添加已有文件(没有已有文件的直接跳过next )

3 选择芯片型号(我们选择MAX3000A 系列下的EPM3256AQC208-10芯片) 4 选择仿真,综合工具(第一次实验全部利用quartus 做,三项都选None ,然后next )

5 工程建立完成(点finish) 第三步:添加文件(file>new> VHDL file),新建完成之后要先保存。

第四步:编写程序 3-8译码器的VHDL描述源文件如下: library ieee; use ieee.std_logic_1164.all; entity decoder3_8 is port( A:in std_logic_vector(2 downto 0); EN:in std_logic; Y:out std_logic_vector(7 downto 0)); end decoder3_8; architecture example_1 of decoder3_8 is signal sel:std_logic_vector(3 downto 0); begin sel<=A & EN; with sel select Y <= "11111110" when "0001", "11111101" when "0011", "11111011" when "0101", "11110111" when "0111", "11101111" when "1001", "11011111" when "1011",

powerdesign教程文档

实验一 数据库 E-R 模型建立

一.实验目的: 实验目的:

1. 了解天据库设计概念设计中的基本知识:如实体、所性、联师集… 2. 3. 4. 能解决设计中常见问题:如用实体集还是用所性 使学学能独成完成天据库模式的设计,包括各表的结构(所性姓、类型、约束和师键 字等)及表之成的师师以及其连接方式,在选定的 DBMS 上建成天据库表。 熟悉天据库建模工具的使用(PowerDesigner 9) 5. 学会使用 Sybase 公司的 PowerDesigner 9 建模工具绘制概念模型图。

二.实验要求: 实验要求:

1. 认真阅读业务需求,作出 E-R 图,并依据设计原则对天据库结构的设计务必做到最优化 2. 在选定的 DBMS 上建成天据库,比较手工输入 SQL 建成天据库与用建模工具自动学成天 据库的优缺点

三.实验环境及学成安排: 实验环境及学成安排:

1. OFFICE 2000,POWERDESIGNER9.0

2. SQL SERVER 2000 3. 学成:4 学成 四.内容提要

使用 PowerDesigner 9 绘制概念模型图 随着天据库应用师统的广泛使用,各大天据库厂商和第三方合作开发了智能化的天据 库建模工具,如 Sybase 公司的 PowerDesigner、RATIONAL 公司的 Rational Rose、Oracle 公司的 CASE*METHOD 等,它们是同一类型的计算机辅助软件工程(CASE)工具。CASE 工具 把开发人员从繁重的劳动中解脱出来,大大地提高了天据库应用师统的开发质量。 PowerDesigner 是 Sybase 公司的天据库建模工具,使用它可以方便地对管理信息师统 进行分析设计, 它几乎包括了天据库模型设计的全过程。 利用 PowerDesigner 可以制作天据 流程图、概念天据模型、物理天据模型,可以学成多种客户端开发工具的应用程序,可为天 据仓库制作结构模型,还可以对社队设计模型进行控制。 PowerDesigner 是唯一结合了下列几种标准建模技术的建模工具套件: 使用 UML 的应 用程序建模、 业务流程建模和传统天据库建模技术, 从而为您提供了高度集成、 基于知识库、 可自定义、图形化、直观并易于使用的工具集。作为功能强大的全部集成的建模和设计解决

实验七 PowerDesigner数据库设计

实验七PowerDesigner数据库设计 一、目的与要求 1.掌握PowerDesigner建立概念模型的方法 2.掌握PowerDesigner建立物理模型的方法 3.掌握PowerDesigner生成数据库表的方法 4.掌握PowerDesigner生成报表的方法 二、实验准备 1.了解数据库设计的三个主要步骤概念设计、逻辑设计和物理设计要完成的工 作; 2.了解概念模型向逻辑模型转换的方法; 3.了解PowerDesigner软件的操作环境。 三、实验内容 根据对“大学教学管理数据库”进行分析和设计,建立其概念模型,转换成物理模型,并生成标准报表文件。记录操作步骤和模型图。 1.建立概念模型 打开PowerDesigner,选择菜单“new”,选择“Conceptual Data Model”类型的文件,新建模型。如图7-1所示。 图7-1 打开如图7-2的建立概念模型的主界面,根据分析所得该数据库至少有3个实体,学生,课程,教师及其多对多的联系类型。选择相应的按钮,添加到模型中,双击实体或联系,可以打开并填写实体名,属性,联系名和类型等,如图7-3所示。 注意:图7-2中并不是完整的模型,要根据自己的分析和设计画出完整的“大

学教学管理数据库”的概念模型。 图7-2 课程: 学生:

教师: 图7-3 完整的概念模型建立完毕,保存成.CDM的文件。 2.转换成物理模型 选择菜单“Tools”下“Generate Physical Data Model”,生成对应的物理模型,选择类型为SQL Server 2005支持的物理模型。如图7-4所示。

PowerDesigner教程

数据库建模工具PowerDesigner简介工具如下图: PowerDesigner系列产品提供了一个完整的建模解决方案,业务或系统分析人员,设计人员,数据库管理员DBA和开发人员可以对其裁剪以满足他们的特定的需要;而其模块化的结构为购买和扩展提供了极大的灵活性,从而使开发单位可以根据其项目的规模和范围来使用他们所需要的工具。PowerDesigner灵活的分析和设计特性允许使用一种结构化的方法有效地创建数据库或数据仓库,而不要求严格遵循一个特定的方法学。PowerDesigner提供了直观的符号表示,使数据库的创建更加容易,并使项目组内的交流和通讯标准化,同时能更加简单地向非技术人员展示数据库和应用的设计。 PowerDesigner不仅加速了开发的过程,也向最终用户提供了管理和访问项目的信息的一个有效的结构。它允许设计人员不仅创建和管理数据的结构,而且开发和利用数据的结构针对领先的开发工具环境快速地生成应用对象和数据敏感的组件。开发人员可以使用同样的物理数据模型查看数据库的结构和整理文

档,以及生成应用对象和在开发过程中使用的组件。应用对象生成有助于在整个开发生命周期提供更多的控制和更高的生产率。 PowerDesigner是一个功能强大而使用简单工具集,提供了一个复杂的交互环境,支持开发生命周期的所有阶段,从处理流程建模到对象和组件的生成。PowerDesigner产生的模型和应用可以不断地增长,适应并随着你的组织的变化而变化。 PowerDesigner包含六个紧密集成的模块,允许个人和开发组的成员以合算的方式最好地满足他们的需要。这六个模块是: PowerDesigner ProcessAnalyst,用于数据发现。 PowerDesigner DataArchitect,用于双层,交互式的数据库设计和构造。PowerDesigner AppModeler,用于物理建模和应用对象及数据敏感组件的生成。PowerDesigner MetaWorks,用于高级的团队开发,信息的共享和模型的管理。PowerDesigner WarehouseArchitect,用于数据仓库的设计和实现。PowerDesigner Viewer,用于以只读的、图形化方式访问整个企业的模型信息。 下面详细介绍PowerDesigner的六个模块: PowerDesigner ProcessAnalyst 用于数据分析或"数据发现"。ProcessAnalyst模型易于建立和维护,并可用在应用开发周期中确保所有参与人员之间顺畅的通讯。这个工具使用户能够描述复杂的处理模型以反映他们的数据库模型。通过表示这些在系统中的处理和描述它们交换的数据,使用ProcessAnalyst可以以一种更加自然的方式描述数据项。 PowerDesigner DataArchitect 用于两层的即概念层和物理层数据库设计和数据库构造。DataArchitect提供概念数据模型设计,自动的物理数据模型生成,非规范化的物理设计,针对多种数据库管理系统(DBMS)的数据库生成,开发工具的支持和高质量的文档特性。使用其逆向工程能力,设计人员可以得到一个数据库结构的"蓝图"可用于文档和维护数据库或移植到一个不同的DBMS。 PowerDesigner AppModeler 用于物理数据库的设计和应用对象及数据敏感组件的生成。通过提供完整的物理建模能力和利用那些模型进行开发的能力,AppModeler允许开发人员针对领先的开发环境,包括PowerBuilder,Visual Basic,Delphi2.0和Power++,快速地生成对象和组件。此外,AppModeler还可以生成用于创建数据驱动的Web站点的组件,使开发人员和设计人员同样可以从一个DBMS发布"动态"的数据。另外,

QuartusII10.0简明教程

Quartus ii 10.0教程 说明 本文的部分章节,来源于本人翻译的Terasic DE2-115的英文入门文档。 平台 硬件:艾米电子EP2C8-2010增强版套件 软件:Quartus II 10.0 + ModelSim-Altera 6.5e (Quartus II 10.0) Starter Edition 内容 ?典型的CAD流程 ?开始 ?新建工程 ?录入Verilog设计 ?编译设计 ?引脚分配 ?仿真设计电路 ?编程及配置到FPGA器件 ?测试设计电路 典型的CAD流程 计算机辅助设计(CAD)软件,使得运用可编程逻辑器件实现所需逻辑电路,变得容易。比如现场可编程门阵列(FPGA)。典型的FPGA CAD设计流程如图1所示。

图1 典型的FPGA CAD设计流程 CAD流程包含以下步骤: ?设计输入——所需电路可通过原理图方式或硬件描述语言方式(如Verilog或VHDL)进行设计。 ?综合——输入的设计被综合进入由逻辑元素(LEs,FPGA芯片提供)组成的电路中。 ?功能仿真——综合电路被测试以验证其功能是否正确,次仿真不考虑时序因素。 ?布局布线——CAD Fitter工具决定网表中定义的LEs如何布置成FPGA芯片中的实际LEs。 ?时序分析——分析已布局布线电路中的不同路径的传播延迟,用以指示所需电路的性能。 ?时序仿真——测试已布局布线电路,验证其是否在功能和时序上都正确。 ?编程及配置——设计的电路,通过编程配置开关,被实现到一个物理的FPGA芯片。 配置开关用于配置LEs和建立所需线路连接。 本指南介绍Quartus II软件的基本特征。展示如何使用Verilog硬件描述语言来设计和实现电路。使用GUI来实现Quartus II指令。通过本份指南,读者将学习到: ?新建工程 ?使用Verilog代码录入设计 ?将综合的电路布局到Altera FPGA ?分配电路的输入输出到FPGA上的指定引脚 ?仿真设计电路 ?编程配置艾米电子EP2C8核心板上的FPGA芯片 1. 开始 在Quartus II中设计的每个逻辑电路或子电路,叫做一个工程。软件每次运行一个工程,并将所有信息保存在单一文件夹中。欲开始一个新的逻辑电路设计,第一步就是新建一个文件夹来保存文件。为了保存本指南的设计文件,在D盘新建introtutorial文件夹。指南者运行的范例为一个简单的双路灯控电路。 打开Quartus II软件,将看到类似于图2的画面。该显示画面包括若干窗口,用户可使用鼠标选择,以访问Quartus II软件的相关功能。Quartus II提供的大多数命令都可用菜单形式来访问。例如,在图2中,在File标签下点击左键,可打开如图3所示的菜单。用左键单击Exit可退出Quartus II软件。

- PowerDesigner画ER图详细教程最完整

- PowerDesigner12.5教程(完整版)解读

- PowerDesigner12.5教程(完整版)

- PowerDesigner教程(完整)

- PowerDesigner实例实战教程

- PowerDesign学习教程

- PowerDesigner实例教程

- PowerDesigner教程PPT

- PowerDesigner12.5中文教程(完整版)

- powerdesigner16从入门到精通

- PowerDesigner12.5教程(完整版)

- PowerDesigner使用教程-PDM精讲

- PowerDesigner12.5教程(完整版)

- PowerDesign中文chm教程chm

- PowerDesigner使用教程使用方法

- PowerDesigner教程

- 使用PowerDesigner设计ER图详细教程

- PowerDesigner教程(ppt)

- (完整word版)PowerDesigner16.5中文教程-数据库模型操作教程

- PowerDesigner实例教程