门电D触发器与位计数器的设计

数字逻辑课程实验报告

实验名称门电D触发器与8位计数器的设计

实验人姓名

学???? 号

班级

同组人姓名

实验时间

成绩

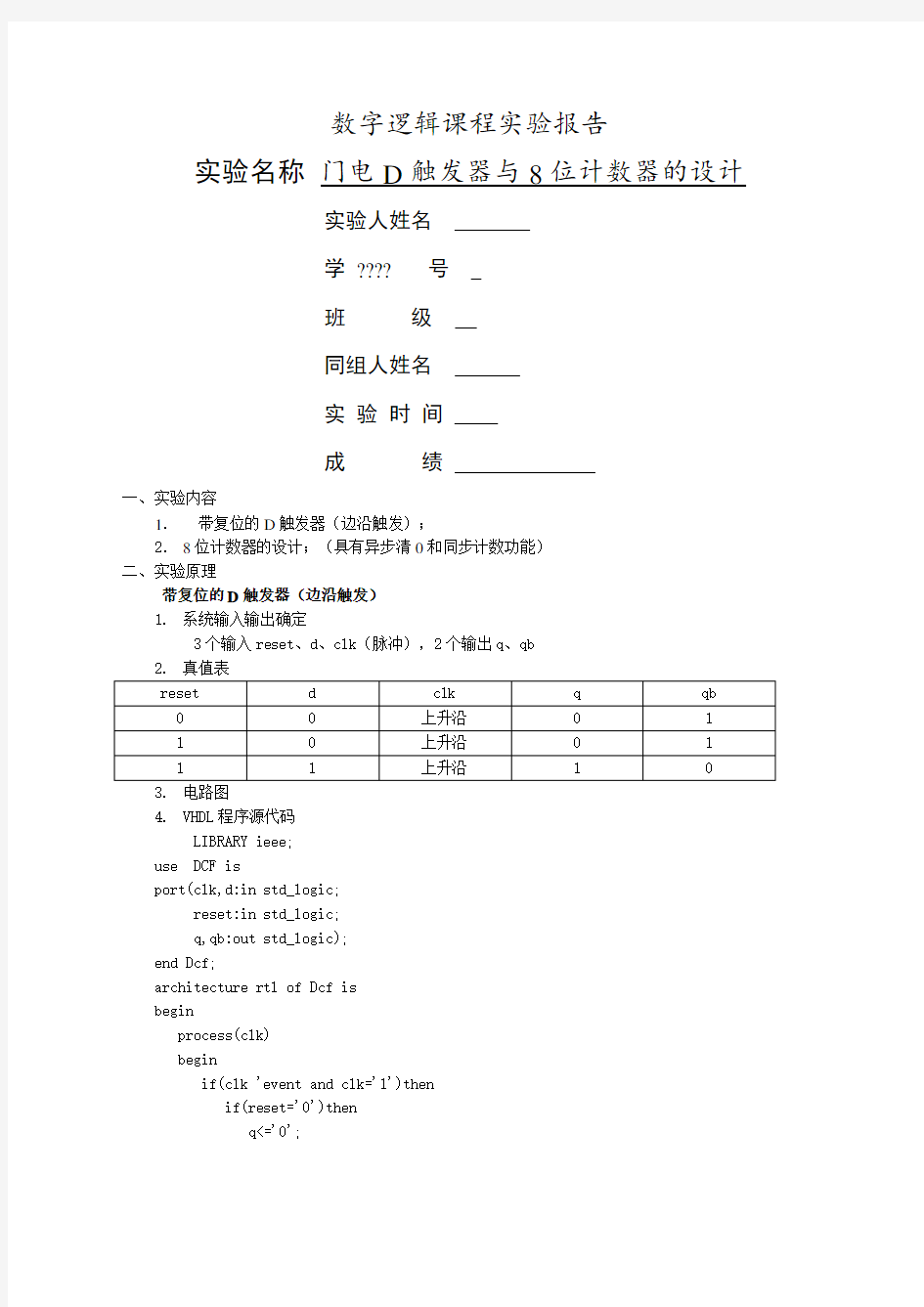

一、实验内容

1.带复位的D触发器(边沿触发);

2.8位计数器的设计;(具有异步清0和同步计数功能)

二、实验原理

带复位的D触发器(边沿触发)

1.系统输入输出确定

3个输入reset、d、clk(脉冲),2个输出q、qb

2.真值表

3.电路图

4.VHDL程序源代码

LIBRARY ieee;

use DCF is

port(clk,d:in std_logic;

reset:in std_logic;

q,qb:out std_logic);

end Dcf;

architecture rtl of Dcf is

begin

process(clk)

begin

if(clk 'event and clk='1')then

if(reset='0')then

q<='0';

qb<='1';

else

q<=d;

qb<=not d;

end if;

end if;

end process;

end rtl;

8位计数器的设计

1、系统输入输出确定

4个输入clk,r,s,en,1个输出co,q即可作为输入也可以是输出。

2、真值表

3、电路图

4、VHDL程序源代码

LIBRARY ieee;

use jsq is

port(clk,r,s,en:in std_logic;

co:out std_logic;

q:buffer std_logic_vector(7 downto 0));

end jsq;

architecture rtl of jsq is

begin

process(clk,r)

begin

if(r='1')then

q<=(others=>'0');

elsif(clk'event and clk='1')then

if(s='1')then

q<=(others=>'0');

elsif(en='1')then

q<=q+1;

else

q<=q;

end if;

end if;

end process;

else '0';

end rtl;

三、测试及分析

D触发器仿真波形

8位计数器仿真波形

3.实验分析:D触发器和8位计数器的仿真波形图中波形与真值表一致实验结果证明:D触发器和8位计数器的设计真实的实验结果与理论结果相同。

四、总结

使用D触发器设计一个11001序列检测器介绍

讨论使用D触发器设计一个11001序列检测器,讨论序列可交迭(Overlap)检测和不可交迭检测在设计上的区别,讨论分别采用Mealy机设计和采用Moore机设计的区别,讨论未用状态的处理问题。 【要求】给出电路原理图或HDL代码,要求进行仿真,并给出仿真结果。 1.原件介绍 D触发器(74LS74)、“与”门(74LS08)、“或”门(74LS32)、“非”门(74LS04),集成电路引脚

2.设计思路 根据要求,设计的序列检测器有一个外部输入x和一个外部输出Z。输入和输出的逻辑关系为:当外部输入x第一个为"1",外部输出Z为"0";当外部输入x 第二个为"1",外部输出Z为"0";当外部输入第三个x为"0",外部输出Z为"0",当外部输入第四个x为“0”,外部输出Z为0,当外部输入第五个x为“1”,外部输出Z为“1”。假定有一个外部输入x序列以及外部输出Z为: 输入X 0 1 1 1 0 0 1 0 1 输出Y 0 0 0 0 0 0 1 0 0 要判别序列检测器是否连续接收了"11001",电路必须用不同的状态记载外部输入x的值。假设电路的初始状态为A,x 输入第一个"1",检测器状态由A装换到B,用状态B记载检测器接受了"11001"序列的第一个"1",这时外部输出Z=0;x输入第二个"1",检测器状态由B装换到C,用状态C 记载检测器接了“11001”序列的第二个"1",外部输出Z=0;x输入第三个"0",检测器状态由C装换到D,外部输出Z=0;x输入第四个为“0”,检测器状态由D装换到E,外部输出Z=0;x输入第五个为“1”,检测器状态由E装换到F,外部输出Z=1。然后再根据外部输入及其他情况时的状态转移,写出相应的输出。以上分析了序列检测器工作,由此可画出原始状态图。根据原始状态图可列出原始状态表。 状态转换表 A B D C E F 1\0 1\0 0\0 0\0 1\1 0\0 0\0 1\0 1\0 0\0 0\0

电子抢答器数电课程设计

设计题目:智力竞赛电子抢答器 设计要求及技术指标: 1、抢答器电路分为抢答电路设计和必答电路设计。 2、抢答电路设计具体要求: (1)抢答组数分为四组,序号为1~4。 (2)优先判断与指示电路设计。 (3)主持人清除上次抢答结果的电路设计。 (4)主持人给选手打分电路与选手得分累计显示电路设计。 3、必答电路设计具体要求: (1)30秒必答倒计时电路设计。 (2)超时短暂报警。 第 1 章电路设计简介 1 原理电路设计: 1.1 电路总体工作框图 图1:课程设计的总体框图

整个电路框图如上图所示,主要可分为三个部分,第一部分为四路选手抢搭电路,这部分电路主要采用了四个74LS595来实现四位选手仅选可选通一路的功能实现,并结合使用多个四路与非门(即74LS10)来实现其对计时电路的控制。第二部分为计时电路,其通过两个级联的74LS161与555定时器来实现计时功能,并通过其对于声音警示电路控制。第三部分为选手计分电路,需用了可加可减的74LS192来实现对于选手的加减积分功能。整个电路在学校提供的开发板上,其中所需使用的LED灯、按钮按照开发板作相应的调整。 第 2 章硬件电路的组成 1电路工作原理 当第一位选手按下按钮,74LS373锁存器构成的选通电路就会将低电平传至二极管led的负极,此时若有其他选手再按下按钮,其会导致74LS373处于锁存数据状态,从而使已经亮的小灯不会受到其他选手按钮的影响,另一方面已经选通一路会通过锁存器阻止其他路数据的传入。另一方面四位按钮通过控制74LS161来实现对计时电路的控制,以使得当有选手按下按钮时计时才开始。 计时电路由两个异步清零的模十计数器构成,对其清零通过对于其清零端与使能端置低电平完成,而两位已内置好74LS48的数码管通过与74LS161的输出管脚来实现时间的显示。因为电路要求30秒计时,所以使用计时十位的74LS161的低两位作为是否到达30s的判断信号,当Q1、Q0均为1的时候就是到达30s,此时通过与非门输出来控制扬声器以及停止计时。 选手计分电路通过使用可加可减的74LS192来完成,当其5管脚为上升沿是,其数值加一;而当4管脚为上升沿时,其数值减一。而上升的产生则通过使用电源、地与一个按钮完成。选手分数的显示通过使74LS192的输出管脚与已内置好74LS48的数码管相连来完成。 总体电路的设计思路如上,后期搭建电路过程中依据实际情况做了小幅调整,当整体思路未变。 1.1总体电路原理图如下:

数电课程设计秒计时器

数电课程设计秒计时器 The final edition was revised on December 14th, 2020.

课程设计任务书 学生姓名:专业班级: 指导教师:工作单位: 题目: 30秒计时器 电路设计 控制电路的设计...................................................................... (13) 报警电路............................................................................ (16)

摘要 计时器在人类生活中有着非常重要而广泛的应用,古时候人们就开始用沙漏和水漏做定时工具,随着科技和社会的发展,人们开始用全新的方法来改造计时器以达到准确计时的目的。 篮球竞赛计时器就是一种典型的计时器的应用。在篮球比赛中规定球友持球的时间不能超过30秒,否则就是犯规。本课程设计的“篮球竞赛30秒计时器”,可用于篮球比赛中,用于对球员持球时间进行30秒限制,一旦球员持球的时间超过了30秒,它将自动报警从而判定刺球员的犯规。 本文设计用的是实现以中小规模集成电路设计计时器的方法,它是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。它是由时钟脉冲产生电路、计数电路、译码驱动及显示电路、报时电路及电源电路组成。时钟脉冲采用555定时器构成多谐振荡电路产生,。。。。通过EDA软件Multisim10绘制了电子电路仿真原理图,并进行仿真,同时用万能板焊接制作了硬件实现电路。

Abstract Clock ,as we all know ,is widly and importantly used in human ancient,our ancestor began to use sandglass and hourglass as timework,but,with the fast development of science and sociaty,people start using all new method to change out clock and make it more exacat. Basketball game is a particular field to use is a rule in basketball game that player can ’t hold the ball exceed 30 seconds,otherwise it is a foul.”the 30 seconds clock in basketball game ”designed in my course design can used in badketball game,to limited players hold the ball in players hold ball over 30 seconds it will give an alarm by itself to judge the player is foul. What the paper use is the design to realize medium scale with integrated circuit design method, it is a kind of typical digital circuits, including the portfolio logic circuit and the sequential is constitute by the clock pulse circuits, counting circuit, decode drive and display circuit, chime circuit and power circuit component. Clock pulse 555 timing constitute by multiple resonance swing circuit produce,... we draws electronic circuit simulation principle chart and simulation through Multisim10 EDA software, at the same time we use the universal plate welding to made hardware realization circuit. 1系统原理框图 图 1系统原理框图 一. 1秒脉冲发生器: 秒脉冲信号发生器需要产生一定精度和幅度的矩形波信号。实 现这样矩形波的方法很多,可以由非门和石英振荡器构成,可由单稳态电路构成,可以由施密特触发器构成,也可以由555点哭构成等。 不同的电路队矩形波频率的精度要求不同,由此可以选用不同电路结构的脉冲信号发生器。本实验中由于脉冲信号作为计数器的计时脉冲,其精度直接影响计数器的精度,因此要求脉冲信号有比较高的精度。一般情况下,要做出一个精度比较高的 频率很低的振荡器有一定的难度 工程上解决这一问题的办法就是先做一个频率比较高的矩形波 秒脉冲发生器 计时器 译码显示电路 控制电路 报警电路 外部操作开关

设计一个一位十进制加减法++数字电路课程设计报告

课程设计报告 课程:微机系统与接口课程设计学号: 姓名: 班级: 教师:

******大学 计算机科学与技术学院 设计名称:设计一个一位十进制加减法器 日期:2010年1月 23日 设计内容: 1、0-9十个字符和“+”“-”分别对应一个按键,用于数据输入。 2、用一个开关控制加减法器的开关状态。 3、要求在数码显示管上显示结果。 设计目的与要求: 1、学习数字逻辑等电路设计方法,熟知加减法器、编码器、译码显示的工作原理及特点; 2、培养勤奋认真、分析故障和解决问题的能力。 设计环境或器材、原理与说明: 环境:利用多功能虚拟软件Multism8进行电路的制作、调试,并生成文件。器材:74LS283或者4008, 4个异或门(一片74LS86)(减法);74LS08,3输入或门(加法) 设计原理: 图1二进制加减运算原理框图 分析:如图1所示,第一步置入两个四位二进制数(要求置入的数小于1010), 如(1001) 2和(0111) 2 ,同时在两个七段译码显示器上显示出对应的十进制数 9和7;第二步通过开关选择运算方式加或者减;第三步,若选择加运算方式,

所置数送入加法运算电路进行运算,同理若选择减运算方式,则所置数送入减法运算电路运算;第四步,前面所得结果通过另外两个七段译码器显示。 设计过程(步骤)或程序代码: 实验电路: 1:减法电路的实现: (1):原理:如图1所示(如下),该电路功能为计算A-B。若n位二进制 原码为N 原,则与它相对应的补码为N 补 =2n-N 原 ,补码与反码的关系式为N 补 =N 反 +1, A-B=A+B 补-2n=A+B 反 +1-2n (2):因为B○+1= B非,B○+0=B,所以通过异或门74LS86对输入的数B求 其反码,并将进位输入端接逻辑1以实现加1,由此求得B的补码。加法器相加的结果为: A+B 反 +1, (3):由于2n=24=(10000) 2 ,相加结果与相2n减只能由加法器进位输出信号完成。当进位输出信号为1时,它与2n的差为0;当进位输出信号为0时,它与2n差值为1,同时还要发出借位信号。因为设计要求被减数大于或等于减数,所以所得的差值就是A-B差的原码,借位信号为0。

数电课程设计抢答器

数电课程设计——抢答器 1220223 16 左杉2014.6.25 设计目的 掌握四人智力竞赛抢答器电路的设计方法。 设计任务与要求 (1)4名选手编号为:1,2,3,4。各有一个抢答按钮S0 ~ S4表示。,按钮的编号与选手的编号对应。 (2)给主持人设置一个控制按钮,用来控制系统清零(抢答显示数码管灭灯)和抢答的开始控制开关S。 (3)抢答器具有数据锁存和显示的功能。抢答开始后,若有选手按动抢答按钮,该选手编号立即锁存,并在抢答显示器上显示该编号,同时扬声器给出音响提示,封锁输入编码电路,禁止其他选手抢答。抢答选手的编号一直保持到主持人将系统清零为止。 一.抢答器的基本功能 1.设计一个抢答器,可同时供四名选手或四个代表队参加比赛,编号为一,二,三,四,各用一个抢答按钮,分别用四个开关表示。 2.给节目主持人设置一个控制开关,用来控制系统的清零(编号显示数码管灭灯)和抢答的开始。

3.抢答器具有数据锁存和显示的功能,抢答开始后,若有选手按动抢答按钮,编号立即锁存,并在LED数码管上显示出选手的编号,并且给出出声响提示,封锁输入电路,实现优先锁存,禁止其他选手抢答,优先抢答选手的编号一直保持到主持人将系统清零为止。 二.使用元件 芯片:74ls75,74ls147,74ls48,74ls08,74ls04,74ls00 其他器件:5个单刀单掷开关,一个7段数码管,一个蜂鸣器,一个三极管,导线若干。 三.具体原理为 1)抢答器电路 该部分主要是由74LS75实现的,此元件是低端有效。当四个选手抢答时,输入的信号为“1”,用74LS20将这四个选手在75芯片对应的非输出端与主持人的主控开关相与非,接入75的使能端(E0/1和E2/3),这样就通过“0”,把75锁定,完成锁定功能。

三位数显示计时器定时器数电课程设计

文档大全 沈阳航空航天大学 课程设计三位数字显示计时器定时器设计 班级 学号 学生姓名 指导教师

文档大全 沈阳航空航天大学 课程设计任务书 课程名称电子线路课程设计 课程设计题目三位数字显示计时器定时器设计 课程设计的内容及要求: 一、设计说明与技术指标 设计一个三位数字显示计时器、定时器电路,技术指标如下: ①计时、定时能够任意启停,保持计时、定时结果; ②开机自动复位; ③最大显示时间为9分59秒; ④设置时间,定时报警; 二、设计要求 1.在选择器件时,应考虑成本。 2.根据技术指标,通过分析计算确定电路和元器件参数。 3.画出电路原理图(元器件标准化,电路图规范化)。 三、实验要求 1.根据技术指标制定实验方案;验证所设计的电路,用软件仿真。 2.进行实验数据处理和分析。 四、推荐参考资料 1. 童诗白,华成英主编.模拟电子技术基础.[M]北京:高等教育出版社,2006年 五、按照要求撰写课程设计报告

文档大全 成绩评定表: 序号 评定项目 评分成绩 1 设计方案正确,具有可行性,创新性( 15分) 2 设计结果可信(例如:系统分析、仿真结果)(15分) 3 态度认真,遵守纪律(15分) 4 设计报告的规范化、参考文献充分(不少于5篇)(25分) 5 答辩(30分) 总分 最终评定成绩(以优、良、中、及格、不及格评定) 指导教师签字: 2016年 12月 31日

文档大全 一、概述 此次课设题目为及时定时系统,计时器和定时器在人们日常生活中有着广泛的应用, 本次课程就是设计利用555定时器以及数字逻辑芯片和数码管实现数字电子计时器和定时器功能,能够满足基本的功能要求,电路要求由可控脉冲发生器、计数电路,显示数码管电路以及报警电路组成。旨在通过这次课程设计实现知识的活学活用,能够将知识运用到实践中去,数字电路分为组合电路和逻辑电路,而本次课设则是基于对逻辑同步或者异步知识的掌握,能够根据题目选用相应的芯片,设计相应的电路,是本次实验最大的目的。 二、方案论证 方案一:使用数字电路的原理设计本方案,方案一利用555定时器以及数字逻辑芯片和数码管实现数字电子计时器和定时器功能,电路要求由可控脉冲发生器、计数电路,显示数码管电路以及报警电路组成。使用555多谐振荡器产生脉冲信号,使用数字芯片进行计数,通过LED 进行报警最后使用显示译码器显示计数。所以一共有四部分组成。 图1 总体电路的原理框图 方案二: 方案二采用单片机编程进行设计实现计时器或者定时器的设计。

数电自动打铃器课程设计

数字电子技术课程设计题目自动打铃器 姓名:___ XXXXXX ___ 所在学院:工学院 所学专业:_ 电气工程及其自动化 班级___ 电气工程XXXX 学号___ XXXXXXXXXXXXX 指导教师:_____ XXXXXX_ ___ 完成时间:____ 2XXXXXXXXX

数电课程设计任务书 一、基本情况 学时:40学时学分:1学分适应班级: 二、进度安排 本设计共安排1周,合计40学时,具体分配如下: 实习动员及准备工作:2学时 总体方案设计:4学时 查阅资料,讨论设计:24学时 撰写设计报告:8学时 总结:2学时 教师辅导:随时 三、基本要求 1、课程设计的基本要求 数字电子技术课程设计是在学习完数字电子课程之后,按照课程教学要求,对学生进行综合性训练的一个实践教学环节。主要是培养学生综合运用理论知识的能力,分析问题和解决问题的能力,以及根据实际要求进行独立设计的能力。初步掌握数字电子线路的安装、布线、焊接、调试等基本技能;熟练掌握电子电路基本元器件的使用方法,训练、提高读图能力;掌握组装调试方法。其中理论设计包括总体方案选择,具体电路设计,选择元器件及计算参数等,课程设计的最后要求是写出设计总结报告,把设计内容进行全面的总结,若有实践条件,把实践内容上升到理论高度。 2、课程设计的教学要求 数字电子技术课程设计的教学采用相对集中的方式进行,以班为单位全班学生集中到设计室进行。做到实训教学课堂化,严格考勤制度,在实训期间累计旷课达到6节以上,或者迟到、早退累计达到8次以上的学生,该课程考核按不及格处理。在实训期间需要外出查找资料,必须在指定的时间内方可外出。 课程设计的任务相对分散,每3名学生组成一个小组,完成一个课题的设计。小组成员既有分工、又要协作,同一小组的成员之间可以相互探讨、协商,可以互相借鉴或参考别人的设计方法和经验。但每个学生必须单独完成设计任务,要有完整的设计资料,独立撰写设计报告,设计报告雷同率超过50%的课程设计考核按不及格处理。

利用D触发器构成计数器

利用D触发器构成计数 器 TYYGROUP system office room 【TYYUA16H-TYY-TYYYUA8Q8-

数字电路实验设计: D触发器组成的4位异步二进制加法计数器一、选用芯片74LS74,管脚图如下: 说明:74LS74是上升沿触发的双D触发器, D触发器的特性方程为 二、设计方案: 用触发器组成计数器。触发器具有0 和1两种状态,因此用一个触发器就可以表示一位二进制数。如果把n个触发器串起来,就可以表示n位二进制数。对于十进制计数器,它的10 个数码要求有 10 个状态,要用4位二进制数来构成。下图是由D触发器组成的4位异步二进制加法计数器。 三、实验台: 四、布线: 1、将芯片(1)的引脚4、10连到一起, 2、将芯片(2)的引脚4、10连到一起, 3、将芯片(1)的引脚10和芯片(2)的引脚10连到一起, 4、将芯片(1)的引脚10连到+5V; 5、将芯片(1)的引脚1、13连到一起, 6、将芯片(2)的引脚1、13连到一起, 7、将芯片(1)的引脚13和芯片(2)的引脚13连到一起, 8、将芯片(1)的引脚13连到+5V; 9、将芯片(1)的引脚3接到时钟信号CP 10、将芯片(1)的引脚2、6接到一起,再将引脚2接到引脚11 11、将芯片(1)的引脚8、12接到一起,再将芯片(1)的引脚8接到芯片(2)的引脚3 12、将芯片(2)的引脚2、6接到一起,再将引脚6接到引脚11 13、将芯片(1)的引脚5、9分别接到Q 0、Q 1 ,再将芯片(2)的引脚5、9分 别接到Q 2、Q 3 14、分别将两芯片的14脚接电源+5V,分别将两芯片的7脚接地0V。

数电课程设计(抢答器)

课程设计任务书 学生姓名:专业班级: 指导教师:工作单位:信息工程学院 题目: 多路数字定时抢答器设计 初始条件: 本课程设计,要求用集成电路:74LSl48,74LS279,74LS48,74LSl92,NE555,74LS00,74LSl21和其它器件等,实现八路定时抢答功能。用蜂鸣器作声电器件,工作电源Vcc为+5V。 要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求) 1、课程设计工作量:1周内完成对多路数字定时抢答器的设计、仿真、装配与调试。 2、技术要求: ①可同时供8名选手(或代表队)参赛,其编号分别是0到7,各用一个抢答按钮,按钮的 编号与选手的编号相对应。给节目主持人设置一个控制开关,用来控制系统的清零(编号显示数码管灭灯)和抢答的开始。 ②抢答器具有数据锁存和显示的功能。抢答开始后,若有选手按动抢答按钮,编号立即锁存, 并数码管上显示选手的编号,同时扬声器给出声音提示;同时封锁输入电路,禁止其它选手抢答。 优先抢答选手的编号一直保持到主持人将系统清零为止。 ③抢答器具有定时抢答的功能,且一次抢答的时间可以由主持人设定(如30秒)。当主持人启 动“开始”键后,要求定时器立即进行减计时,并用显示器显示,同时扬声器发出短暂的声响,声响持续时间0.5秒左右。 ④参赛选手在设定的时间内进行抢答,抢答有效,定时器停止工作,显示器上显示选手的编号 和抢答时刻的时间,并保持到主持人将系统清零为止;如果定时抢答的时间已到,而没有选手抢答时,本次抢答无效,系统进行短暂的报警,并封锁输入电路,禁止选手超时后抢答,定时显示器上显示00。 ⑤确定设计方案,按功能模块的划分选择元、器件和中小规模集成电路,设计分电路,画出 总体电路原理图,阐述基本原理。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全 文用A4纸打印,图纸应符合绘图规范。 指导教师签名:年月日 系主任(或责任教师)签名:年月日

数电课程设计-30秒倒计时器

. 定时电路的设计 ——数字逻辑课程设计 学院:计算机学院 专业班级:计科13

时间:2015年1月4日 目录 设计要求 (3) 正文 一、倒计时器组成及原理 (3) 1.1倒计时计数器组成 (3) 1.2工作原理 (3) 二、拟定设计方案 (4) 2.1用Multisim进行仿真设计 (4) 2.2设计实现数码管显示 (4) 2.3设计555定时振荡实现秒振荡发生功能 (4) 2.4设计实现减法计数功能 (5) 2.5设计实现二位数减法计数功能 (5) 2.6设计实现反馈电路实现30秒计数功能 (5) 2.7设计实现控制电路实现启动、清零/复位和暂停/继续计数控制电路 (5) 2.7.1清零/复位电路 (5) 2.7.2暂停/继续计数电路 (6) 2.7.3启动电路 (7) 2.8设计实现闪烁报警电路 (8) 三、功能说明总结 (9) 四、课程设计小结 (9) 参考文献 (10) 附录: 一、电路原理图 (11) 二、元器件明细表 (11)

设计要求: 设计30秒倒计时计数器。 30秒倒计时器的设计功能要求包括: 1.具有30S减计时功能,计时时间到后发出声光报警信号(点亮LED,喇叭鸣叫); 2.计时时间精确(用石英振荡器产生秒信号); 3.用数码管显示剩余时间; 4.具有复位、启动、暂停、继续等操作按钮; 正文: 一、倒计时器组成及原理 1.1倒计时计数器组成 倒计时计数器选用TTL集成电路,主要由秒定时振荡发生器、减法计数器、译码器、七段数码显示器、控制电路、闪烁报警电路等组成,在电路工作过程中,电路能够通过控制器实现开始计数、清零/复位、暂停/继续计数等功能,在倒计时结束保持00状态并不断闪烁提示报警,原理图如下: 图1 1.2工作原理 当电路工作时,由555定时器组成多谐振荡器,选取适当的电容使振荡周期为1s;用两片减法计数器芯片级联组成二位数计数器,用七段数码管显示计数;控制电路通过控制减

数电课程设计报告-抢答器

课程设计报告 题目数字抢答器设计 课程名称数字电子技术院部名称龙蟠学院 专业自动化 班级M11自动化学生姓名王栋明 学号1121112015指导教师赵国树 金陵科技学院教务处制

目录 第一章设计要求 (5) 第二章总体参考方案 2.1 总体参考方案框图 (5) 2.2 总体参考时序逻辑 (6) 第三章单元电路设计 3.1 定时电路 3.1.1 电路设计 (6) 3.1.2 元件说明 (7) 3.2 开关阵列电路 3.2.1 电路设计 (8) 3.3 门控电路 3.3.1 电路设计 (8) 3.2.2 元件说明 (9) 3.4 编码电路 3.4.1 电路设计 (11) 3.4.2 元件说明 (12) 3.5 报警电路 3.5.1 电路设计 (13) 3.5.2 元件说明 (13) 3.6 显示电路

3.6.1 电路设计 (13) 3.6.2 元件说明 (13) 第四章整体电路图 (15) 第五章各部分功能的实现 5.1 按下S1启动定时30S,开始抢答,LED灯亮 (15) 5.2 某位选手抢答有效 (16) 5.3 清零、灭灯、复位 (16) 第六章心得体会

第一章设计要求 1. 数字抢答器应具有数码锁存、显示功能,抢答组数分为八组,即序号0、1、 2、3、4、5、6、7,优先抢答者按动本组开关,组号立即锁存到LED显示器上,同时封锁其它组号。 2. 系统设置外部清除键,按动清除键,LED显示器自动清零灭灯。 3. 数字抢答器定时为30秒,启动起始键后,要求:①30秒定时器开始工作; ②蜂鸣器要短暂报警;③发光二极管亮灯。 4. 抢答者在30秒内抢答,抢答有效,终止定时;30秒定时到,无抢答者本次抢答无效,系统短暂报警,发光二极管灭灯。 第二章总体参考方案 2.1、总体参考方案框图 2.2、总体参考时序逻辑 它包括定时电路、门控电路、译码显示电路、8线-3线优先编码器、RS锁存器和报警电路等六个部分组成。其中定时电路、门控电路、译码显示电路及8线-3线优先编码器三部分的时序配合尤为重要,当启动外部操作开关(起始键)时,定时器开始工作,同时打开门控电路,输出有效,8线-3线优先编码器等待

篮球竞赛24秒计时器数电课程设计

《数字电子技术》课程设计说明书课题名称:篮球竞赛24秒计时器设计 专业:电气工程及其自动化 班级:电气1202班 指导老师:胡新晚 姓名:曾瑞琪

计数器概述 篮球竞赛24秒计时器功能 随着信息时代的到来,电子技术在社会生活中发挥这越来越重要的作用,运用模电和数电知识设计的电子产品成为社会生活中不可缺少的一部分,特别是在各种竞技运动中,定时器成为检验运动员成绩的一个重要工具。在篮球比赛中,规定了球员的持球时间不能超过24秒,否则就犯规了。本课程设计的“篮球竞赛24秒计时器”可用于篮球比赛中,用于对球员持球时间24秒限制。一旦球员的持球时间超过了24秒,它就自动报警从而判定此球员的犯规。 本设计只要完成:显示24秒倒计时功能:系统设置外部操作开关,控制计时器的直接清零、启动、暂停、连续功能;在直接清零时,数码管显示器灭灯,计时器为24秒递减计时其计时间间隔为1秒,计时器递减计时到零时,数码管显示器不灭灯,同时发出光电报警信号等。 设计任务及要求 基本要求 (1)显示24秒计时功能。 (2)设置外部操作开关控制计时器直接清零、启动、暂停/连续功能。 (3)计时器为24秒递减计时器,其计时间隔为1秒。 (4递减计时到零时,显示器不能灭灯,同时发出光电报警信号。 设计任务及目标 (1)根据原理图分析各单元电路的功能; (2)熟悉电路中所用到的各集成块的管脚及其功能;

(3)进行电路的装接、调试、直到电路能达到规定的设计要求; (4)写出完整、详细的课程设计报告 主要参考器件 555 晶体定时器 74 LS00 74LS48译码器 74LS192十进制可编程同步加锁计数器

一位加法器(数电)

《电子技术课程设计报告》题目:一位加法器 学院:工程学院 专业:07级电气工程及其自动化 班级:07级1班23号 姓名:王晓龙 指导教师:李斌李芝兰 2009年12月9 日

目录 1.课程设计目的 (2) 2.课程设计题目描述和要求 (2) 3.1课程设计报告内容 (2) 3.2论述方案的各部分工作原理 (2) 3.3设计方案的图表 (9) 3.4编写设计说明书 (9) 4.总结 (10) 1.课程设计目的 课程设计是培养我们学生综合运用所学知识,发现,提出,分析和解决实际问题,锻炼实践能力的重要环节,是对学生实际工作能力的具体训练和考察过程.随

着科学技术发展的日新日异,数字电子技术已经成为当今计算机应用中重要的基础领域,在生活中可以说得是无处不在。因此作为二十一世纪的大学来说掌握运用数字电子技术及逻辑电路的开发技术是十分重要的。 (1)了解基本的逻辑门电路。 (1)在实际应用中学会编码器译码器的作用和工作方式。 (1)提高自己的动手动脑能力,将在课堂上学到的知识应用到实际当中。 2.课程设计题目描述和要求 题目:一位加法器 要求:(1)利用基本逻辑门电路和编码器,译码器及计数器完成电路(2)用LED管显示 3.课程设计报告内容 3.1 设计方案的选定与说明; 利用逻辑门电路实现两个二进数相加并求出和的组合线路。键盘输入数字,编码器,逻辑门电路,计数器,译码器驱动器,使其达到一位数加法运算。我设计的数字系统中输入数字,所以需要编码功能的逻辑电路实现编码,因为为一位加法,所以输入为0~9十个按键。通过8421BCD编译,利用基本逻辑门电路实现加法运算,因为没有小数部分运算,无小数点,因此我选用74HC4511译码驱动器连接7段式LED显示管读出结果。 3.2论述方案的各部分工作原理; 编码器部分盘输入逻辑电路就是由编码器组成。图1是用十个按键和门电路组成的8421码编码器,其功能如表1所示,其中S0~S9代表十个按键,即对应十进制数0~9的输入键,它们对应的输出代码正好是8421BCD 码,同时也把它们作为逻辑变量,ABCD 为输出代码(A为最高位),GS为控制使能标志。 对功能表和逻辑电路进行分析,都可得知:①该编码器为输入低电平有效; ②在按下S0~S9中任意一个键时,即输入信号中有一个为有效电平时,GS =1,代表有信号输入,而只有S0~S9均为高电平时GS=0,代表无信号输入,此时的输出代码0000为无效代码。由此解决了前面提出的如何区分两种情况下输出都是全0的问题。优先编码器:允许同时输入两个以上的有效编

数电课程设计报告《八路数字抢答器》

数字电路课程设计 数字抢答器 设计报告 姓名: 学号: 专业:电子信息工程系 指导教师: 2012年04 月18 日

八路数字抢答器 一、设计目的及任务 1.设计的目的 通过八路数字抢答器的设计实验,要求大家回顾所学数字电子技术的基础理论和基础实验,掌握组合电路、时序电路、编程器件和任意集成电路的综合使用及设计方法,熟悉掌握优先编码器、触发器、计数器、单脉冲触发器、555电路、译码/驱动电路的应用方法,熟悉掌握时序电路的设计方法。达到数字实验课程大纲所要求掌握的基本内容。 2.设计的任务及要求 (1)基本功能 ①设计一个智力竞赛抢答器,可同时供8名选手或8个代表队参赛,他们的选号分别是0、1、2、3、4、5、6、7,各用一个抢答按钮,按钮的编号对应分别是S0、S1、S2、S3、S4、S5、S6、S7。 ②给节目主持人设置一个控制开关,用来控制系统的清零(编号显示数码管灭灯)和抢答器的开始。 ③抢答器具有数据锁存和显示的功能。抢答开始后,若有选手按动抢答按钮,编号立即锁存,并在LED数码管上显示出选手的编号。此外,要封锁输入电路,禁止其他选手抢答。优先抢答选手的编号一直保持主持人将系统清零为止。(2)扩展功能 ①抢答器具有定时抢答的功能,且一次抢答的时间可以由主持人设定(如30秒)。当节目支持人启动“开始”键后,要求定时器立即减计时,并用显示器显示。 ②参加选手在设定的时间内抢答,抢答有效,定时器停止工作,显示器上显示选手的编号和抢答时刻的时间,并保持到主持人将系统清零为止。 ③如果定时抢答的时间已到,却没有选手抢答时,本次抢答无效,系统短暂报警,并封锁输入电路,禁止选手超时后抢答,时间显示器上显示00。 二、电路设计总方案及原理框图 1. 设计思路 (1)本题的根本任务是准确判断出第一抢答者的信号并将其锁存。实现这一功能可选择使用触发器或锁存器等。在得到第一信号之后应立即将电路的输入封锁,即使其他组的抢答信号无效。同时还必须注意,第一抢答信号应该在主持人发出抢答命令之后才有效。

数字电子技术课程设计电子秒表

数字电子技术课程设计报告题目:电子秒表的设计 专业: 班级: 姓名: 指导教师: 课程设计任务书 学生班级:学生姓名:学号: 设计名称:电子秒表的设计 起止日期: 指导教师:周珍艮

目录 绪论- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 4 第一章、设计要求 1.1设计任务及目的- - - - - - - - - - - - - - - - - - - - - - -- - - - - - - - -5 1.2 系统总体框图- - - - - - - - - - - - - - - - - - - - - - - - - - - - -

- - - 5 1.3、设计方案分析- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -6 第二章、电路工作原理及相关调试 2.1 电路工作原理- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - 7 2.1相关调试- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -- 11 第三章、实验总结 附录A 电子秒表原理图 附录B 相关波形 元件清单 参考文献 绪论 随着电子技术的发展,电子技术在各个领域的运用也越来越广泛,渗透到人们日常生活的方方面面,掌握必要的电工电子知识已经成为当代大学生特别是理工类大学生必备的素质之一。 电子秒表是日常生活中比较常见的电子产品,秒表的逻辑结构主要由时基电路、分频器、二一五一十进制异步加法记数器、数据选择器和显示译码器等组成。整个秒表需有一个清零/ 启动信号和一个停止/保持信号装置,以便秒表能随意停止及启动,计数器的输出全都为BCD码输出,方便显示译码器连接。本次设计基于简单易行的原则,秒表显示以0.1s为最小单位,最大量程为9.9s,采用七段数码管作为显示部分,以此来达到基本设计要求.我门设计的秒表,是以555定时器为核心,以分频、计数与译码显示模块为主要构成部分的电子秒表的设计方案,充分利用数

数电课程设计乒乓球比赛word文档

乒乓球比赛游戏机 一、设计任务与要求 1 课题目的及意义 本次课程设计的内容是独立完成一个乒乓球比赛游戏机的设计,采用EWB 电路仿真设计软件完成乒乓球比赛游戏机电路的设计及仿真调试,在微机上仿真实现乒乓球比赛游戏机的设计。通过这次课程设计让我们了解和熟悉了乒乓球游戏机的原理和Multisim仿真设计软件的操作,也让我们加深了解了对双向移位寄存器、双D触发器及、加法器及逻辑门电路的一些实际用途,并将理论与实践相结合。 2 课题的内容和要求 设计一个甲、乙双方参赛,裁判参与的乒乓球比赛游戏模拟机。 基本要求: (1)用8个发光二极管排成一条直线,以中点为界,两边各代表参赛双方的位置,其中点亮的发光二极管代表“乒乓球”的当前位置,点亮的发光二极管依次由左向右或由右向左移动。 (2)当球运动到某方的最后一位时,参赛者应立即按下自己一方的按钮,即表示击球,若击中,则“球”向相反方向运动,若未击中,则对方得1分。(3)设置自动计分电路,双方各用二位数码管来显示计分,每局11分。到达11分时产生报警信号。 提高要求: (4)一方得分时,电路自动响铃3s,这期间发球无效,等铃声停止后方能继续比赛。 (5)设置局数显示,5局结束后有声响提示比赛结束。 课题任务要求 1、画出总体设计框图,以说明乒乓球比赛游戏机由哪些相对独立的功能模块组成,标出各个模块之间互相联系,时钟信号传输路径、方向和频率变化。并以文字对原理作辅助说明。

2、设计各个功能模块的电路图,加上原理说明。 3、选择合适的元器件,在EWB上连接验证、仿真、调试各个功能模块的电路。在连接验证时设计、选择合适的输入信号和输出方式,在充分电路正确性同时,输入信号和输出方式要便于电路的仿真、调试和故障排除。 4、在验证各个功能模块基础上,对整个电路的元器件和连接,进行合理布局,进行整个数字钟电路的连接验证、仿真、调试。 二、方案设计与论证 根据设计任务,对照图乒乓球比赛模拟及1.1,可以分为三个模块进行设计: 1. 球台电路:球迹移动电路可采用双向移位寄存器方法实现,由发光二极管作光点模拟乒乓球移动的轨迹。 2. 驱动控制电路:由双D触发器及逻辑门电路构成,通过此电路来控制并且实现球台灯的左右移位即实现乒乓球的运动。 3. 计分电路:使用十进制的计数器、逻辑门和集成的4管脚的数码管来组成计分电路。 通过多次设计、画图及仿真实验,我们发现方案电路最简洁,原理简单易懂,操作也很方便,且实用性较强。故采用此方案进行设计。 三、单元电路设计

D触发器的设计

目录 第一章绪论0 简介0 集成电路0 版图设计1 软件介绍1 标准单元版图设计1 标准单元版图设计的概念1 标准单元版图设计的历史1 标准单元的版图设计的优点2 标准单元的版图设计的特点2 第二章D触发器的介绍 2 简介2 维持阻塞式边沿D触发器3 电路工作过程3 状态转换图和时序图3 同步D触发器3 电路结构3 逻辑功能4 真单相时钟(TSPC)动态D触发器4 第三章工艺基于TSPC原理的D触发器设计5 电路图的设计5 创建库与视图5 基于TSPC原理的D触发器电路原理图5 创建D触发器版图6 设计步骤6 器件规格7 设计规则的验证及结果8 第四章课程设计总结9 参考文献 9 第一章绪论 简介 集成电路 集成电路(Integrated Circuit,简称IC)是20世纪60年代初期发展起来的一种新型半导体器件。它是经过氧化、光刻、扩散、外延、蒸铝等半导体制造工艺,把构成具有一定功能的电路所需的半导体、电阻、电容等元件及它们之间的连接导线全部集成在一小块硅片上,然后焊接封装在一个管壳内的电子器件。其封装外壳有圆壳式、扁平式或双列直插式等多种形式。是一种微型电子器件或部件,采

用一定的工艺,把一个电路中所需的晶体管、二极管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构;其中所有元件在结构上已组成一个整体,使电子元件向着微小型化、低功耗和高可靠性方面迈进了一大步。集成电路发明者为杰克·基尔比(基于硅的集成电路)和罗伯特·诺伊思(基于锗的集成电路)。当今半导体工业大多数应用的是基于硅的集成电路。 版图设计 版图(Layout)是集成电路设计者将设计并模拟优化后的电路转化成的一系列几何图形,包含了集成电路尺寸大小、各层拓扑定义等有关器件的所有物理信息。集成电路制造厂家根据版图来制造掩膜。版图的设计有特定的规则,这些规则是集成电路制造厂家根据自己的工艺特点而制定的。不同的工艺,有不同的设计规则。设计者只有得到了厂家提供的规则以后,才能开始设计。版图在设计的过程中要进行定期的检查,避免错误的积累而导致难以修改。很多集成电路的设计软件都有设计版图的功能,Cadence 的Virtuoso的版图设计软件帮助设计者在图形方式下绘制版图。 对于复杂的版图设计,一般把版图设计分成若干个子步骤进行: (1)划分为了将处理问题的规模缩小,通常把整个电路划分成若干个模块。(2)版图规划和布局是为了每个模块和整个芯片选择一个好的布图方案。(3)布线完成模块间的互连,并进一步优化布线结果。 (4)压缩是布线完成后的优化处理过程,他试图进一步减小芯片的面积。软件介绍 目前大部分IC 公司采用的是UNIX 系统,使用版本是SunSolaris。版图设计软件通常为Cadence ,它是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA设计和PCB 设计。软件操作界面人性化,使用方便,安全可靠,但价格较昂贵。 标准单元版图设计 标准单元版图设计的概念 标准单元,也叫宏单元。它先将电路设计中可能会遇到的所有基本逻辑单元的版图, 按照最佳设计的一定的外形尺寸要求, 精心绘制好并存入单元库中。实际设计ASIC电路时, 只需从单元库中调出所要的元件版图, 再按照一定的拼接规则拼接, 留出规则而宽度可调的布线通道, 即可顺利地完成整个版图的设计工作了。 基本逻辑单元的逻辑功能不同, 其版图面积也不可能是一样大小的。但这些单元版图的设计必须满足一个约束条件, 这就是在某一个方向上它们的尺寸必须是完全一致的, 比如说它们可以宽窄不一, 但它们的高度却必须是完全相等的,这就是所谓的“等高不等宽”原则。这一原则是标准单元设计法得以实施的根本保证。 标准单元版图设计的历史 随着集成电路产业迅猛的发展,工艺水平不断提高,集成电路特征尺寸循着摩尔定律不断缩小。设计芯片时需要考虑的因素越来越多,芯片设计的复杂程度也越来越高。因而尽可能复用一些已经通过工艺验证的IP核可以提高设计的效率,降低芯片设计的成本。

数字电路课程设计--数字抢答器

智力竞赛抢答器 一、本次课程设计目的 1.结合所学的数字电路的理论知识来完成数字电路课程设计。 2.在数字电路的课程设计中,熟悉数字电路的逻辑设计过程以及集成电路的使用。 3.学会利用一些没学过的来设计电路。 4。学会用软件方法仿真电路。 二、本次课程设计安排 1、时间安排 略。 2、地点安排 S2403实验室。 智力竞赛抢答器 1 设计目的 (1)熟悉集成电路的引脚安排及使用方法。 (2)掌握各芯片的逻辑功能及使用方法。 (3)了解面包板结构及其接线方法。 (4)了解数字抢答器的组成及工作原理。 (5)熟悉数字抢答器的设计与制作。 (6)学会用软件方法仿真电路。 2 设计思路 (1)设计抢答器电路。 (2)设计可预置时间的定时电路。 (3)设计报警电路。(选做) (4)设计时序控制电路。(选做) 3 设计过程 3.1方案论证

图 1 数字抢答器框图 数字抢答器总体方框图如图1所示。, 其工作原理为:接通电源后,主持人将开关拨到“清除”状态,抢答器处于禁止状态,编号显示器灭灯,定时器显示设定时间;主持人将开关置于“开始”状态,宣布“开始”抢答器工作。定时器倒计时,扬声器给出声响提示。选手在定时时间内抢答时,抢答器完成:优先判断、编号锁存、编号显示、扬声器提示。当一轮抢答之后,定时器停止、禁止二次抢答、定时器显示剩余时间。如果再次抢答必须由主持人再次操作“清除”和“开始”状态开关。 3.2电路设计 抢答器电路如图2所示。 图2 数字抢答器电路 该电路完成两个功能:一是分辨出选手按键的先后,并锁存优先抢答者的编号,同时译码显示电路显示编号;二是禁止其他选手按键操作无效。