杭州矽力杰笔试

IC Design Engineer Test Sheet

Analog Design

Device Knowledge

1. p+/n- junction and p-/n+ junction, which has a higher breakdown voltage Why For

a p+/n- junction having N

A and N

D

, what is the approximate function of junction

capacitance (C

j ) vs. reverse biased voltage (V

R

)

2. Draw the cross-section of a CMOS inverter. Draw the parasitic structure on the cross-section. Describe ways to prevent “latch-up”

Circuit Analysis

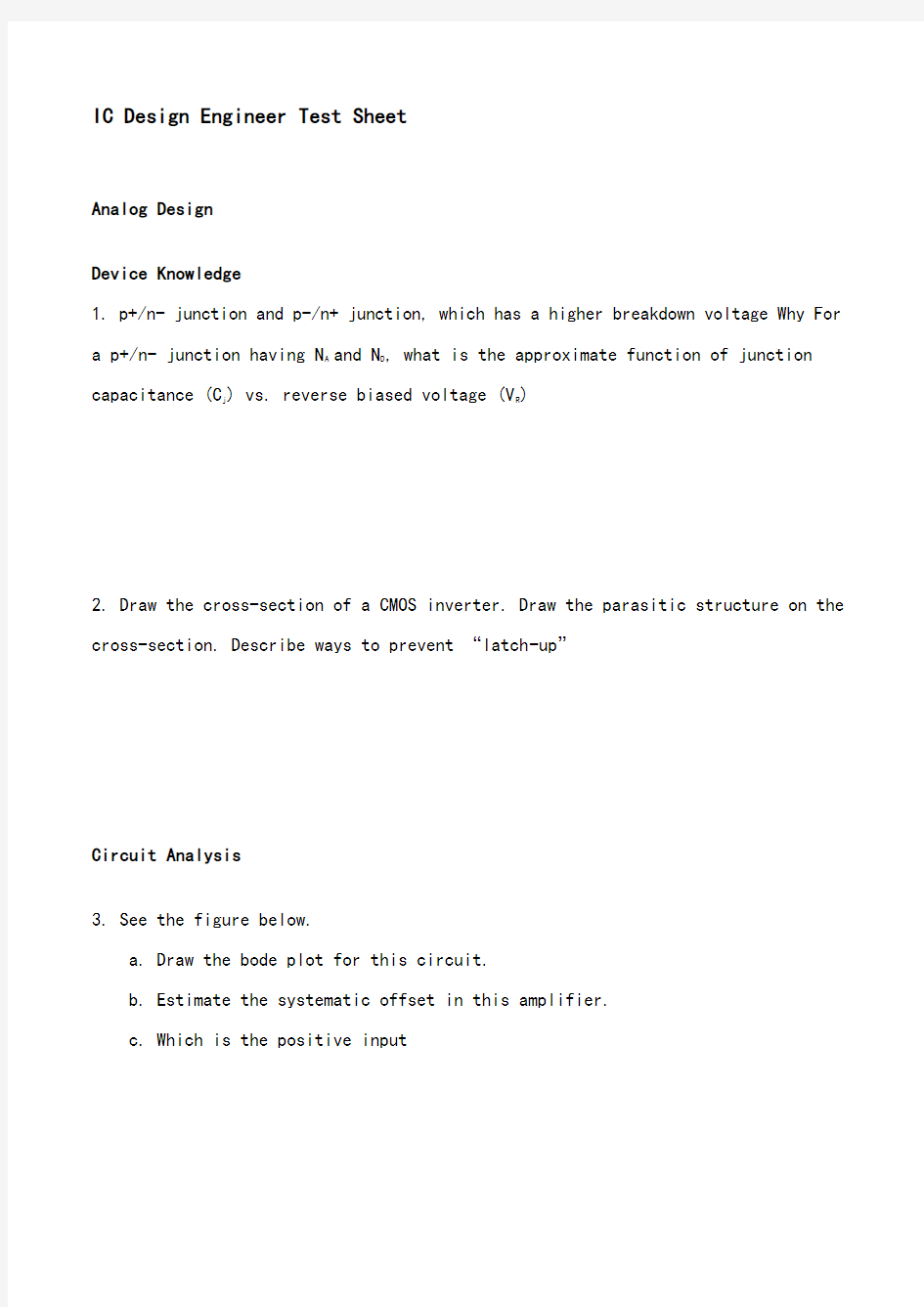

3. See the figure below.

a. Draw the bode plot for this circuit.

b. Estimate the systematic offset in this amplifier.

c. Which is the positive input

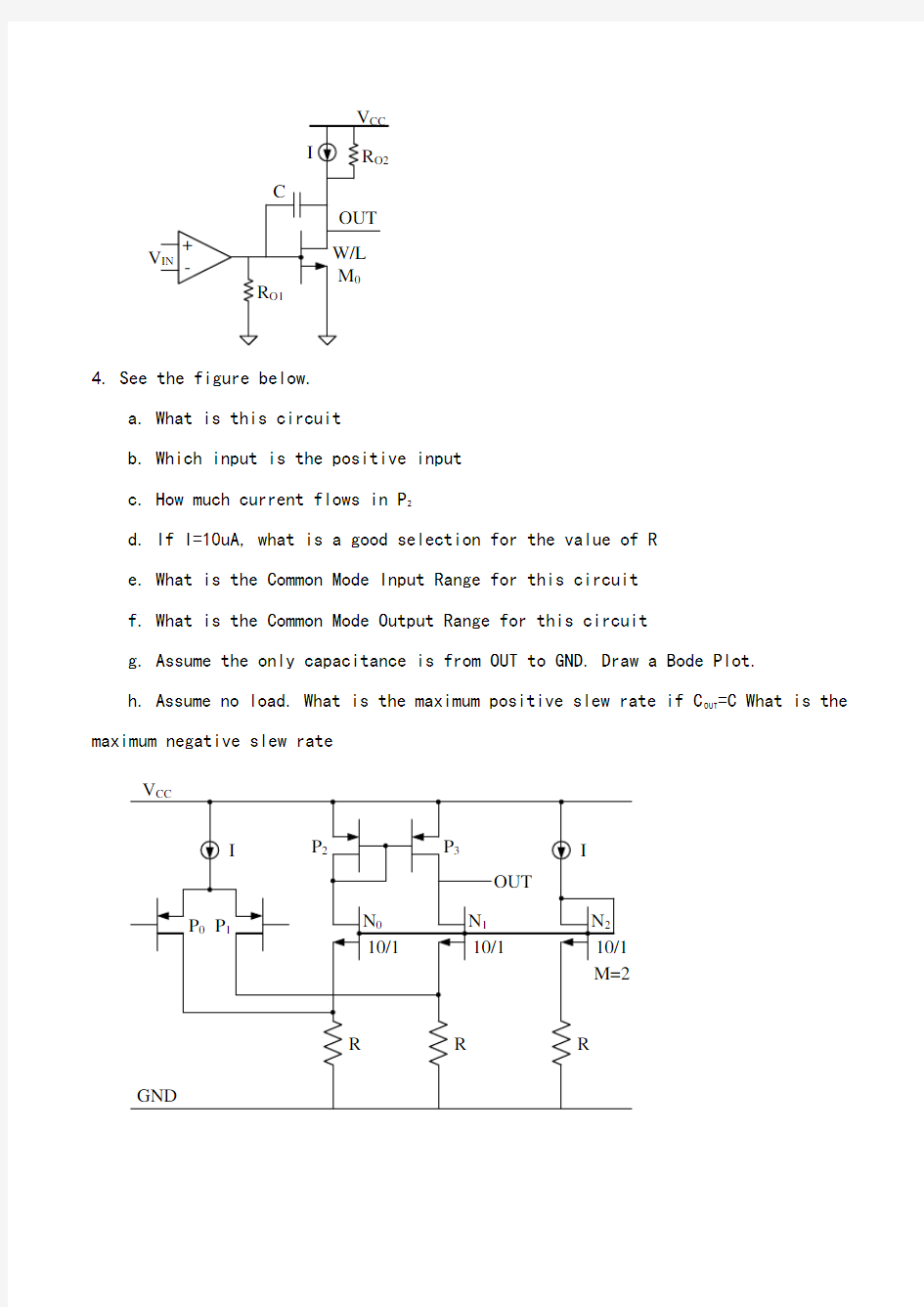

4. See the figure below.

a. What is this circuit

b. Which input is the positive input

c. How much current flows in P

2

d. If I=10uA, what is a good selection for the value of R

e. What is the Common Mode Input Range for this circuit

f. What is the Common Mode Output Range for this circuit

g. Assume the only capacitance is from OUT to GND. Draw a Bode Plot.

=C What is the

h. Assume no load. What is the maximum positive slew rate if C

OUT

maximum negative slew rate

5. See the figure below.

Assume at time=0 inductor current is 0A. Draw inductor current, V

X and V

OUT

vs. time.

I

6. See the figure below.

a. What is this circuit

b. What is the desired ratio R

2/R

1

c. How many stable points does this circuit have

d. Assume R

1 and R

2

have no Temperature Coefficient. Draw a graph of I in R

2

vs.

Temperature.

e. What is the minimum supply voltage necessary for this circuit to work properly

OUT

7. See the figure below.

a. Write the gain equation of each circuit.

b. Assuming V O =0 at time 0. Sketch V O (t) for the given input signal.

A

B

C

8. Draw Buck Converter Circuit and key waveform, explain the basic operations at steady state.

Other

Must Answer (Question 1-3)

Question 1:

Write the V/I relationship equations for resistor (R), capacitor (C), and inductor (L).

Question 2:

Given V

B in Table 1, please calculate V

C

and V

E

. Assumptions: beta of NPN is infinity,

P-N junction forward voltage drop is .

Question 3:

假设图中理想放大器工作在深度负反馈状态,请计算下图输出端电压(V

)。

OUT

For Test Engineer (Question 4-5)

Question 4:

用C语言写一个递归算法求N!

Question 5:

C语言题目

a. 在编译环境下,下列类型变量需要占几个字节内存:

int

float

double

long

char

unsigned char

b. 以下程序的输出结果:

#define ADD(x) (x)+(x)

main()

{

int a=4, b=6, c=7, d=ADD(a+b)*c;

printf(“d=%d\n”,d);

}

c. 设int a=7,b=9,t;执行完表达式t=(a>b)a:b;后,t的值是

d. 设计一个排序函数,并同时获得最大值,最小值,均方根。函数名、排序数列等自行定义。

For AE Engineer (Question 6-8)

Question 6:

a. What is this circuit shown in the Figure

C1

b. Please draw the waveforms for V

2

for three cases (use the same scale):

C 1=open, R

3

=1k;

R 3=open, C

1

=1uF;

R 3=1k, C

1

=1uF.

0V

0V Question 7:

Draw bode plots of V

O /V

I

(gain and phase) for the circuit shown below. Please label

the proper pole/zero location.

V I

O

Case 1: R3=open

Case 2: R3=1K

Question 8:

Figure below shows a simple buck converter. The switching frequency of the converter is 1MHz.

L 1

I OUT

a. V IN =10V, V OUT =4V, I OUT =5A, what is the ON time of Q 2

b. Draw waveforms of V SW and I L1 below (under the same time scale of V G -V SW ). Assumption: I OUT =5A.

For Layout Engineer (Question 9-12)

Question 9: 简述CMOS 工艺流程。

Question 10:

Draw the layout of a two-input NAND gate.

Z

A

B

Question 11:

下面电路图中有两个MOSFET(M

A and M

B

)

。假设每个MOSFET有两个gate figure,右下版图应

该如何连接,才能使M

A

和M

B

匹配。

Question 12:

画出不同的电流镜图,并简述各自特点。

南航电气硕士2013就业情况

电机与电器: 中国船舶重工集团公司第七一六研究所 中国电子科技集团第二十一研究所 中国商飞民用飞机试飞中心 中国商用飞机有限责任公司上海飞机设计研究江苏省电力公司检修分公司扬州检修分部 南京南瑞太阳能科技有限公司 合肥高新技术产业开发区人力资源开发管理中心华为技术有限公司南京研究所 南京埃斯顿自动化股份有限公司 南京埃斯顿自动化股份有限公司 南京埃斯顿自动化股份有限公司 深圳市南方安华电子科技有限公司 无锡小天鹅股份有限公司 英飞特电子股份有限公司 飞利浦(中国)投资有限公司 海拉(上海)管理有限公司南京研发分公司 杭州茂力半导体技术有限公司 杭州茂力半导体技术有限公司 联合汽车电子有限公司 路斯特传动系统(上海)有限公司 梅特勒-托利多(常州)测量技术有限公司 南京迈瑞生物医疗电子有限公司 矽力杰半导体技术(杭州)有限公司 电力电子与电力传动: 成都飞机设计研究所 航天科技集团公司第五研究院通信卫星事业部上海飞机客户服务有限公司 上海空间电源研究所 上海空间电源研究所 上海空间电源研究所 上海空间电源研究所 上海空间电源研究所 中国电子科技集团公司第二十一研究所 中国电子科技集团公司第四十三研究所 中国航天科工集团第二研究院206所 中国商用飞机有限责任公司上海飞机设计研究中航(上海)航空无线电电子技术有限公司 中航工业雷达与电子设备研究院 中航工业洛阳613所 国电南瑞科技股份有限公司 国电南瑞科技股份有限公司 南京南瑞继保电气有限公司

南京南瑞继保电气有限公司 南京苏美达动力产品有限公司 上海市电力公司 宿迁供电公司 阳光电源(上海)有限公司 中电电气太阳能研究院 南京埃斯顿自动化股份有限公司 南京普国科技有限公司 上海联影医疗科技有限公司 苏州汇川技术有限公司 国家知识产权局专利局专利审查协作江苏中心德州仪器半导体技术(上海)有限公司 德州仪器半导体技术(上海)有限公司 德州仪器半导体技术(上海)有限公司 德州仪器半导体技术(上海)有限公司 飞利浦中国照明事业部 飞思卡尔半导体(中国)有限公司上海分公司江森自控空调冷冻设备(无锡)有限公司 西门子数控(南京)有限公司 矽力杰半导体技术(杭州)有限公司 矽力杰半导体技术(杭州)有限公司 电力系统及自动化: 上海飞机制造有限公司 中国电子科技集团公司第四十三研究所 中国航空工业集团公司金城南京机电液压工程中国电子科技集团公司第二十一所 长园深瑞继保自动化有限公司南京办事处 国电南瑞科技股份有限公司 国电南瑞科技股份有限公司 南京南瑞继保电气有限公司 南京南瑞集团公司 阳光电源(上海)有限公司 南京亚派科技实业有限公司 上海科梁信息工程有限公司 苏州汇川技术有限公司 苏州汇川技术有限公司 无锡市硅动力微电子股份有限公司 亚派科技(南京) 正德职业技术学院 杭州茂力半导体技术有限公司 杭州茂力半导体技术有限公司 合肥阳光 江森自控空调冷冻设备(无锡)有限公司

【CN209496332U】一种电源管理系统【专利】

(19)中华人民共和国国家知识产权局 (12)实用新型专利 (10)授权公告号 (45)授权公告日 (21)申请号 201920426318.4 (22)申请日 2019.03.29 (73)专利权人 矽力杰半导体技术(杭州)有限公 司 地址 310051 浙江省杭州市滨江区西兴街 道联慧街6号 (72)发明人 陈建淳 王忠富 (51)Int.Cl. G06F 1/26(2006.01) (54)实用新型名称 一种电源管理系统 (57)摘要 公开了一种电源管理系统,主电源管理单元 通过通信接口与至少一个子电源管理单元连接, 以实现同步控制,从而使得控制方式灵活,可以 方便地增加子电源管理单元而无需改变具体电 路,同时减少引脚的数量, 节省芯片体积与成本。权利要求书1页 说明书3页 附图4页CN 209496332 U 2019.10.15 C N 209496332 U

权 利 要 求 书1/1页CN 209496332 U 1.一种电源管理系统,其特征在于,包括: 至少一个子电源管理单元,以实现功率转换;以及 主电源管理单元,被配置通过通信接口实现与所述至少一个子电源管理单元的同步控制。 2.根据权利要求1所述的电源管理系统,其特征在于,所述电源管理系统还包括: 通用寄存器,用于存储指令信息,从而控制所述至少一个子电源管理单元与所述主电源管理单元的工作状态。 3.根据权利要求2所述的电源管理系统,其特征在于,所述通用寄存器与所述主电源管理单元位于同一封装体中。 4.根据权利要求2所述的电源管理系统,其特征在于,所述主电源管理单元可以访问通用寄存器中的数据并写入所述至少一个子电源管理单元,从而实现同步控制。 5.根据权利要求1所述的电源管理系统,其特征在于,所述至少一个子电源管理单元包括升压拓扑、降压拓扑或升降压拓扑。 6.根据权利要求1所述的电源管理系统,其特征在于,所述至少一个子电源管理单元独立于所述主电源管理单元而封装。 2

华科电气就业统计

声明:以下数据来源于白云黄鹤,我按时间顺序整理了下。仅做参考,含一定隐私因素,请不要大肆传播。 @13华科电气考研群226529052 【2009届硕士】 电工理论与新技术曾××男统分广东电网公司佛山供电局电工理论与新技术陈××男统分广东省佛山电力设计院有限公司 电工理论与新技术陈××男统分广东天联工程有限公司 电工理论与新技术马××女统分国网电力科学研究院 电工理论与新技术黎××男统分湖南省电力公司超高压管理局 电工理论与新技术张××男统分华中科技大学录博 电工理论与新技术沈××男统分江苏省电力公司常州供电公司 电工理论与新技术叶××男统分南京供电公司 电工理论与新技术李××男统分山特电子(深圳)有限公司电机与电器杨××男统分阿海珐电力自动化有限公司 电机与电器刘××男统分东方电气集团东方电机有限公司 电机与电器肖××男统分东方电气集团东方电机有限公司 电机与电器李××男统分广东省电力工业局试验研究所 电机与电器王××男统分广东省信息技术应用研究所 电机与电器吴××男统分国电南京自动化股份有限公司 电机与电器国××男统分国网电力科学研究院 电机与电器赵××男统分国网电力科学研究院 电机与电器唐××男统分湖北省电力公司宜昌供电公司 电机与电器邓××男统分湖南送变电勘察设计咨询有限公司电机与电器程××男统分华中科技大学录博 电机与电器段××男统分华中科技大学录博 电机与电器刘××男统分华中科技大学录博 电机与电器刘××男统分华中科技大学录博 电机与电器冯××女统分华中科技大学录博 电机与电器曾××男统分华中科技大学录博

电机与电器娄××男统分华中科技大学录博 电机与电器涂××男统分华中科技大学录博 电机与电器牟××男统分清华大学录博 电机与电器徐××男统分上海电气电站设备有限公司上海发电机厂 电机与电器叶××男统分上海电气电站设备有限公司上海发电机厂 电机与电器黄××女统分上海市机电工业学校 电机与电器高××女统分台达能源技术(上海)有限公司电机与电器夏××男统分武汉都市环保工程技术股份有限公司 电机与电器盛×× 男统分武汉都市环保工程技术股份有限公司 电机与电器汪××男统分武警湖北省公安消防总队 电机与电器严××男统分伊博电源(杭州)有限公司 电机与电器王××男统分中国医药集团武汉医药设计院 电机与电器张××男统分中冶南方(武汉)自动化有限公司电力电子与电力传动刘××男统分安庆市教育局 电力电子与电力传动闫××男定向海南省三亚市亚龙湾××部队169 电力电子与电力传动曹××男统分杭州矽力杰半导体技术有限公司 电力电子与电力传动张××男统分航天科工集团二院二十三所 电力电子与电力传动李××男统分河北省电力勘测设计研究院 电力电子与电力传动佘××男统分湖北省高校毕业生就业指导服务中心 电力电子与电力传动周××男统分湖北省高校毕业生就业指导服务中心 电力电子与电力传动熊××男统分湖北省高校毕业生就业指导服务中心 电力电子与电力传动童××男统分华中科技大学录博 电力电子与电力传动刘××男统分华中科技大学录博 电力电子与电力传动刘××男统分华中科技大学录博 电力电子与电力传动姚××男统分华中科技大学录博 电力电子与电力传动李××男统分华中科技大学录博

矽力杰半导体技术(杭州)有限公司_招标190923

招标投标企业报告 矽力杰半导体技术(杭州)有限公司

本报告于 2019年9月23日 生成 您所看到的报告内容为截至该时间点该公司的数据快照 目录 1. 基本信息:工商信息 2. 招投标情况:招标数量、招标情况、招标行业分布、投标企业排名、中标企业 排名 3. 股东及出资信息 4. 风险信息:经营异常、股权出资、动产抵押、税务信息、行政处罚 5. 企业信息:工程人员、企业资质 * 敬启者:本报告内容是中国比地招标网接收您的委托,查询公开信息所得结果。中国比地招标网不对该查询结果的全面、准确、真实性负责。本报告应仅为您的决策提供参考。

一、基本信息 1. 工商信息 企业名称:矽力杰半导体技术(杭州)有限公司统一社会信用代码:91330100673960735E 工商注册号:330100400019553组织机构代码:673960735 法定代表人:Wei Chen成立日期:2008-04-22 企业类型:有限责任公司(外国法人独资)经营状态:存续 注册资本:6852万美元 注册地址:浙江省杭州市西湖区文三路90号71幢A1501-A1505、A1509-A1511室 营业期限:2008-04-22 至 2028-04-21 营业范围:技术开发、技术服务、成果转让:系统集成,集成电路及模块,半导体,电子产品;生产、测试、安装:高功率密度、高效率单片电源芯片;销售自产产品(国家禁止和限制的项目除外,涉及许可证的凭证经营)。 联系电话:*********** 二、招投标分析 2.1 招标数量 企业招标数: 个 (数据统计时间:2017年至报告生成时间)2

晶丰明源、昂宝、矽力杰与茂捷半导体替换型号

晶丰明源、昂宝、矽力杰与茂捷半导体兼容型号 晶丰明源兼容型号 M8900兼容BP3319M PSR+PFC,外置MOS,驱动性更强,PF>0.9,内置LED短路和开路保护,高效率,隔离式 M8911 兼容 BP3315D 、M8911A 兼容 BP3315D 、M8912 兼容BP3316D PSR+PFC,内置MOS,高PFC值,PSR系列,省光耦和431,节省成本空间,安全性高。 M8915 兼容BP2325A、M8916兼容BP2326A、M8918兼容BP2328A 非隔离+高PF+内置MOS,有源功率因数校正,高PF值,低THD ,效率高,多重保护功能以加强系统可靠性,包括开路保护、短路保护、芯片供电欠压保护等。变压器体积大大缩小,无输出的整流滤波等器件,减少成本。 M8919兼容BP2329A BUCK架构,非隔离+外置MOS,与PSR相比,它的PFC值较高,效率较高,变压器体积大大缩小,无输出的整流滤波等器件,减少成本,但非隔离的是热地,安全性相对较低。 M8831兼容BP2831A、M8832兼容BP2832A、M8833兼容BP2833D、M8836兼容BP2836D 非隔离+内置MOS+单绕组,降压型恒流驱动,多重保护功能以加强系统可靠性,包括开路

保护、短路保护、欠压保护等无需辅助绕组检测和供电,只需要很少的外围元件,即可实现优异的恒流特性,极大的节约了系统成本和体积。 昂宝兼容型号 M5573兼容OB2263,OB2273、M5576兼容OB2269(管脚不容) SSR+外置MOS管,各种保护功能,待机功耗<100mW,抖频功能,65KHz,高性能PWM控制器,过温保护,欠压保护,高性能PWM控制。SSR电压电流精度高, M5576最大待机功耗〔100mW〕高效率:〔24V5A平均效率>89%〕,轻载,空载无异响声 M5358兼容OB2358 低待机功耗,抖频功能,50KHz,各种保护功能,高性能PWM控制器,SSR性能稳定,动态响应好,输出电压精度高,适用于对电压精度要求高的应用领域 M5832兼容OB2532 PSR+外置MOS,各种保护功能,PSR成本低,节省PCB板上空间,省掉光耦和431,节省成本 M5835兼容OB2535、M5836兼容OB2536、M5838兼容OB2538 PSR内置MOS有线补功能,各种保护功能,PSR成本低,节省PCB板上空间,省掉光耦和431,节省成本