第七章 半导体存储器习题

第七章半导体存储器习题

[本次习题要求6月4日交]

7.1填空题:

1.半导体存储器从读、写的功能上可分为ROM和()两大类。

2.工作中既可以读出信息,又可写入信息的存储器称为()。

3.根据存储单元电路结构和工作原理的不同,将RAM分为静态RAM和()RAM 两类。

4.一个ROM共有10根字线(地址线),8根位线(数据线),则其存储容量为()。

A.10×28;

B.102×8;

C.10×82;

D.210×8。

5.容量为8K×8位的RAM芯片,其地址线和数据线各为()。

A.8和8根;

B.10和8根;

C.13和8根;

D.8和13根。

6.要扩展成32K×16位的ROM,需要()片32K×8位的ROM。

7.为了构成4096×8位的RAM,需要()片1024×2位的RAM。

8.关于半导体存储器的描述,下列哪种说法是错误的是()。

A.RAM读写方便,但一旦掉电,所存储的内容就会全部丢失。

B.ROM掉电以后数据不会丢失。

C.RAM可分为静态RAM和动态RAM。

D.动态RAM不必定时刷新。

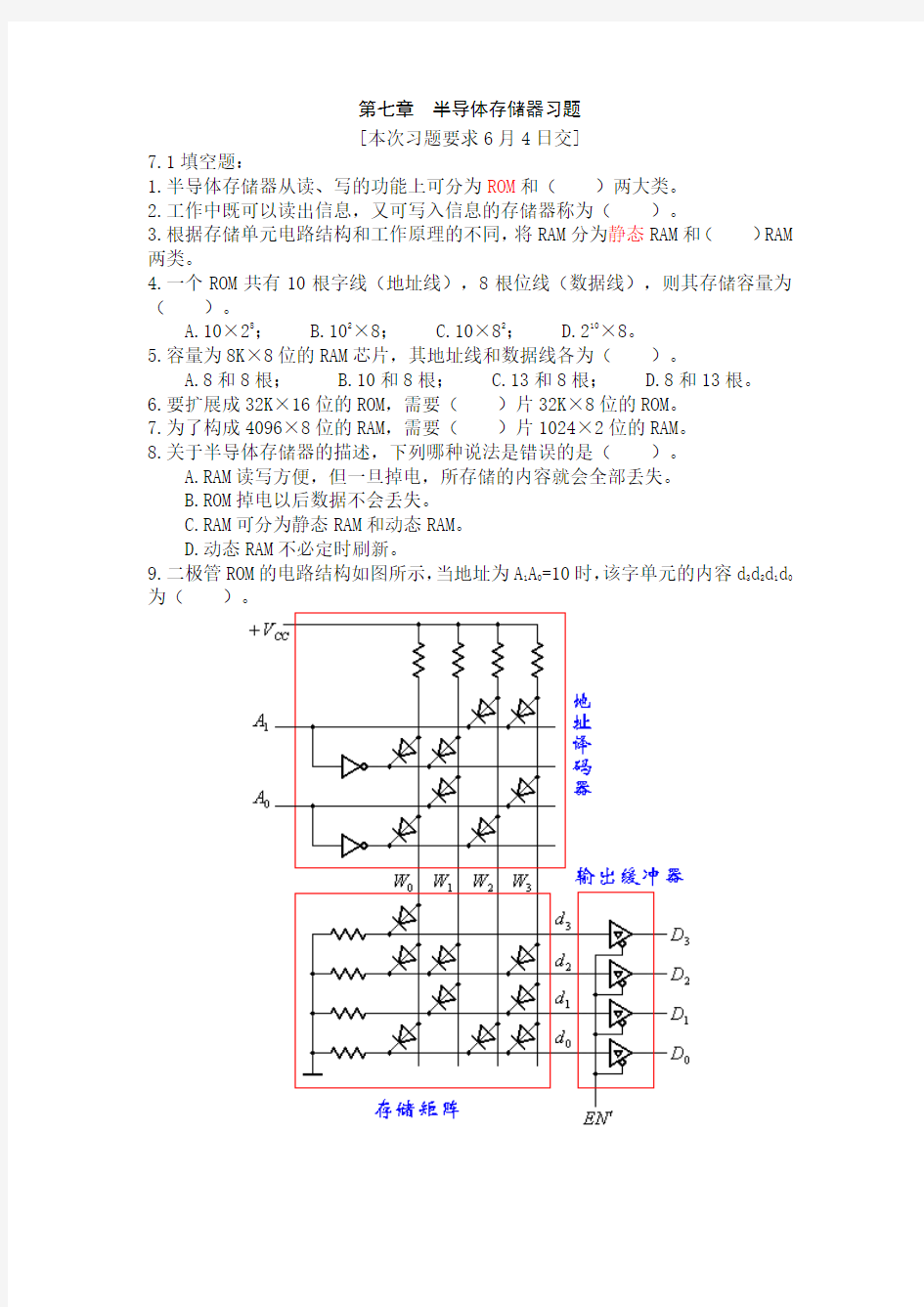

9.二极管ROM的电路结构如图所示,当地址为A

1A

=10时,该字单元的内容d

3

d

2

d

1

d

为()。

10.ROM阵列逻辑图如图所示,当地址为A

1A

=10时,该字单元的内容D

3

D

2

D

1

D

为

()。

A.1l10;

B.0111;

C.1010;

D.0100。

7.2试用2片1024×4位的RAM(2114)接成1024×8位的存储器。

7.3试用2片1024×4位的RAM(2114)接成2048×4位的存储器。

7.4用4×6位的ROM设计一个六段显示译码器。六段显示器如图所示(图中e 是水平线,f是垂直线)。它可以显示东南西北四个方向之一,实心线表示亮,虚心线表示不亮。

显示东南西北四个方向之一由ROM的两位地址输入码A

1和A

控制,控制要

求如下表所示。即六段显示译码器的输入为A

1和A

,并使输出a~f中适当的段

亮。设输出逻辑1表示亮,逻辑0表示不亮。

要求列出ROM

7.5试用8×2位容量的ROM设计一个能实现两个一位二进制数全加的逻辑电路。

输入为被加数A

i 、加数B

i

及来自低位的进位C

i-1

;输出为和S

i

及向高位的进位C

i

。

要求:(1)列出真值表;(2)直接在下图中画出用ROM点阵图实现全加的电路。

7.6由一片256×8位的EPROM 构成的数码转换器,将8位二进制原码转换成等值的补码,最高位为符号位。问:当地址输入A 7……A 1A 0分别为0000 0000、0000 0001、1000 0001、1111 1111时,EPROM 中对应地址中的数据D 7……D 1D 0各为何值?将你的答案填写地下表中。

第10章 半导体存储器汇总

第10章半导体存储器 10.1 学习要求 (1)理解只读存储器的基本工作原理。 (2)掌握用只读存储器进行逻辑设计的方法。 (3)了解随机存取存储器的基本工作原理。 (4)了解扩展存储器容量的方法。 10.2 学习指导 本章重点: (1)只读存储器的工作原理。 (2)利用只读存储器进行逻辑设计。 本章难点: (1)只读存储器的工作原理。 (2)利用只读存储器进行逻辑设计。 本章考点: (1)利用只读存储器实现各种组合逻辑函数。 (2)利用只读存储器实现给定功能的逻辑电路。 (3)与、或阵列图的意义和用法。 10.2.1 只读存储器(ROM) 1.ROM的结构 ROM由地址译码器、存储矩阵和读出电路组成,如图10.1所示。ROM的特点是存入的内容固定不变,工作时只能读出(取出),不能存入(写入),且在断电后存入的信息仍能保持,常用于存放固定的信息。 存储矩阵是存储器的主体,由大量的存储单元组成。一个存储单元只能存储1位二进制数码1或0。通常数据和指令用M位的二进制数表示,称为一个字,M为字长。M个存储单元为一组,存储一个字,称为字单元。每个字单元有一个地址,按地

电子技术学习指导与习题解答 246 址来选择所需要的字。图10.1中W 0、W 1、…、1N -W 称为字单元的地址选择线,简称字线;D 0、D 1、…、1M -D 称为输出信息的数据线,简称位线。存储矩阵有N 条字线和M 条位线,M N ?表示存储器的存储容量,这是存储器的主要技术指标之一。 地址译码器的作用是根据输入的地址代码011n A A A -,从N (n N 2=)条字线中选择一条字线,以确定与地址代码相对应的字单元的位置。至于选择哪—条字线,则决定于输入的是哪一个地址代码。任何时刻,只能有一条字线被选中。被选中的那条字线所对应的字单元中的各位数码便经M 条位线传送到数据输出端。 A 0A 1 A 0 地 址输入 数据输出 … 图10.1 ROM 的结构示意图 2.ROM 的工作原理 如图10.2所示是一个由二极管构成的容量为44?的ROM 。 A 0 地址输入 地址译码器 存储矩阵 A 1 图10.2 二极管ROM 电路

数字电路与逻辑设计习题7第七章半导体存储器(精)

第七章半导体存储器 一、选择题 1.一个容量为1K ×8的存储器有个存储单元。 A.8 B.8K C.8000 D.8192 2.要构成容量为4K ×8的R AM ,需要片容量为256×4的R AM 。 A.2 B.4 C.8 D. 32 3.寻址容量为16K ×8的RAM 需要根地址线。 A.4 B. 8 C.14 D. 16 E.16K 4.若R AM 的地址码有8位,行、列地址译码器的输入端都为4个,则它们的 输出线(即字线加位线)共有条。 A.8 B.16 C.32 D.256 5.某存储器具有8根地址线和8根双向数据线,则该存储器的容量为。 A.8×3 B.8K ×8 C. 256×8 D. 256×256 6. 采用对称双地址结构寻址的1024×1的存储矩阵有。 A.10行10列 B.5行5列 C.32行32列 D. 1024行1024列 7.随机存取存储器具有功能。 A. 读/写 B. 无读/写 C. 只读 D. 只写 8.欲将容量为128×1的R AM 扩展为1024×8,则需要控制各片选端的辅助译

码器的输出端数为。 A.1 B.2 C.3 D. 8 9.欲将容量为256×1的R AM 扩展为1024×8,则需要控制各片选端的辅助译 码器的输入端数为。 A.4 B.2 C.3 D. 8 10.只读存储器ROM 在运行时具有功能。 A. 读/无写 B. 无读/写 C. 读/写 D. 无读/无写 11.只读存储器R OM 中的内容,当电源断掉后又接通,存储器中的内容。 A. 全部改变 B. 全部为0 C. 不可预料 D. 保持不变 12.随机存取存储器RAM 中的内容,当电源断掉后又接通,存储器中的内容。 A. 全部改变 B. 全部为1 C. 不确定 D. 保持不变 13.一个容量为512×1的静态RAM 具有。 A. 地址线9根,数据线1根 B. 地址线1根,数据线9根 C. 地址线512根,数据线9根 D. 地址线9根,数据线512根 14.用若干R AM 实现位扩展时,其方法是将相应地并联在一起。 A. 地址线 B. 数据线 C. 片选信号线 D. 读/写线 15.PROM 的与陈列(地址译码器)是。 A. 全译码可编程阵列 B. 全译码不可编程阵列

半导体存储器分类介绍

半导体存储器分类介绍 § 1. 1 微纳电子技术的发展与现状 §1.1.1 微电子技术的发展与现状 上个世纪50年代晶体管的发明正式揭开了电子时代的序幕。此后为了提高电子元器件的性能,降低成本,微电子器件的特征尺寸不断缩小,加工精度不断提高。1962年,由金属-氧化物-半导体场效应晶体管(MOSFET)组装成的集成电路(IC)成为微电子技术发展的核心。 自从集成电路被发明以来[1,2],集成电路芯片的发展规律基本上遵循了Intel 公司创始人之一的Gordon Moore在1965年预言的摩尔定律[3]:半导体芯片的集成度以每18个月翻一番的速度增长。按照这一规律集成电路从最初的小规模、中规模到发展到后来的大规模、超大规模(VLSI),再到现在的甚大规模集成电路(ULSI)的发展阶段。 随着集成电路制造业的快速发展,新的工艺技术不断涌现,例如超微细线条光刻技术与多层布线技术等等,这些新的技术被迅速推广和应用,使器件的特征尺寸不断的减小。其特征尺寸从最初的0.5微米、0.35 微米、0.25 微米、0.18 微米、0.15 微米、0.13 微米、90 纳米、65 纳米一直缩短到目前最新的32纳米,甚至是亚30纳米。器件特征尺寸的急剧缩小极大地提升了集成度,同时又使运算速度和可靠性大大提高,价格大幅下降。随着微电子技术的高速发展,人们还沉浸在胜利的喜悦之中的时候,新的挑战已经悄然到来。微电子器件等比例缩小的趋势还能维持多久?摩尔定律还能支配集成电路制造业多久?进入亚微米领域后,器件性能又会有哪些变化?这一系列的问题使人们不得不去认真思考。20世纪末

期,一门新兴的学科应运而生并很快得到应用,这就是纳电子技术。 §1.1.2 纳电子技术的应用与前景 2010年底,一篇报道英特尔和美光联合研发成果的文章《近距离接触25nm NAND闪存制造技术》[4],让人们清楚意识到经过近十年全球范围内的纳米科技热潮,纳电子技术已逐渐走向成熟。电子信息技术正从微电子向纳电子领域转变,纳电子技术必将取代微电子技术主导21世纪集成电路的发展。 目前,半导体集成电路的特征尺寸已进入纳米尺度范围,采用32纳米制造工艺的芯片早已问世,25纳米制造技术已正式发布,我们有理由相信相信亚20纳米时代马上就会到来。随着器件特征尺寸的减小,器件会出现哪些全新的物理效应呢? (1)量子限制效应。当器件在某一维或多维方向上的尺寸与电子的徳布罗意波长相比拟时,电子在这些维度上的运动将受限,导致电子能级发生分裂,电子能量量子化,出现短沟道效应、窄沟道效应以及表面迁移率降低等量子特性。 (2)量子隧穿效应。当势垒厚度与电子的徳布罗意波长想当时,电子便可以一定的几率穿透势垒到达另一侧。这种全新的现象已经被广泛应用于集成电路中,用于提供低阻接触。 (3)库仑阻塞效应。单电子隧穿进入电中性的库仑岛后,该库仑岛的静电势能增大e2/2C,如果这个能量远远大于该温度下电子的热动能K B T,就会出现所谓的库仑阻塞现象,即一个电子隧穿进入库仑岛后就会对下一个电子产生很强的排斥作用,阻挡其进入。 以上这些新的量子效应的出现使得器件设计时所要考虑的因素大大增加。目

06第六章半导体存储器(2学时)

第六章半导体存储器2学时基本知识: 1、半导体存储器的基本概念、以及性能技术指标; 2、半导体存储器的功能分类; 3、SRAM存储单元的基本电路结构; 4、RAM的读/写操作; 5、掩膜ROM的基本结构与基本特性; 6、可编程ROM的基本结构与基本特性; 重点知识: 1、正确理解存储容量的概念; 2、正确理解RAM的基本结构组成; 3、熟练掌握RAM存储容量的扩展方法; 4、正确使用常规半导体存储器; 难点知识: 1、半导体存储器的结构组成的理解;

课后练习:P383-7.1.2、7.1.52、RAM存储容量的扩展方法;

序言 随着半导体集成工艺的不断进步,电路的集成度越来越高。目前,大规模集成电路LSI日新月异,LSI电路的一个重要应用领域就是半导体存储器。 半导体存储器就是存储大量二值数据的半导体器件,是数字系统必不可少的组成部分。这种存储包括:存储文字的编码数据、存储声音的编码数据、存储图像的编码数据。 衡量存储器性能的重要计数指标——存储容量(目前动态存储器的容量可达10亿位/片)、存取速度(一些高速存储器的存取时间仅10nS)。

1、存储容量 存储器由若干存储单元组成,每个存储单元存放一位二进制数。由若干二进制数组成的二进制数代码称为一个字,字所包含二进制 数的位数称为字长。 可见,存放一个字长为M的字需要M个存储单元,且M个存储单元为一个信息单元。 所以:存储容量就是字数N(信息单元)与字长M(位数)的乘积(即存储单元的总数)。 如:64M×8=512M (其中64M为字数或信息单元,8为字长或位数,512M为存储单元)

第七章 半导体存储器

第七章 半导体存储器 数字信息在运算或处理过程中,需要使用专门的存储器进行较长时间的存储,正是因为有了存储器,计算机才有了对信息的记忆功能。存储器的种类很多,本章主要讨论半导体存储器。半导体存储器以其品种多、容量大、速度快、耗电省、体积小、操作方便、维护容易等优点,在数字设备中得到广泛应用。目前,微型计算机的内存普遍采用了大容量的半导体存储器。 存储器——用以存储一系列二进制数码的器件。 半导体存储器的分类 根据使用功能的不同,半导体存储器可分为随机存取存储器(RAM —Random Access Memory )和只读存储器(ROM —Read-Only memory )。 按照存储机理的不同,RAM 又可分为静态RAM 和动态RAM 。 存储器的容量 存储器的容量=字长(n )×字数(m ) 7.1随机存取存储器(RAM ) 随机存取存储器简称RAM ,也叫做读/写存储器,既能方便地读出所存数据,又能随时写入新的数据。RAM 的缺点是数据的易失性,即一旦掉电,所存的数据全部丢失。 一. RAM 的基本结构 由存储矩阵、地址译码器、读写控制器、输入/输出控制、片选控制等几部分组成。 存储矩阵 读/写控制器 地址译码器 地 址码输片选读/写控制输入/输出 入 图7.1—1 RAM 的结构示意框图

2 1. 存储矩阵 RAM 的核心部分是一个寄存器矩阵,用来存储信息,称为存储矩阵。 图7.1—5所示是1024×1位的存储矩阵和地址译码器。属多字1位结构,1024个字排列成32×32的矩阵,中间的每一个小方块代表一个存储单元。为了存取方便,给它们编上号,32行编号为X 0、X 1、…、X 31,32列编号为Y 0、Y 1、…、Y 31。这样每一个存储单元都有了一个固定的编号(X i 行、Y j 列),称为地址。 1 1 1 1 31 31 131******** 列 译 码 器 行译码器 .. .........位线 位线 位线 位线 位线 位线 . .. . . . . X X X Y Y Y 0 1 31 131 A A A A A A A A A A 地 址 输 入 地址 输入 012 34 5 67 89 D D 数据线 . .. . 图7.1-5 1024×1位RAM 的存储矩阵 2. 址译码器 址译码器的作用,是将寄存器地址所对应的二进制数译成有效的行选信号和列选信号,从而选中该存储单元。 存储器中的地址译码器常用双译码结构。上例中,行地址译码器用5输入32输出的译码器,地址线(译码器的输入)为A 0、A 1 、…、A 4,输出为X 0、X 1、…、X 31;列地址译码器也用5输入32输出的译码器,地址线(译码器的输入)为A 5、A 6 、…、A 9,输出为Y 0、Y 1、…、Y 31,这样共有10条地址线。例如,输入地址码A 9A 8A 7A 6A 5A 4A 3A 2A 1A 0=0000000001,则行选线X 1=1、列选线Y 0=1,选中第X 1行第

半导体存储器分类

半导体存储器 一.存储器简介 存储器(Memory)是现代信息技术中用于保存信息的记忆设备。在数字系统中,只要能保存二进制数据的都可以是存储器;在集成电路中,一个没有实物形式的具有存储功能的电路也叫存储器,如RAM、FIFO等;在系统中,具有实物形式的存储设备也叫存储器,如内存条、TF卡等。计算机中全部信息,包括输入的原始数据、计算机程序、中间运行结果和最终运行结果都保存在存储器中。 存储器件是计算机系统的重要组成部分,现代计算机的内存储器多采用半导体存储器。存储器(Memory)计算机系统中的记忆设备,用来存放程序和数据。计算机中的全部信息,包括输入的原始数据、计算机程序、中间运行结果和最终运行结果都保存在存储器中。它根据控制器指定的位置存入和取出信息。自世界上第一台计算机问世以来,计算机的存储器件也在不断的发展更新,从一开始的汞延迟线,磁带,磁鼓,磁芯,到现在的半导体存储器,磁盘,光盘,纳米存储等,无不体现着科学技术的快速发展。 存储器的主要功能是存储程序和各种数据,并能在计算机运行过程中高速、自动地完成程序或数据的存取。存储器是具有“记忆”功能的设备,它采用具有两种稳定状态的物理器件来存储信息。这些器件也称为记忆元件。在计算机中采用只有两个数码“0”和“1”的二进制来表示数据。记忆元件的两种稳定状态分别表示为“0”和“1”。日常使用的十进制数必须转换成等值的二进制数才能存入存储器中。计算机中处理的各种字符,例如英文字母、运算符号等,也要转换成二进制代码才能存储和操作。 储器的存储介质,存储元,它可存储一个二进制代码。由若干个存储元组成一个存储单元,然后再由许多存储单元组成一个存储器。一个存储器包含许多存储单元,每个存储单元可存放一个字节(按字节编址)。每个存储单元的位置都有一个编号,即地址,一般用十六进制表示。一个存储器中所有存储单元可存放数据的总和称为它的存储容量。假设一个存储器的地址码由20位二进制数(即5位十六进制数)组成,则可表示2的20次方,即1M个存储单元地址。每个存储单元存放一个字节,则该存储器的存储容量为1MB。

数字逻辑技术第七章

第七章半导体存储器习题 一、选择题 1.一个容量为1K×8的存储器有个存储单元。 A.8 B.8K C.8000 D.8192 2.要构成容量为4K×8的RAM,需要片容量为256×4的RAM。 A.2 B.4 C.8 D.32 3.寻址容量为16K×8的RAM需要根地址线。 A.4 B.8 C.14 D.16 E.16K 4.若RAM的地址码有8位,行、列地址译码器的输入端都为4个,则它们的输出线(即字线加位线)共有条。 A.8 B.16 C.32 D.256 5.某存储器具有8根地址线和8根双向数据线,则该存储器的容量为。 A.8×3 B.8K×8 C.256×8 D. 256×256 6.采用对称双地址结构寻址的1024×1的存储矩阵有。 A.10行10列 B.5行5列 C.32行32列 D.1024行1024列 7.随机存取存储器具有功能。 A.读/写 B.无读/写 C.只读 D.只写 8.欲将容量为128×1的RAM扩展为1024×8,则需要控制各片选端的辅助译码器的输出端数为。 A.1 B.2 C.3 D.8 9.欲将容量为256×1的RAM扩展为1024×8,则需要控制各片选端的辅助 译码器的输入端数为。 A.4 B.2 C.3 D.8 10.只读存储器ROM在运行时具有功能。 A.读/无写 B.无读/写 C.读/写 D.无读/无写 11.只读存储器ROM中的内容,当电源断掉后又接通,存储器中的内容。 A.全部改变 B.全部为0 C.不可预料 D.保持不变 12.随机存取存储器RAM中的内容,当电源断掉后又接通,存储器中的内容。 A.全部改变 B.全部为1 C.不确定 D.保持不变 13.一个容量为512×1的静态RAM具有。 A.地址线9根,数据线1根 B.地址线1根,数据线9根 C.地址线512根,数据线9根 D.地址线9根,数据线512根 14.用若干RAM实现位扩展时,其方法是将相应地并联在一起。 A.地址线 B.数据线 C.片选信号线 D.读/写线 15.PROM的与陈列(地址译码器)是。 A.全译码可编程阵列 B. 全译码不可编程阵列 C.非全译码可编程阵列 D.非全译码不可编程阵列 二、判断题(正确打√,错误的打×) 1.实际中,常以字数和位数的乘积表示存储容量。() 2. RAM由若干位存储单元组成,每个存储单元可存放一位二进制信息。() 3.动态随机存取存储器需要不断地刷新,以防止电容上存储的信息丢失。() 4.用2片容量为16K×8的RAM构成容量为32K×8的RAM是位扩展。()5.所有的半导体存储器在运行时都具有读和写的功能。()6. ROM和RAM中存入的信息在

第6章 半导体存储器

6 习题参考答案 6.1 ROM 有哪些种类?各有何特点? 6.2 指出下列的ROM 存储系统各具有多少个存储单元,应有地址线、数据线、字线和位线各多少根? 6.3 一个有16384个存储单元的ROM ,它的每个字是8位。试问它应有多少个字?有多少根地址线和数据线? 6.4 已知 ROM 如图6.21所示,试列表说明ROM 存储的内容。 A 1 A 图6.21 题6.4的图 解: 存储的数据为01、11、00、10 6.5 ROM 点阵图及地址线上的波形图如图6.22所示,试画出数据线D 3~D 0上的波形图。 A 1 A 0 图6.22 题6.5的图

解: 10A A 3210D D D D 0 00 11 01 10 0 1 11 1 1 00 1 0 0 1 0 1 1 A 1A 0 D 0 D 1D 2 D 3 6.6 试用ROM 设计一个组合逻辑电路,用来产生下列一组逻辑函数。画出存储矩阵的 点阵图。 D B D B Y D B D A C D C B B A Y D C A D B A D C B A Y D ABC D C AB D C B A D C B A Y +=+++=++=+++=4321 解: 1234(5,10,13,14)(9,10,11,13) (1,3,4,5,6,7,9,10,11,13,14)(1,3,4,6,9,11,12,14) Y ABCD ABCD ABCD ABCD m Y ABCD ABD ACD m Y AB BCD ACD BD m Y BD BD m =+++=∑=++=∑=+++=∑=+=∑ A B C D Y 4 Y 3 Y 2 Y 1 输出 6.7 试用ROM 设计一个实现8421BCD 码到余3码转换的逻辑电路,要求选择EPROM 的容量,画出简化阵列图。 解:列写真值表,作电路图,选用16×4的EPROM 。

数字电子技术基础第四版课后答案7

第七章半导体存储器 [题] 存储器和寄存器在电路结构和工作原理上有何不同 [解] 参见第节。 [题] 动态存储器和静态存储器在电路结构和读/写操作上有何不同 [解] 参见第7.3.1节和第节。 [题] 某台计算机的内存储器设置有32位的地址线,16位并行数据输入/输出端,试计算它的最大存储量是多少 [解] 最大存储量为232×16=210×210×210×26=1K×1K×1K×26=64G [题] 试用4片2114(1024×4位的RAM)和3线-8线译码器74LS138(见图3.3.8)组成4096×4位的RAM。 [解] 见图。 [题] 试用16片2114(1024×4位的RAM)和3线-8线译码器74LS138(见图3.3.8)接成一个8K×8位的RAM。 [解] 见图。

[题] 已知ROM的数据表如表所示,若将地址输入A3A2A1A0作为4个输入逻辑变量,将数据输出D3D2D1D0作为函数输出,试写出输出与输入间的逻辑函数式。 [ 解] D3= 1 2 3 1 2 3 1 2 3 1 2 3 A A A A A A A A A A A A A A A A+ + + D2=0 1 2 3 1 2 3 1 2 3 1 2 3 1 2 3 A A A A A A A A A A A A A A A A A A A A+ + + + +0 1 2 3 A A A A D1=0 1 2 3 1 2 3 1 2 3 1 2 3 A A A A A A A A A A A A A A A A+ + + D0=0 1 2 3 1 2 3 A A A A A A A A+ [题]图是一个16×4位的ROM,A3、、A2、A1、A0为地址输入,D3、D2、D1、D0是数据输出,若将D3、D2、D1、D0视为A3、、A2、A1、A0的逻辑函数,试写出D3、D2、D1、D0的逻辑函数式。 [解]0 1 2 3 1 2 3 1 2 3 1 2 3 3 A A A A A A A A A A A A A A A A D+ + + = 1 2 3 1 2 3 1 2 3 2 A A A A A A A A A A A A D+ + = 1 2 3 1 2 3 1 2 3 1 2 3 1 2 3 1 A A A A A A A A A A A A A A A A A A A A D+ + + + = 1 2 3 1 2 3 1 2 3 1 2 3 1 2 3 A A A A A A A A A A A A A A A A A A A A D+ + + + = 1 2 3 1 2 3 A A A A A A A A+ + 地址 输入 数据 输出 地址 输入 数据 输出 A3A2A1 A0 D3D2D1 D0 A3A2A1 A0 D3D2D1 D0 0000 0001 0010 0011 0100 0101 0110 0111 0001 0010 0010 0100 0010 0100 0100 1000 1000 1001 1010 1011 1100 1101 1110 1111 0010 0100 0100 1000 0100 1000 1000 0001

半导体存储器件及其操作方法与相关技术

图片简介: 一种半导体存储器件,包括:熔丝部分,包括:第一熔丝组,具有针对第一模式分配的多个第一熔丝;以及第二熔丝组,具有针对第二模式分配的多个第二熔丝;以及编程部分,适于在所述第二模式下响应于修复控制信号而编程包括在所述第一熔丝组中的所述第一熔丝之中的可用熔丝或编程包括在所述第二熔丝组中的所述第二熔丝。 技术要求 1.一种半导体存储器件,包括: 熔丝部分,包括:第一熔丝组,具有针对第一模式分配的多个第一熔丝;以及第二熔丝组,具有针对第二模式分配的多个第二熔丝;以及 编程部分,适于在所述第二模式下响应于修复控制信号而编程包括在所述第一熔丝组中 的所述第一熔丝之中的可用熔丝或编程包括在所述第二熔丝组中的所述第二熔丝。 2.如权利要求1所述的半导体存储器件,其中,所述编程部分包括:

第一熔丝信息储存块,适于:储存对应于所述第一熔丝组的第一熔丝信息,且通过确定所述第一熔丝组是否具有所述第一熔丝之中的未使用的熔丝来产生过流信号; 第二熔丝信息储存块,适于储存对应于所述第二熔丝组的第二熔丝信息;以及 选择输出块,适于在所述第二模式下响应于所述过流信号而输出所述第一熔丝信息或所述第二熔丝信息。 3.如权利要求2所述的半导体存储器件,其中,所述编程部分还包括: 启动控制块,适于:在启动操作中确定所述第一熔丝组和所述第二熔丝组是否被使用且更新所述第一熔丝信息和所述第二熔丝信息。 4.如权利要求2所述的半导体存储器件,其中,所述编程部分还包括: 地址锁存块,适于锁存从外部器件接收的缺陷地址信息。 5.如权利要求2所述的半导体存储器件,其中,所述编程部分还包括: 断裂控制块,适于使与自所述选择输出块输出的所述第一熔丝信息或所述第二熔丝信息相对应的熔丝断裂。 6.如权利要求2所述的半导体存储器件,其中,所述第一熔丝信息储存块输出当所述第一熔丝组具有所述可用熔丝时被禁用且当所述第一熔丝组无可用熔丝时被使能的所述过流信号。 7.如权利要求2所述的半导体存储器件,其中,所述选择输出块包括: 选择控制信号发生单元,适于:接收在所述第二模式下被使能的封装后修复PPR模式使能信号、扩展模式信号和所述过流信号,且产生选择控制信号;以及 选择单元,适于响应于所述选择控制信号而选择性地输出所述第一熔丝信息或所述第二熔丝信息。 8.一种半导体存储器件,包括:

存储器的发展与技术现状.

存储器的发展史及技术现状 20122352 蔡文杰计科3班 1.存储器发展历史 1.1存储器简介 存储器(Memory)是计算机系统中的记忆设备,用来存放程序和数据。计算机中的全部信息,包括输入的原始数据、计算机程序、中间运行结果和最终运行结果都保存在存储器中。它根据控制器指定的位置存入和取出信息。自世界上第一台计算机问世以来,计算机的存储器件也在不断的发展更新,从一开始的汞延迟线,磁带,磁鼓,磁芯,到现在的半导体存储器,磁盘,光盘,纳米存储等,无不体现着科学技术的快速发展。 1.2存储器的传统分类 从使用角度看,半导体存储器可以分成两大类:断电后数据会丢失的易失性存储器和断电后数据不会丢失的非易失性存储器。过去都可以随机读写信息的易失性存储器称为RAM(Randoo Aeeess Memory),根据工作原理和条件不同,RAM又有静态和动态之分,分别称为静态读写存储器SR AM(St ate RAM)和动态读写存储器DRAM(Dynamie RAM);而过去的非易失控存储器都是只读存储RoM(Readon一y Memo-ry),这种存储器只能脱机写人信息,在使用中只能读出信息而不能写人或改变信息.非易失性存储器包含各种不同原理、技术和结构的存储器.传统的非易失性存储器根据写人方法和可写人的次数的不同,又可分成掩模只读存储器MROM(Mask ROM)、一次性编程的OTPROM(one Time Programmable ROM)和可用萦外线擦除可多次编程的Uv EPROM(Utravio-let ErasableProgrammable ROM).过去的OT PROM都是采用双极性熔丝式,这种芯片只能被编程一次,因此在测试阶段不能对产品进行编程性检侧,所以产品交付用户后,经常在编程时才会发现其缺陷而失效,有的芯片虽然能被编程,但由于其交流性不能满足要求,却不能正常运行.故双极性熔丝式PROM产品的可信度不高. 2.半导体存储器 由于对运行速度的要求,现代计算机的内存储器多采用半导体存储器。半导体存储器包括只读存储器(ROM)和随机读写存储器(RAM)两大类。 2.1只读存储器 ROM是线路最简单的半导体电路,通过掩模工艺,一次性制造,在元件正常工作的情况下,其中的代码与数据将永久保存,并且不能够进行修改。一般地,只读

第七章 半导体存储器习题

第七章半导体存储器习题 [本次习题要求6月4日交] 7.1填空题: 1.半导体存储器从读、写的功能上可分为ROM和()两大类。 2.工作中既可以读出信息,又可写入信息的存储器称为()。 3.根据存储单元电路结构和工作原理的不同,将RAM分为静态RAM和()RAM 两类。 4.一个ROM共有10根字线(地址线),8根位线(数据线),则其存储容量为()。 A.10×28; B.102×8; C.10×82; D.210×8。 5.容量为8K×8位的RAM芯片,其地址线和数据线各为()。 A.8和8根; B.10和8根; C.13和8根; D.8和13根。 6.要扩展成32K×16位的ROM,需要()片32K×8位的ROM。 7.为了构成4096×8位的RAM,需要()片1024×2位的RAM。 8.关于半导体存储器的描述,下列哪种说法是错误的是()。 A.RAM读写方便,但一旦掉电,所存储的内容就会全部丢失。 B.ROM掉电以后数据不会丢失。 C.RAM可分为静态RAM和动态RAM。 D.动态RAM不必定时刷新。 9.二极管ROM的电路结构如图所示,当地址为A 1A =10时,该字单元的内容d 3 d 2 d 1 d 为()。

10.ROM阵列逻辑图如图所示,当地址为A 1A =10时,该字单元的内容D 3 D 2 D 1 D 为 ()。 A.1l10; B.0111; C.1010; D.0100。 7.2试用2片1024×4位的RAM(2114)接成1024×8位的存储器。 7.3试用2片1024×4位的RAM(2114)接成2048×4位的存储器。 7.4用4×6位的ROM设计一个六段显示译码器。六段显示器如图所示(图中e 是水平线,f是垂直线)。它可以显示东南西北四个方向之一,实心线表示亮,虚心线表示不亮。 显示东南西北四个方向之一由ROM的两位地址输入码A 1和A 控制,控制要 求如下表所示。即六段显示译码器的输入为A 1和A ,并使输出a~f中适当的段 亮。设输出逻辑1表示亮,逻辑0表示不亮。 要求列出ROM 7.5试用8×2位容量的ROM设计一个能实现两个一位二进制数全加的逻辑电路。 输入为被加数A i 、加数B i 及来自低位的进位C i-1 ;输出为和S i 及向高位的进位C i 。 要求:(1)列出真值表;(2)直接在下图中画出用ROM点阵图实现全加的电路。

第7章 半导体存储器与可编程逻辑器件习题解答

思考题与习题 7.1 选择题 7.14 选择题 1)存储容量为8K×8位的ROM 存储器,其地址线为 条。 C A 、8 B 、12 C 、13 D 、14 2)只能按地址读出信息,而不能写入信息的存储器为 。 b A 、 RAM B 、ROM C 、 PROM D 、EPROM 3)一片ROM 有n 根地址输入,m 根位线输出,则ROM 的容量为 。a A 、m n ?2 B 、n m ? C 、m n 22? D 、n m ?2 4)一个6位地址码、8位输出的ROM ,其存储矩阵的容量为 。 A 、46 B 、64 C 、512 D 、256 5)为构成4096×8的RAM ,需要 片2024×2的RAM ,并需要有 位地址译码以完成寻址操作。 A 、8 ,15 B 、16,11 C 、10,12 D 、8,12 6)PAL 是一种的 可编程逻辑器件。 A 、与阵列可编程,或阵列固定 B 、与阵列列固,或阵可编程定 C 、与阵列、或阵列固定 D 、与阵列、或阵列可编程 7.2 试写出如图7-27所示阵列图的逻辑函数表达式和真值表,并说明其功能。 1 F 2 F 3 图6-1 例6-1逻辑图 图7-27 题7.2图 解:根据与阵列的输出为AB 的最小项和阵列图中有实心点“·”为1,无“·”为0, 可以写出: AB W F ==30 B A AB B A B A W W W F +=++=++=3211 B A B A B A F ⊕=+=2 AB B A B A B A B A W W W F =+=++=++=2103 从上述逻辑表达式可以看出,图7-1所示阵列图实现了输入变量A 、B 的四种逻辑运算:与、或、异或和与非。列出真值表如表7-1所示。 7.3 若存储器芯片的容量为128K× 8位,求: 表7-1 例7-1真值表

半导体存储器的设计与实现

半导体存储器的设计与实现 汽车与交通工程学院车辆(卓越)1101 孟礼3110401167 摘要: 本文主要采用了文献研究法,通过查阅相关互联网资料和国内外书籍,获得了大量重要的资料。内容上首先研究了半导体产业的相关知识,简述了半导体技术和存储技术的发展历程,及其对人类社会发展所产生的深刻影响;然后重点论述了半导体存储技术的研究现状和发展方向;最后综观半导体产业在国内国外的发展境况,分析世界半导体存储产业重心的转移将可能带给中国半导体产业发展的机遇与挑战。本文是在前人研究的基础上,根据目前状况合理推断未来的趋势,希望可以引起重视读者的重视,增进学术界的交流,从而对半导体存储器向前发展起到一定的积极作用。 关键词:半导体存储器、高速低耗、体积小、产业重心 The design and implementation of a semiconductor memory device School of Automotive and Traffic Engineering Vehicles (excellent)1101 MengLi3110401167 Abstract:This treatise uses a literature study, throughing search Internet information and books at home and abroad, obtaining a lot of important information. Firstly,studied the common knowledge of the semiconductor industry, outlines the development process of semiconductor technology and storage technology, and its profound impact on the development of human

第七章 半导体存储器

第七章 半导体存储器内容提要 本章将系统地介绍各种半导体存储器的工作原理和使用方法。半导体存储器包括只读存储器(ROM ) RAM )。)。在只读存储器中,介绍了 在只读存储器中,介绍了和快闪存储器等不同类型的ROM 的工作原理和特点;而在随机存储器中,介绍了静态RAM (SRAM )和动态RAM (DRAM )两种类型。此外,也介绍了存储器扩展容量的连接方法以及用存储器设计组合逻辑电路,重点放在这里。

本章内容 7.5 用存储器实现组合逻辑函数

1. 半导体存储器的定义 路,由于计算机以及一些数字系统中要存储大量的数据,因此存储器是数字系统中不可缺少的组成部分,7.1.1所示。 输入 / 出 电 路I/O 输入输入//出控制图7.1.1

2.存储器的性能指标 存储量和存取速度作为衡量存储器的重要性能指标。 片,一些高速存储 3.半导体存储器的分类 (1)从存取功能上分类 从存取功能上可分为只读存储器( Memory,简称ROM)和随机存储器( Access Memory,简称RAM

a. ROM a. ROM 、可编程ROM(Programmable PROM)和可擦除的可编程ROM(Erasable Programmable Read-Only Memory,简称EPROM)。 *掩模ROM在制造时,生产厂家利用掩模技术把数据写入存储器中,一旦ROM 定不变,无法更改。

(或者全为0),用户可根据自己的需要写入,利用通用或专用的编程 1)。 是采用浮栅技术的可编程存储器,其数据不但可以由用户根据自己的需要写入,而且还能擦除重写,所以具有较大的使用灵活性。它的数据的写入需要通用或专用的编程器,其擦除为照射擦除,为一次全部擦除。电擦除的PROM ROM。