浅谈对FPGA约束中input delay和output delay的理解

外部器件发送数据到FPGA系统模型如图1所示。对FPGA的IO口进行输入最大最小延时约束是为了让FPGA设计工具能够尽可能的优化从输入端口到第一级寄存器之间的路径延迟,使其能够保证系统时钟可靠的采到从外部芯片到FPGA的信号。

图1 FPGA数据输入模型

输入延时即为从外部器件发出数据到FPGA输入端口的延时时间。其中包括时钟源到FPGA延时和到外部器件延时之差、经过外部器件的数据发送Tco,再加上PCB板上的走线延时。如图2所示,为外部器件和FPGA接口时序。

图2外部器件和FPGA接口时序

Input delay定义了从外部芯片输入到fpga的数据相对于输入到fpga时钟管脚的时间延迟,从上图2可以得出input delay=Tclk1+Tco+Tpcb-Tclk2=Tpcb-(Tclk2-Tclk1)+Tco;

因此,input delay max = Tpcb(max) –(Tclk2(min)–Tclk1(max)) + Tco(max)

input delay min = Tpcb(min) –(Tclk2(max)–Tclk1(min)) + Tco(min) 通常Tpcb和Tclk都是常数,因此Tco的最大最小值决定了input delay的最大最小值。

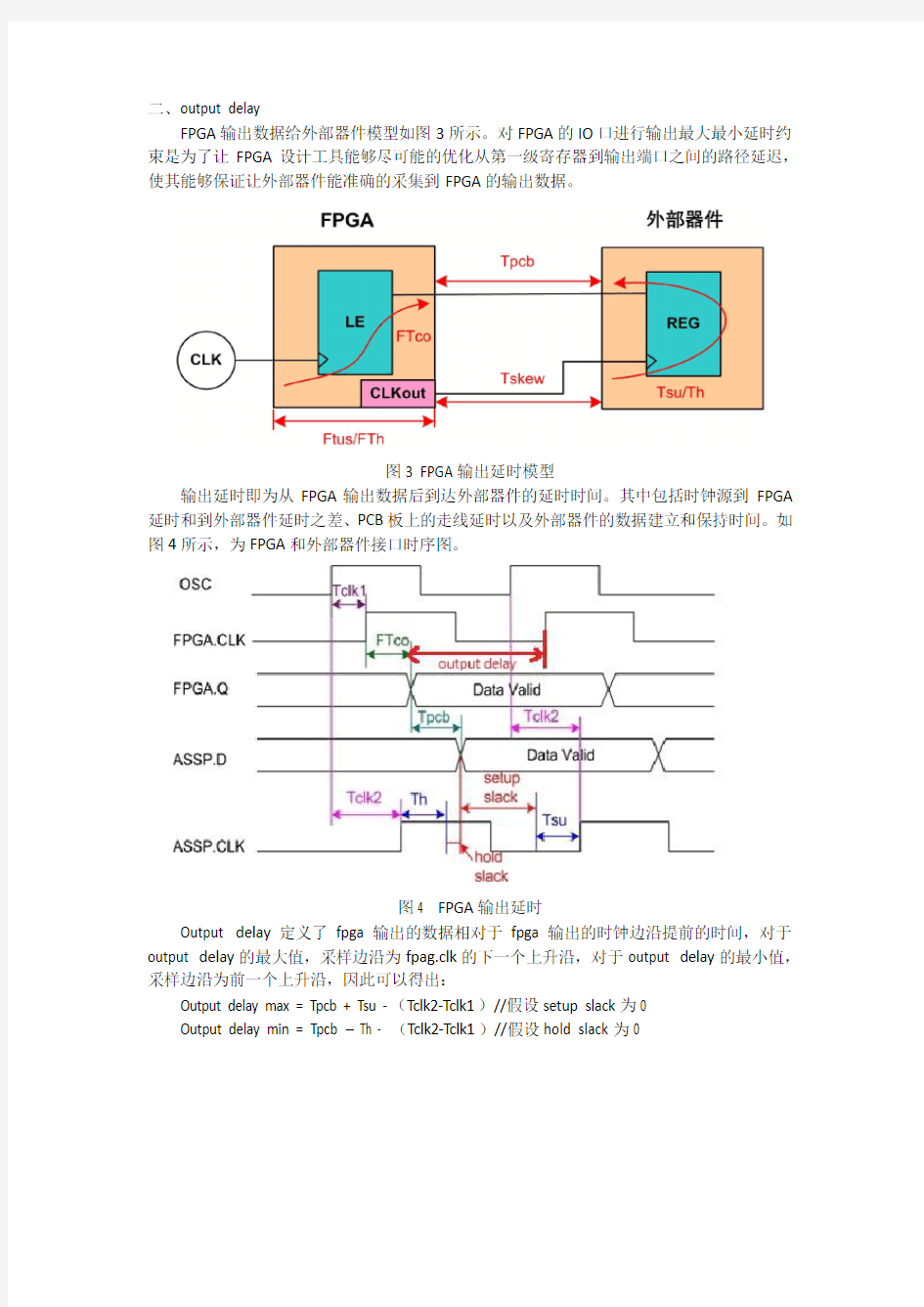

FPGA输出数据给外部器件模型如图3所示。对FPGA的IO口进行输出最大最小延时约束是为了让FPGA设计工具能够尽可能的优化从第一级寄存器到输出端口之间的路径延迟,使其能够保证让外部器件能准确的采集到FPGA的输出数据。

图3 FPGA输出延时模型

输出延时即为从FPGA输出数据后到达外部器件的延时时间。其中包括时钟源到FPGA 延时和到外部器件延时之差、PCB板上的走线延时以及外部器件的数据建立和保持时间。如图4所示,为FPGA和外部器件接口时序图。

图4 FPGA输出延时

Output delay定义了fpga输出的数据相对于fpga输出的时钟边沿提前的时间,对于output delay的最大值,采样边沿为fpag.clk的下一个上升沿,对于output delay的最小值,采样边沿为前一个上升沿,因此可以得出:

Output delay max = Tpcb + Tsu -(Tclk2-Tclk1)//假设setup slack为0

Output delay min = Tpcb – Th - (Tclk2-Tclk1)//假设hold slack为0