JTAG通用文件

AN 586: 将Jam STAPL和

Jam STAPL字节码播放器

移植到嵌入式系统AN-586-1.0 Application Note Jam? 标准测试和编程语言(STAPL) 与Jam STAPL 字节码(JBC) 播放器,是让处理器

能够将Jam 文件(.jam)或Jam 字节码文件(.jbc)基于一定算法对CPLD 或FPGA 器件进行编程或配置的软件。

引言

本应用手册向您介绍将Jam STAPL 和Jam STAPL JBC播放器移植到嵌入式系统时您需要知道的一些函数相关资料。

本应用手册不提供举例,因为移植所要求的改动取决于您使用的嵌入式系统和操作系统。Jam STAPL或JBC播放器移植概览

Jam STAPL 或JBC 播放器的功能主要是解释和执行.jam 或.jbc 中所有的Jam STAPL 或JBC 指令。主程序完成Jam 或JBC 播放器的所有基本功能。对于所要使用的嵌入式系统,您必须对Jam 或JBC 播放器的I/O 函数进行修改,来定制函数以适应要使用的嵌入式处理器或操作系统,例如:Freescale? V2 ColdFire处理器。

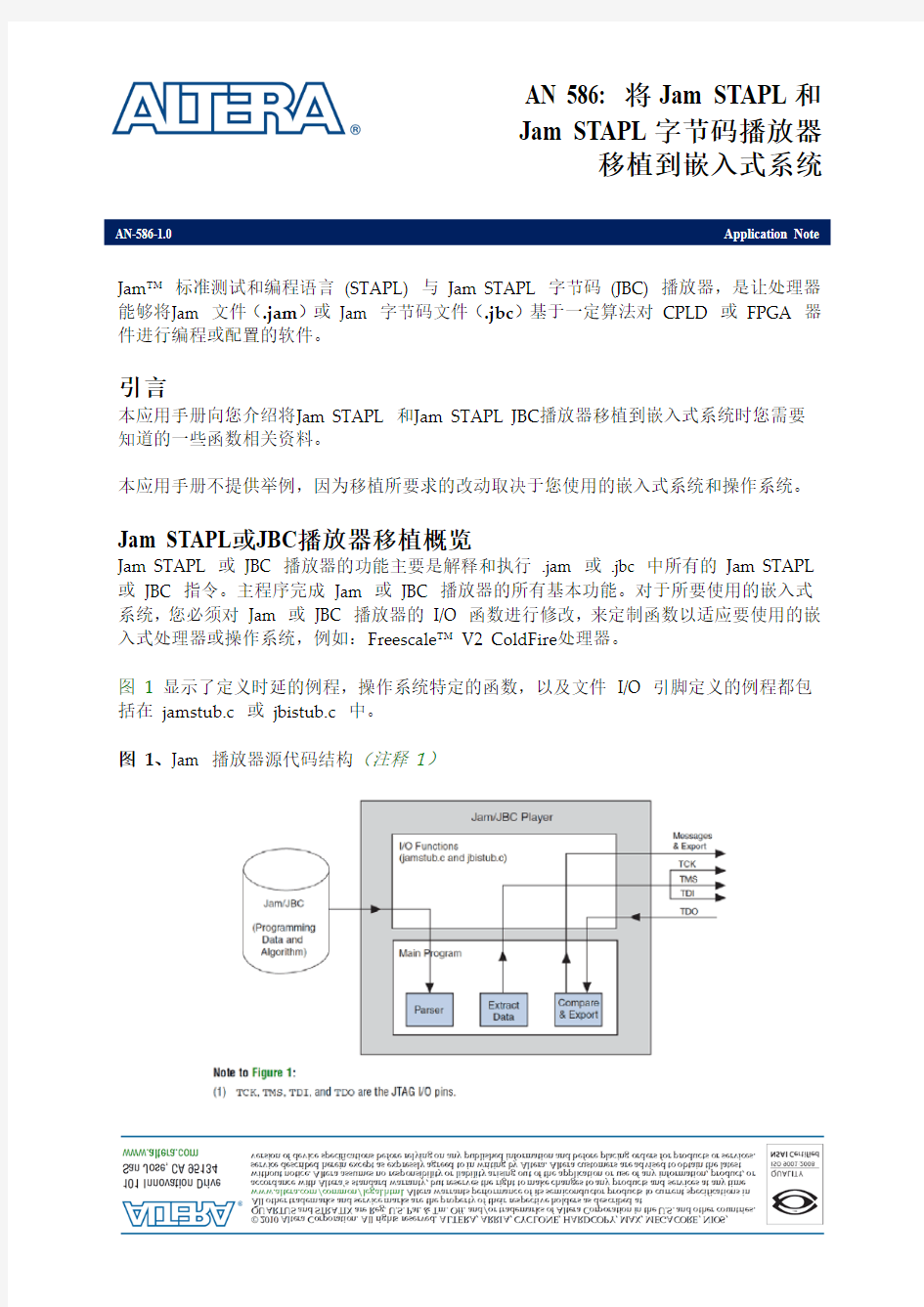

图1显示了定义时延的例程,操作系统特定的函数,以及文件I/O 引脚定义的例程都包括在jamstub.c 或jbistub.c 中。

图1、Jam 播放器源代码结构(注释1)

图1注释:

(1)TCK、TMS、TDI 和TDO 均为JTAG I/O 引脚。

通过编辑jamstub.c 或jbistub.c,您可以定制I/O 函数,为任何嵌入式系统编译源代码。Jam 或JBC 播放器是用C 编程语言来编写的。为了保证编译过程中的兼容性,Altera 推荐将Jam 或JBC 播放器移植到一个支持 C 语言兼容编译器的嵌入式系统。

Jam 或JBC 播放器源代码仅支持32 位处理器。您需要移植Jam 或JBC 播放器源代码以支持其它类型的处理器。

Altera 建议您只对jamstub.c 和jbistub.c 中的Jam 或JBC 播放器源代码进

行修改。

jamstub.c和jbistub.c中的函数

本小节列举出移植过程中需要注意的一些函数。表 1 显示了这些函数及其在jamstub.c和jbistub.c. 中的相应名称。表后面是每一种函数的简要介绍。

表1、jamstub.c 和jbistub.c 中的函数

主函数

main

该函数是每一个 C 程序的组成部分,也是所有 C 程序的主要构建模块。在Jam 或JBC 播放器源代码中,main() 函数包括.jam 或.jbc 位置、初始化列表和退出代码。另外,jam_execute 或jbi_execute 函数(Jam 或JBC 播放器的主入口点)是通过main() 函数调用的。

在默认情况下,初始化列表、操作和文件位置均设置为NULL。文件名和初始化列表均通过终端程序从输入流读取,终端程序利用命令提示符向Jam 或JBC 播放器发出指令。如果您的嵌入式处理器没有用户界面,则您必须自定义这个部分。初始化列表和操作的描述,请参见“初始化列表和操作”。

初始化列表和操作

下面各部分介绍了main() 函数的初始化列表和操作。

初始化列表

初始化列表init_list 是一系列指针字串所定义的地址,每个均包含一个初始化字符串。每个初始化字符串均以“string=值”的形式出现。一个初始化列表向Jam 或JBC 播放器提供要执行的初始化字符串,它们对应到指令。表2 列出了 1.1 版J am 规范定义的字符串。

表2、1.1 版Jam 规范定义的字符串

您必须以正确的方式传递初始化列表。如果传递的初始化列表无效或者没有传递初始化列表,则Jam 或JBC 播放器仅对.jam或.jbc 执行语法检查。如果语法检查通过,则Jam 或JBC 播放器发出成功退出代码,而不执行任何函数。例1表明了如何定义代码来建立

init_list,以使Jam 或JBC 播放器执行一个编程和验证操作。

例1、

操作规定了Jam 或JBC 播放器执行的动作。在默认情况下,将action 设置为NULL。如果不要求初始化列表,则您可以使用一个NULL 指针来表示一个空的初始化列表。这种情况仅适用于Jam 或JBC 播放器中已经定义了操作的情况。表3列出了Jam 或JBC 播放器中可用的一些操作。

表3、Jam 和JBC 播放器中的可用操作

延迟函数

jamstub.c 和jbistub.c 中有三种相互关联的延迟函数:delay()、calibrate_delay() 和get_tick_count()。get_tick_count() 函数获取系统时钟(system tick) 计数值,并将该值返回给calibrate_delay() 函数。之后,calibrate_delay() 函数利用该系统时钟计数来决定 1 毫秒延迟所需的循环。随后,delay() 函数利用该信息来执行WAIT 命令要求的延迟。get_tick_count

该函数由calibrate_delay() 函数调用,用以获取毫秒单位时间所需系统时钟计数。默认情况下,其源代码为下列操作系统定制:

?WINDOWS—GetTickCount() 函数

?UNIX—clock() 系统函数

如果您的嵌入式处理器的操作系统不使用上述Windows 或UNIX 函数,则您必须相应地定制这种函数。

calibrate_delay

该函数将确定1 毫秒延迟所需的循环次数。在默认情况下,源代码中是针对于Windows 操作系统的计算。

如果您嵌入式处理器的操作系统不是Windows,则您需要自定义这种函数。

该函数实现对PLD、内存编程以及配置基于SRAM 器件所需的编程脉宽控制。这些延迟是通过针对目标处理器速度校准软件循环来实现的。例如,对Altera MAX? CPLD 的内置EEPROM 单元进行编程中使用了不同的脉冲宽度。Jam 或JBC 播放器使用delay() 函数来实现这些脉宽。.jam 或.jbc 中的WAIT 命令指明了需要的延迟。

您必须根据处理器的速度以及处理器执行一个循环所需的时间来定制该函数。为了使执行Jam 或JBC STAPL的声明的时间最短,Altera 建议您在1 毫秒至1 秒的范围尽可能精确地校准延迟。

其它函数

getc

该函数会获取.jam 中的字符。对getc() 函数的每一次调用都将文件指针的当前位置前移。需要连续调用该函数来获得字符串。如果连续调用到达文件末尾,则设置文件末尾指示,同时getc() 函数返回EOF。如果出现读取错误,则设置错误指示,同时getc() 返回EOF。该函数同标准fgetc() C 函数类似。该函数返回读取的字符码,如果无读取值则返回一个(-1)。

在默认情况下,源代码考虑的是Windows 操作系统环境下.jam 中字符的检索算法。如果您处理器的操作系统使用一种不同的算法,则您需要定制该函数。

seek

该函数根据规定偏移值设置.jam 输入流的当前文件位置指针。如果该偏移值小于文件长度,则函数返回零,否则返回一个非零的值。该函数与标准 C 函数fseek() 类似。

在源代码中,.jam 的存储机制是内存缓冲区。另外,您可以使用一种文件系统作为存储机制。这种情况下,您必须自定义该函数,以使用与 C 语言fopen() 和fclose() 函数等效的函数,并存储文件指针。

jtag_io

该函数提供对IEEE 1149.1 JTAG 信号TDI、TMS、TCK 和TDO 的访问。jtag_io() 函数包含发送和接收二进制编程数据的代码。您必须将这四个JTAG信号重新映射至嵌入式处理器引脚。在默认情况下,在源代码中是写到PC的并行端口。

当前源代码中,PC 并口会反转TDO 实际值。jtag_io() 源代码中再次反转TDO 值来恢复原始数据。

tdo=(read_byteblaster(1)&0x80)? 0:1;

如果目标处理器不反转TDO,则代码为:

tdo=(read_byteblaster(1)&0x80)?1:0;

为了将信号映射到正确的地址,使用左移(<<)或者右移(>>)操作符。例如,如果TDI 和TMS 分别位于第三和第二端口,则代码为:

Data=(((tdi?0x40:0)>>3)|((tms?0x02:0)<<1));

将相同的过程运用于TCK 和TDO。

如果您不是使用PC 并口,则您必须自定义该函数来写入正确的硬件端口。

message

当Jam 或JBC 播放器在.jam 或.jbc 中遇到一个PRINT 命令时,播放器便处理该文本消息,并将结果传递给message() 函数。如果没有标准输出设备,message() 函数将不做任何操作。

播放器不会在文本消息末尾添加换行符。如果您的嵌入式系统要求您新添加一行,则您必须将message() 函数打印信息和该函数的错误信息修改为标准输出。如果您不使用该功能,则您可以删除该例程,或者在message() 函数中把puts() 函数的调用注释掉。

export_integer

export_integer() 和export_boolean_array() 函数将来自Jam 或JBC 播放器的信息返回给调用程序。该例程最常见的用法,是将器件的用户电子签名(UES) 指令代码传回调用Jam 或JBC 播放器的程序。该函数利用printf() 函数,向stdio 发送文本信息。Jam 或JBC 播放器使用export_integer() 和export_boolean_array() 函数来向调用Jam 或JBC 播放器的操作系统或软件传递信息(例如:器件的UES 指令代码或USERCODE)。

在默认情况下,Jam 或JBC 播放器使用printf 命令打印值。如果printf 命令不可用或者没有stdout 可用器件,则您需要修改这些函数。您可以将该信息重定向到某个文件或者存储设备,也可以将该信息作为一个变量传回给调用Jam 或JBC 播放器的程序。malloc

可以调用该函数以分配所需内存。在程序执行期间,Jam 或JBC 播放器必须分配内存来执行任务。当Jam 或JBC播放器分配内存时,malloc() 需被调用。例如,如果程序要将Jam 或JBC 文件写入内存时,Jam 或JBC 播放器将调用该函数来分配所需内存,以存

放.jam 或.jbc文件。Jam 或JBC 文件大小取决于被编程器件的数量以及类型。您必须评估各个设计,来选择一个合适的内存资源。

某些情况下,嵌入式系统不支持malloc() 函数。如果存在这种情况,则您必须使用一个同类函数来替代该函数。

如欲了解ROM 和RAM 内存使用估算方法的更多详情,请参见《AN 425:使用命令行Jam STAPL 解决方案进行器件编程》的“Jam STAPL字节码播放器内存使用”小节。initialize_jtag_hardware

该函数对您的硬件I/O 进行初始化,以使播放器能够写至JTAG 端口。默认情况下,Jam 或JBC 播放器源代码包含Windows 操作系统初始化硬件I/O 的例程。

您必须根据您的操作系统和硬件要求自定义该函数来初始化您的硬件I/O。

close_jtag_hardware

该函数关闭(或失效)您的硬件I/O,以使播放器停止写至JTAG 端口。在默认情况下,Jam 或JBC 播放器源代码包含关闭Windows 操作系统通信端口的例程。

其它操作系统环境下,您必须自定义该函数来关闭您的硬件I/O。

read_byteblaster

该函数通过ByteBlaster? II 下载线缆读取数据。read_byteblaster 函数使用conio.h 库的inp() 函数从并行端口进行读取操作。该函数仅针对Windows 系统而定制。

在您的嵌入式处理器中,您必须使用同类函数定制该函数,通过ByteBlaster II下载线缆来执行读取操作。

write_byteblaster

该函数通过ByteBlaster II 下载线缆写入数据。write_byteblaster 使用conio.h 库的outp() 函数来写入并行端口。该函数仅针对Windows 操作系统而定制。

在您的嵌入式处理器中,您必须使用同类函数来定制该函数,通过ByteBlaster II 下载线缆来执行写入操作

文档修订记录

表 4 列出了本应用手册的修订记录。

表4、修订记录

最全的刷bios方法

刷新主板BIOS的几种方法BIOS(Basic Input-Output System)即电脑的基本输入输出系统,是集成在主板上的一个ROM芯片,它提供了电脑系统最基础的功能支持。其中包含了开机引导代码、基础硬件驱动程序、参数设置程序以及一些厂商自主研发的软件等。BIOS的一大特点就是可以用特定的方法来刷新,这就是通常所说的BIOS升级。升级BIOS除了可以获得许多新的功能之外,还可以解决芯片组、主板设计上的一些缺陷,排除一些特殊的电脑故障等。提到刷新BIOS,很多人一定认为做这种事很危险,弄不好就会把BIOS刷坏。其实,如果你掌握了正确的方法,并且操作得当,一般是没有什么问题的。刷新BIOS的方法有很多种,除了可以在DOS下刷新外,还可以在Windows下刷新,另外还有一些主板厂商在其主板中设计了BIOS刷新工具,开机后按相应的组合键就可以调出BIOS刷新工具进行刷新。下面就让我来给大家一一介绍一下。 现在国内市面上比较流行的主板BIOS主要有Award BIOS和AMI BIOS这两种,不同类型的BIOS所使用的刷新程序也不相同。我们可以通过开机自检画面判断,或者开机时按“Del”键进入CMOS后,在其设置界面上判断。以下均以Award BIOS为例: 1.在DOS下刷新 1)先将主板的最新BIOS文件(如:Awardbios.bin文件)和刷新工具awdflash.exe下载 至你的硬盘上的一个文件夹中,如D:\BIOS文件夹。 2)制作一张Windows 98启动盘,在BIOS中设成从软驱启动,用这张启动盘引导系统进入 DOS实模式状态。 注意:在Windows 98下制作启动盘时,要选择“仅复制系统文件”这项。制作好的启动盘里面只含有“Io.sys、Msdos.sys、Command.com”这三个文件。 另外,如果你的系统是Windows 98,也可以在系统启动时迅速按下F8键,在出现的启动选择菜单里选择第6项“Safe Mode Command Prompt Only”,也可以进入到DOS实模式下。 3)输入CD D:\BIOS,进入到D:\BIOS目录。再输入awdflash.exe,进入到刷新软件的界 面。 4)在“File Name to Program”后面输入你下载的新版本BIOS名Awardbios.bin。 5)回车后,刷新软件会问你“Do you want to save BIOS(Y/N)”,为了保险起见我们一 般按“Y”键选择备份原有的BIOS文件。按提示在“File Name to Save”后面输入要保存的BIOS文件名(如oldbios.bin)后回车,此时刷新程序开始备份你的BIOS文件。 6)备份工作完成后,刷新程序会再次提示你“Are you sure to program(Y/N)”,其意思为 你确认更新BIOS吗?此进按“Y”,刷新程序就把最新的BIOS文件写入到BIOS里了。 BIOS刷新完成后,会出现两个提示信息:一是按F1进行重新启动,二是按F10退出返回DOS,你可以根据你的实际情况来选择。如果你认为你的刷新操作是完全正确的,你就可以按F1键重新启动电脑;如果你认为刷新过程中存在一些错误或不当,就按F10退出,重新刷新。 2.在Windows下刷新 随着Windows使用者的增多,人们越来越习惯在图形化的界面下操作,毕竟现在用DOS

USB+AVR+JTAGICE使用说明书

USB AVR USB AVR JTAG JTAG JTAGICE ICE ICE 使用说明 使用说明 版本:R R e v 1.0 2020008-1

简介 一、简介 USB AVR JTAGICE支持自动升级和手动升级的仿真器,与AVR Studio相结合,通过 USB可以对所有带JTAG 接口的单片机进行在片调试和编程。 【主要功能简介】 · 基于ATMEL原厂提供的方案而设计,支持AVRStudio,借鉴了ATMEL原厂生产的 JTAGICE仿真器,使用方法同它们一致,简单易用,稳定可靠。手动升级采用AVR910对监控芯片升级,彻底解决冲掉监控代码的后顾之忧! · 接入目标板的JTAG接口,可使用JTAG方式进行连接。 · JTAG功能: - JTAG仿真及编程支持的器件型号:与ATMEL原装JTAGICE仿真器支持的器件型号相同。 - JTAG仿真功能与性能:与ATMEL原装JTAGICE仿真器仿真功能相同。支持全速运行、单步调试、断点调试等各种调试方法,可查看IO状态,变量数据等,仿真速度可设置提高至115200bps等等。 - JTAG编程功能与性能:与ATMEL原装JTAGICE仿真器烧写功能相同。可直接烧写程序,设置熔丝位等。 · 与PC机的连接接口: - 准USB接口(USB To RS232,需要安装驱动程序!); · 与目标板的连接接口: - 与ATMEL官方JTAG标准接口兼容; · 特点: - 监控固件程序可升级!JTAG采用单独的MCU进行控制,控制程序均采用ATMEL提供的固件程序,使得该仿真器可自动检测AVRStudio的新版本。日后,ATMEL将会推出更多AVR型号,亦会将新的器件型号添加入AVRStudio的器件支持列表,当您在未来开发中需要使用最新的型号,升级AVRStudio,升级仿真器的固件程序,仿真器便得以支持新的型号!

液晶显示屏V-by-One与LVDS接口信号驱动原理

V-by-One接口信号驱动原理(3840*2160) 一、时钟与像素点关系 一场:60Hz-16.667ms,2250行(2160行有效) ——刷新像素点:3840*2160个/Vertical 一行:135KHz-7.407us,(=60Hz*2250),4400=550*8点(3840点=480*8点有效)——刷新像素点:3840个/ Horizontal Clock:74.25MHz-13.468ns,(=135KHz*550) ——刷新像素点:8个/Clock 以上,可参考《附录A:屏规格书信号时序特性》。 二、V-by-One信号传输规则 每个Clock(DCLK),V-by-O接口有8对差分对(lane0~lane7)同时传输,每对差分对负责一个Pixel;共8个Pixels一起传输数据。 以上,可参考《附录B:屏规格书每场画面时序》与《附录C:屏规格书单区与双区的驱动方式(每一行)》。 每对差分对同时串行传输4Bytes字节(共32bits,V-by-One传输协议有40bits);(每bit周期0.3367ns=13.468ns/40,2,97G带宽) 或按照公式计算:4(byte)×8×(10/8)×(594MHz/8lines)=2,97G 以上,可参考《附录D:屏规格书数据传输格式》与《附录E:V-by-O协议文件截图》。 信号最小单位为bit,1bit的数据长度合成眼图(1UI=0.3367ns=336.7ps),可通过眼图测试得具体信号特性; 以上,可参考《附录F:V-by-O接口输入端眼图》。

附录C:屏规格书单区与双区的驱动方式(每一行)

JTAG接口的定义及常见问题

JTAG接口的定义及常见问题 ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM 系统前要先熟悉ARM系统的JTAG接口的定义和常见问题。 1.ARM系统的JTAG接口是如何定义的?每个PIN又是如何连接的? 下图是JTAG接口的信号排列示意: 接口是一个20脚的IDC插座。下表给出了具体的信号说明: 表 1 JTAG引脚说明 序号信号名方向说明 1 Vref Input 接口电平参考电压,通常可直接接电源 2 Vsupply Input 电源 (设备提供) 3 nTRST Output (可选项) JTAG复位。在目标端应加适当的上拉电阻以防止误触发。 4 GND -- 接地 5 TDI Output Test Data In from Dragon-ICE to target. 6 GND -- 接地 7 TMS Output Test Mode Select 8 GND -- 接地 9 TCK Output Test Clock output from Dragon-ICE to the target 10 GND -- 接地 11 RTCK Input (可选项) Return Test Clock。由目标端反馈给Dragon-ICE的时钟信号,用来同步TCK信号的产生。不使用时可以直接接地。12 GND -- 接地

13 TDO Input Test Data Out from target to Dragon-ICE. 14 GND -- 接地 15 nSRST Input/Output (可选项) System Reset,与目标板上的系统复位信号相连。可以直接对目标系统复位,同时可以检测目标系统的复位情况。为了防止误触发,应在目标端加上适当的上拉电阻。 16 GND -- 接地 17 NC -- 保留 18 GND -- 接地 19 NC -- 保留 20 GND -- 接地 2.目标系统如何设计? 目标板使用与Dragon-ICE一样的20脚针座,信号排列见表1。RTCK和 nTRST 这两个信号根据目标ASIC有否提供对应的引脚来选用。nSRST则根据目标系统的设计考虑来选择使用。下面是一个典型的连接关系图: 复位电路中可以根据不同的需要包含上电复位、手动复位等等功能。如果用户希望系统复位信号nSRST能同时触发JTAG口的复位信号nTRST,则可以使用一些简单的组合逻辑电路来达到要求。后面给出了一种电路方案的效果图。

刷bios图解教程

刷bios图解教程 AWARD Plug-and-Play BIOS升级方法 如果是SOLTEK公司的用户,在主板出货光碟上就有写BIOS的程序----Awdflash.exe,其在光碟上的路径为:UtilityAwdflash.exe(或者可以在我们公司网站程序下载中下载最新版本),AWARD BIOS程序都是以“.bin”为扩展名的文件,SOLTEK公司在公司主页上随时为您提供各款主板最新BIOS 程序,直接下载就可以了。具体BIOS刷新操作方法如下: 1、刷新BIOS前需要先准备一张DOS启动软盘,制作方法有以下几种: (a). 可以使用Win98系统格式化一张系统磁盘,在WIN98中点击我的电脑,在3.5软盘上点击鼠标右键,选择格式化,然后选择仅复制系统文件并格式化即可。 (b). 可以在MS-DOS模式下,在DOS提示符下键入format a:/s格式化一张DOS启动软盘。 2、 DOS启动盘制作完成后您可以将BIOS刷新程序Awdflash.exe,BIOS文件*.bin同时复制到刚刚制作的软盘当中(注意要在同一目录)。然后用该软盘启动DOS,如果是用WIN98/ME的启动盘来升级BIOS,注意当屏幕出现Starting Windows 98......时,按下Shift+F5组合键跳过Config.sys文件的执行。因为在升级BIOS时不能有内存管理程序的执行 C 启动到DOS后进行BIOS刷新,在DOS提示符下执行 A:>Awdflash *.bin /cc/cd/cp/sn/py确定后就会自动完成BIOS的刷新操作并重新启动。*.bin 为BIOS文件名,需要输入您下载的新版本的BIOS文件名,而且要带.bin的后缀才可以。如果需要备份旧版本的BIOS,可以按以下步骤进行: 键入A:>Awdflash **.bin /cc/cp/cd之后,(请注意BIOS文件名与参数之间需留有一空格)片刻将会出现图一的界面。见下图: 图一

LVDS屏线及屏接口定义

LVDS屏线及屏接口定义 现在碰到液晶屏大多是LVDS屏线,经常碰到什么单6,双6 单8双8.如何区分呢? 方法数带“+-”的这种信号 线一共有几对,有10对的减2对就是双8,有8对的减2对就是双6。有5对的 减掉1对是单8,有4对的减掉1对是单6,数+/-线一共有多少对。说通俗点就 4对——单6 5对——单8 8对——双6 10对——双8 方法2 拧开螺丝看看主板里面的电路,一般每对数据线之间都有一个100欧姆的电阻 ,看到4个的话就是单6位的屏,看到8个的话就是双六位,5个的话一般是单8位,有10个一般就是双8位,当然有资料的话就不用这么麻烦,也有TMDS 也用这种20PIN的连接头的,比如LG的LP141X1,不过基本上很少lvds的接口的定义20PIN单6定义: 1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地 14:CLK- 15:CLK+ 16空 17空 18空 19 空 20空每组信号线之间电阻为(数字表120欧左右) 20PIN双6定义 1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:R1- 8:R1+ 9:R2- 10:R2+ 11:CLK- 12:CLK+ 13:RO1- 14:RO1+ 15:RO2- 16:RO2+ 17:RO3- 18:RO3+;19:CLK1- 20:CLK1+每组信号线之间电阻为(数字表120欧左右) X20PIN单8定义: 1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地 14:CLK- 15:CLK+ 16:R3- 17:R3+ 每组信号线之间电阻为(数字表120欧左右) 30PIN单6定义: 1:空2:电源3:电源 4:空 5:空 6:空 7:空 8:R0- 9:R0+ 10:地 11:R1- 12:R1+ 13:地 14:R2- 15:R2+ 16:地 17:CLK- 18:CLK+ 19:地 20:空- 21:空 22:空 23:空 24:空 25:空 26:空 27:空 28空 29空 30空每组信号线之间电阻为(数字表120欧左右)' 30PIN单8定义: 1:空2:电源3:电源 4:空 5:空 6:空 7:空 8:R0- 9:R0+ 10:地 11:R1- 12:R1+ 13:地 14:R2- 15:R2+ 16:地 17:CLK- 18:CLK+ 19:地 20:

Jtag的各种引脚定义

Jtag的各种引脚定义 使用过ARM芯片的人肯定都听过一个仿真器————JLINK,为什么ARM芯片现在能够这么流行?其中恐怕就有一个原因就是很多的ARM芯片都支持使用Jlink进行调试和仿真。所以你只要有一个Jlink,不管是ARM7、ARM9、ARM11还是最新的ARM Cortex 系统都能下载和调试了。 以前的嵌入式开发者,可能使用什么公司的芯片就得买一个对应芯片的下载和仿真器,这样如果你只使用一种芯片,可能还好,不过恐怕没有那种芯片能够一直引领市场。 Jlink使用的是一种叫做JTAG的协议,JTAG原本是用于芯片内部测试的,现在大多用于芯片的程序下载和调试仿真。由于现在Jlink用的比较多,所以有些人可能把Jlink就等同于JTAG了,实际上,JTAG是一种协议,只要满足这种协议的就可以叫做JTAG,比如H—JTAG、OpenJTAG、OSJTAG等等。正版的Jlink是卖的很贵的。大概是1000到2000RMB吧。不过,中国的山寨能力是很强的,而且你硬件卖给别人了,你也没办法控制别人说你不许拆开我的东西看里面的电路是怎么样的。所以Jlink就被破解了,破解之后的Jlink很便宜,网上五六十块钱就能买到一个能用的Jlink。 除了商业版的Jlink和H—JTAG,网上还有一些电子爱好者,他们参照开源软件的模式,设计了开源硬件,比如arduino。还有人制作了开源版本的JTAG仿真器——OpenJTAG。而一些芯片的开发商不像那些软件厂商,会给软件做很多的限制,他们对于开源硬件还是比较开明的,所以他们也支持了一些开源硬件。比如TI公司的MSP430 LaunchPad、ST公司的STM Discovery 等等板子。还有飞思卡尔公司的USBDM和OSJTAG。他们把这些硬件的原理图、PCB还有固件都放在了网络上供人自由下载和制作,你也可以根据他的资料进行改进。这样能使大家对于他们家的芯片有更多的了解,所以,他们也乐于开源一些评估板。 今天我要说的是几种JTAG仿真器的引脚定义,首先我看看比较常见的JTAG 20-Pin的引脚接口如下:

最新整理NVIDIA显卡刷BIOS教程方法介绍

N V I D I A显卡刷B I O S教程方法介绍 有时利用显卡刷B I O S有可能能优化系统性能等,那么,N V I D I A显卡刷B I O S具体步骤是怎样的呢?可能有许多用户不懂,具体方法见下文N V I D I A显卡刷B I O S教程。 下文以N V I D I A显卡为例,需要应用到N V F f a s h软件(可在N卡官网上下载)。 N V I D I A显卡刷B I O S教程: 1、将下载下来的N V F f a s h.e x e和B I O S文件放在C 盘新建的N V F f a s h文件夹中,进入D O S界面后先进入到C盘分区: 输入:C:回车 进入B I O S文件夹,输入:c d B I O S回车 然后要刷新显卡B I O S,输入:n v f l a s h-4-5-6 50754789b c a d0.r o m回车(50754789b c a d0.r o m为R O M名字,也可以在之前就将其改名为非常简单的名字,如1.r o m)注意,50754789b c a d0.r o m为下载下来的B I O S文件名字。 2、刷新过程中会有一步让您确认是否刷新,在这一步可以看到显示芯片之类的相关数据,按:Y继续刷新

B I O S。 3、B I O S在刷新过程之中。 4、刷新成功。 最后,刷新成功后需要重启。电脑会自动进入系统,此时说明显卡B I O S刷新成功。 相关阅读:B I O S故障分析大全 1.C M O S b a t t e r y f a i l e d 中文:C M O S电池失效。 解释:这说明C M O S电池已经快没电了,只要更换新的电池即可。 2.C M O S c h e c k s u m e r r o r-D e f a u l t s l o a d e d 中文:C M O S执行全部检查时发现错误,要载入系统预设值。 解释:一般来说出现这句话都是说电池快没电了,可以先换个电池试试,如果问题还是没有解决,那么说明C M O S R A M可能有问题,如果没过一年就到经销商处 换一块主板,过了一年就让经销商送回生产厂家修一下吧! 3.P r e s s E S C t o s k i p m e m o r y t e s t 中文:正在进行内存检查,可按E S C键跳过。

U盘版 AVR JTAG ICE 使用说明

U盘版AVR-JTAG-ICE 仿真器 安装与使用说明(V1.0版) 目录 一、产品介绍 (3) 二、安装驱动 (4)

三、硬件连接 (5) 四、安装软件 (7) 五、升级固件 (8) 六、在线编程 (12) 七、在线仿真 (14) 八、疑难解答 (16) 九、断开对外5V供电(3.3V供电系统) (16) 一、产品介绍

迷你型USB AVR JTAG ICE仿真器是一款针对AVR系列具有JTAG接口的单片机进行在线编程下载、仿真调试开发的优秀首选工具,仿真器内部固件可无限升级,故可适应AVRstudio 各种版本软件。其外形小巧,价格低廉,是工厂、学校、个人等开发AVR系列单片机的首选产品。 特点: 1.支持USB1.1或USB 2.0通信; 2.全面支持WIN98、WINME、WIN2000、WINXP、VISTA、WIN7等32位与64位操作系统; 3.采用USB口供电,板内带有500mA自恢复保险丝,保护电脑主板不被意外烧毁; 4.在对芯片编程仿真时可以使用目标系统本身电源,也可以使用仿真器从USB口取电 供给目标板,但应保证目标标电流不大于500mA,以免过流保护不能正常工作; 5.支持AVR系列单片机具有JTAG接口的所有型号芯片; 6.编程完成不影响目标板的程序运行,可以对Flash、EEPROM、熔丝位等读写操作; 7.支持3.3V与5V工作电压系统; 8.固件可无限升级,支持多个版本的AVR studio环境; 9.使用Atmel公司推荐的标准10PIN JTAG接口; 10.使用铝合金外壳设计,提供多色可选,小巧时尚携带方便。 二、安装驱动

JTAG各类接口针脚定义及含义

JTAG各类接口针脚定义及含义 JTAG有10pin的、14pin的和20pin的,尽管引脚数和引脚的排列顺序不同,但是其中有一些引脚是一样的,各个引脚的定义如下。 一、引脚定义 Test Clock Input (TCK) -----强制要求1 TCK在IEEE1149.1标准里是强制要求的。TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。 Test Mode Selection Input (TMS) -----强制要求2 TMS信号在TCK的上升沿有效。TMS在IEEE1149.1标准里是强制要求的。TMS信号用来控制TAP状态机的转换。通过TMS信号,可以控制TAP在不同的状态间相互转换。 Test Data Input (TDI) -----强制要求3 TDI在IEEE1149.1标准里是强制要求的。TDI是数据输入的接口。所有要输入到特定寄存器的数据都是通过TDI接口一位一位串行输入的(由TCK驱动)。 Test Data Output (TDO) -----强制要求4 TDO在IEEE1149.1标准里是强制要求的。TDO是数据输出的接口。所有要从特定的寄存器中输出的数据都是通过TDO接口一位一位串行输出的(由TCK驱动)。 Test Reset Input (TRST) ----可选项1 这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。TRST可以用来对TAPController进行复位(初始化)。因为通过TMS也可以对TAP Controll进行复位(初始化)。所以有四线JTAG与五线JTAG之分。 (VTREF) -----强制要求5 接口信号电平参考电压一般直接连接Vsupply。这个可以用来确定ARM的JTAG接口使用的逻辑电平(比如3.3V还是5.0V?) Return Test Clock ( RTCK) ----可选项2 可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK信号的产生,不使用时直接接地。System Reset ( nSRST)----可选项3 可选项,与目标板上的系统复位信号相连,可以直接对目标系统复位。同时可以检测目标系统的复位情况,为了防止误触发应在目标端加上适当的上拉电阻。 USER IN 用户自定义输入。可以接到一个IO上,用来接受上位机的控制。 USER OUT 用户自定义输出。可以接到一个IO上,用来向上位机的反馈一个状态 由于JTAG经常使用排线连接,为了增强抗干扰能力,在每条信号线间加上地线就出现了这种20针的接口。但事实上,RTCK、USER IN、USER OUT一般都不使用,于是还有一种14针的接口。对于实际开发应用来说,由于实验室电源稳定,电磁环境较好,干扰不大。

串口JTAG使用说明

AVR JTAG下载HEX文件使用说明 本文只介绍AVR JTAG下载HEX文件在AVR Studio环境下的下载方法,推荐使用。并口下载线主要优点是电路简单,缺点主要有下载速度慢、不能在AVR Studio环境下使用。具体差别在用了AVR JTAG 之后就知道了,现在一个标准的下载线也只要几十块钱和并口下载线没什么差别了。此处所说的STK500下载线和AVR ISP下载线同属一类,它们使用相同的通信协议,STK500确切的说是一个学习板,AVR JTAG才是真正意义上的下载线。 AVR JTAG实物图片 AVR JTAG连接示意图 JTAG接口 支持芯片列表

AVR JTAG下载线支持芯片型号非常多,这里就不一一列出了,只要AVR芯片支持ISP下载的都可以。AVR JTAG下载HEX文件-操作方法: 1、打开AVR Studio 软件,按下图操作。 2、在这里选择所用器件及连接端口,选择JTAG ICE,自动检测端口,点击Connect进入下一步。 3、下面窗口提示所用AVR ISP下载线固件版本与当前所用软件不同,提示要求升级AVR ISP下载线固件,如版本相同就不会出现下面的提示。如你所用的AVR ISP下载线不支持在线升级功能的话,不要点确定要不AVR ISP下载线会死在那里不动了,直接点击取消跳过此步既可。 4、正常会进入下面编程(Program)界面。主要包括有器件(Device)、编程模式(Programming mode)、Flash下载、EEPROM下载几个部分,最下面部分是信息窗口。

器件:用于选择器件和手工擦除器件。 编程模式:用于选择ISP和并口下载模式,由于此处用的是AVR JTAG下载线只支持ISP方式下载。Erase Device Before擦除器件,选中此项在每次下载前会对将器件擦除。需要同时烧写用户程序和引导程序时需要注意此处,正常情况下需选中此项。Verify Devic写入校验,默认为选中。 Flash:下载Flash文件,有选择文件(Input HEX File)、编程(Program)、校验(Verify)、读取(Read)。 EEPROM:下载EEPROM文件,包含内容与上面相同。 如果你是初学者,并不要求对器件进行熔丝等复杂配置,由此窗口将HEX文件写入器件就可以实验了。其它系统时钟及看门狗等可先使用器件默认配置。 5、下图为熔丝配置(Fuses)界面,具体配置请参照熔丝配置部分。

lvds接口定义及原理知识

lvds接口定义及原理知识 LVDS接口定义 作者:bechade 更新时间:2007-9-22 7:31:10 文章录入:chfygl -------------------------------------------------------------------------------- 20PIN单6定义: 1:电源2:电源3:地4:地5:R0- 6:R0+ 7:地8:R1- 9:R1+ 10:地11:R2- 12:R2+ 13:地14:CLK- 15:CLK+ 16空17空18空19 空20空 每组信号线之间电阻为(数字表120欧左右) 20PIN双6定义: 1:电源2:电源3:地4:地5:R0- 6:R0+ 7:R1- 8:R1+ 9:R2- 10:R2+ 11:CLK- 12:CLK+ 13:RO1- 14:RO1+ 15:RO2- 16:RO2+ 17:RO3- 18:RO3+ 19:CLK1- 20:CLK1+ 每组信号线之间电阻为(数字表120欧左右) 20PIN单8定义:

1:电源2:电源3:地4:地5:R0- 6:R0+ 7:地8:R1- 9:R1+ 10:地11:R2- 12:R2+ 13:地14:CLK- 15:CLK+ 16:R3- 17:R3+ 每组信号线之间电阻为(数字表120欧左右) 30PIN单6定义: 1:空2:电源3:电源4:空5:空6:空7:空8:R0- 9:R0+ 10:地11:R1- 12:R1+ 13:地14:R2- 15:R2+ 16:地17:CLK- 18:CLK+ 19:地20:空- 21:空22:空23:空24:空25:空26:空27:空28空29空30空 每组信号线之间电阻为(数字表120欧左右) 30PIN单8定义: 1:空2:电源3:电源4:空5:空6:空7:空8:R0- 9:R0+ 10:地11:R1- 12:R1+ 13:地14:R2- 15:R2+ 16:地17:CLK- 18:CLK+ 19:地20:R3- 21:R3+ 22:地23:空24:空25:空26:空27:空28空29空30空 每组信号线之间电阻为(数字表120欧左右) 30PIN双6定义: 1:电源2:电源3:地4:地5:R0- 6:R0+ 7:地8:R1- 9:R1+ 10:地11:R2- 12:R2+ 13:地14:CLK- 15:CLK+ 16:

JTAG接口电路

JTAG接口电路 1 JTAG(Joint Test Action Group;联合测试行动小组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。 JTAG最初是用来对芯片进行测试的,JTAG的基本原理是在器件内部定义一个TAP(Test Access Port;测试访问口)通过专用的JTAG测试工具对进行内部节点进行测试。JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。现在,JTAG接口还常用于实现ISP(In-System Programmable�在线编程),对FLASH等器件进行编程。 JTAG编程方式是在线编程,传统生产流程中先对芯片进行预编程现再装到板上因此而改变,简化的流程为先固定器件到电路板上,再用JTAG编程,从而大大加快工程进度。JTAG接口可对PSD芯片内部的所有部件进行编程 具有JTAG口的芯片都有如下JTAG引脚定义: TCK——测试时钟输入; TDI——测试数据输入,数据通过TDI输入JTAG口; TDO——测试数据输出,数据通过TDO从JTAG口输出; TMS——测试模式选择,TMS用来设臵JTAG口处于某种特定的测试模式。 可选引脚TRST——测试复位,输入引脚,低电平有效。 含有JTAG口的芯片种类较多,如CPU、DSP、CPLD等。 JTAG内部有一个状态机,称为TAP控制器。TAP控制器的状态机通过TCK和TMS进行状态的改变,实现数据和指令的输入。图1为TAP控制器的状态机框图。 2 JTAG芯片的边界扫描寄存器 JTAG标准定义了一个串行的移位寄存器。寄存器的每一个单元分配给IC芯片的相应引脚,每一个独立的单元称为BSC(Boundary-Scan Cell)边界扫描单元。这个串联的BSC在IC内部构成JTAG回路,所有的BSR (Boundary-Scan Register)边界扫描寄存器通过JTAG测试激活,平时这些引脚保持正常的IC功能。图2为具有JTAG口的IC内部BSR单元与引脚的关系。 3 JTAG在线写Flash的硬件电路设计和与PC的连接方式 以含JTAG接口的StrongARM SA1110为例,Flash为Intel 28F128J32 16MB容量。SA1110的JTAG的TCK、TDI、TMS、TDO分别接PC并口的2、3、4、11线上,通过程序将对JTAG口的控制指令和目标代码从PC的并口写入JTAG的BSR中。在设计PCB时,必须将SA1110的数据线和地址线及控制线与Flash的地线线、数据线和控制线相连。因SA1110的数据线、地址线及

JTAGICE MKII使用方法-AVR

JTAGICE MKII仿真器使用方法 一:硬件和软件的准备 1. 仿真器上需要接一个ISP-10PIN的转换线(实物已经接好); 2.不能将WDAM的JP1那一行VCC和GND的管脚拆下,仿真器不能提供电源,但是需要接上VCC和GND; 3. WDAM需要外部供电; 4.需要将与RESET管脚连接的容性器件拆下,即将R39的电容拆下; 5.安装AVR studio4(仿真器也可与AVR studio5或者AVR studio6一起使用,但我是用AVR studio4测试的,所以建议使用AVR studio4) 二、烧写程序 1.打开AVR studio4,选择Tools-Program-connect,弹出如下对话框,依次选择 2.选择完后,弹出另一对话框,依次按如下选择,即可完成程序下载

三、仿真 1、打开AVR studio4,选择project-projectWizard,弹出如下对话框,点击OPEN,选择我们用ICCAVR编写的程序的工程文件里的.COF文件

2.上面那步操作完后会弹出如下对话框,按图依次选择 3.如果MCU没有使能DWEN熔丝位,会弹出如下对话框,选择”Use SPI to enable debugWIRE interface”,点击OK后,会弹出一个对话框,提示需要重启设备,此时我们重新启动WDAM后,点击确定,即可进入仿真界面

三、取消DWEN的使能 1、打开AVR studio4,选择project-projectWizard,弹出如下对话框,点击OPEN,随意选择我们用ICCAVR编写的程序的工程文件里的.COF文件

LVDS接口定义

LVDS接口又称RS-644总线接口,是20世纪90年代才出现的一种数据传输和接口技术。LVDS即低电压差分信号,这种技术的核心是采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点,其传输介质可以是铜质的PCB连线,也可以是平衡电缆。LVDS在对信号完整性、低抖动及共模特性要求较高的系统中得到了越来越广泛的应用。目前,流行的LVDS技术规范有两个标准:一个是TIA/EIA(电讯工业联盟/电子工业联盟)的ANSI/TIA/EIA-644标准,另一个是IEEE 1596.3标准。 如上图,就是一块单六位LVDS 30针接口的液晶屏,其中1脚GND就是地,2脚、3脚VCC就是电压,4、6、7脚为存储IC(一般为24C之类的芯片)的读写信号脚,就是我们常换DELL机器的屏所说的码片,这里面存储了屏的一些信息,如型号、生产日期等,DELL 之类的少类的机器就往屏上这个IC里写入了自家的识别信号。8脚R0-、9脚R0+为第一组LVDS信号,依次类推,每往下一组信号中间都空一脚,共三组R-及R+信号,一直到接口的17脚CLKIN-、18脚CLKIN+,这两脚很重要,断开一根线,屏就无法显示,R-+的信号,少了一根两根还可以点亮屏,当然会显示不正常!这四对信号用数字表量阻值表现为100欧--120欧(不同屏)。

像我以前装液晶显示器的时候,这个单六位LVDS,只要对应单六位,再对应屏的分辨率(分辨率很重要)写个程序,屏线只用十根线,几乎就可以点亮这类的屏!这类屏我们常称为单六,当然液晶显示器的屏还有单八,单八的就多了对R3-和R3+,别小看这多出的一对信号,液晶屏的色彩就会多很多~单八位的己经过时了,以前15寸的液晶显示器的屏很多都是单八位的。当然,还有双八的~现在的市面上的液晶显示器都是双八位的接口啦~ 这里,我可以大胆的说:笔记本上用的都是单六,和双六的~现在液晶显示器上用的都是双八位了,早期的还有TTL、TMDS、TCON接口的,这类接口的我们修本的完全不必了解。扯远了。。。当然,你别和我说:我狗年马日拆的一台液晶显示器里怎么就是单六的……这个就是中国的山寨文化了,你们都懂的……. 真正用于笔记本上的屏全部都是单六的,高档机有双六的,双六接口的就是我们所说的高分屏了。 以前如果超过了1280X800的分辨率的屏就一定是双六或双八的,当然现在出的LED的屏也是这样的,只不过单六的分辨率到了1366X768,略高一点点而己!LED的屏,屏信号也是LVDS的,说的LED只不过是背光源是LED发光的而己~ 双六接口的高分辨率的屏,多了四对信号: RS0-、RS0+,RS1-、RS1+,RS2-、RS2+,CLK2-、CLK2+。(有的屏的PDF档里为RB0-、RB0+之类的,其实都一样): 如果我们接双六屏线的时候,这四对信号不能接到R0-至CLK1+上面去,否则……你们懂的~ 早期的20针的笔记本屏的定义如下,懒得找图了,直接在百度找个定义说明,略加修改,你们自己研究下吧: 20PIN单6定义: 1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地 14:CLK- 15:CLK+ 16空17空18空19 空20空; 每组信号线之间电阻为(数字表100~120欧左右) 20PIN双6定义: 1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:R1- 8:R1+ 9:R2- 10:R2+ 11:CLK- 12:CLK+ 13:RO1- 14:RO1+ 15:RO2- 16:RO2+ 17:RO3- 18:RO3+ 19:CLK1- 20:CLK1+6;

最新整理映泰890主板怎么刷新BIOS

映泰890主板怎么刷新B I O S 映泰890主板,相信有些人用过或者正在用,那么对于B I O S,应该怎么刷新呢?那就告诉大家一些F12一键刷映泰主板B I O S的实践经验。 方法步骤: 之后重新启动计算机,系统自检过程猛按F12键,即可进入如下界面,选择U S B移动设备,回车进入。 进入刷新程序界面,左边f i l e栏显示U盘当中存放的B I O S文件,选择,点击回车。 刷新界面出现确认信息,确认无误后Y,点击回车。 再次显示确认信息,同样,Y回车确认即可。 经过两侧信息确认后,刷新过程正式开始 待进度条读完后,刷新完成,再次弹出确认信息,Y 回车后电脑重新启动 重新启动后,被替换掉的开机画面显示正常。 相关阅读:B I O S故障分析大全 1.C M O S b a t t e r y f a i l e d 中文:C M O S电池失效。 解释:这说明C M O S电池已经快没电了,只要更换新的电池即可。

2.C M O S c h e c k s u m e r r o r-D e f a u l t s l o a d e d 中文:C M O S执行全部检查时发现错误,要载入系统预设值。 解释:一般来说出现这句话都是说电池快没电了,可以先换个电池试试,如果问题还是没有解决,那么说明C M O S R A M可能有问题,如果没过一年就到经销商处换一块主板,过了一年就让经销商送回生产厂家修一下吧! 3.P r e s s E S C t o s k i p m e m o r y t e s t 中文:正在进行内存检查,可按E S C键跳过。 解释:这是因为在C M O S内没有设定跳过存储器的第二、三、四次测试,开机就会执行四次内存测试,当然你也可以按E S C键结束内存检查,不过每次都要这样太麻烦了,你可以进入C O M S设置后选择B I O S F E A T U R S S E T U P,将其中的Q u i c k P o w e r O n S e l f T e s t设为 E n a b l e d,储存后重新启动即可。 4.K e y b o a r d e r r o r o r n o k e y b o a r d p r e s e n t 中文:键盘错误或者未接键盘。 解释:检查一下键盘的连线是否松动或者损坏。 5.H a r d d i s k i n s t a l l f a i l u r e

LVDS接口与MIPI接口

LVDS接口与MIPI接口 MIPI?(Mobile Industry Processor Interface) 是2003年由ARM, Nokia, ST ,TI等公司成立的一个联盟,目的是把手机内部的接口如摄像头、显示屏接口、射频/基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性。 MIPI联盟下面有不同的WorkGroup,分别定义了一系列的手机内部接口标准,比如摄像头接口CSI、显示接口DSI、射频接口DigRF、麦克风 /喇叭接口SLIMbus等。统一接口标准的好处是手机厂商根据需要可以从市面上灵活选择不同的芯片和模组,更改设计和功能时更加快捷方便。下图是按照 MIPI的规划下一代智能手机的内部架构。 MIPI是一个比较新的标准,其规范也在不断修改和改进,目前比较成熟的接口应用有DSI(显示接口)和CSI(摄像头接口)。CSI/DSI分别是指其承载的是针对Camera或Display应用,都有复杂的协议结构。以DSI为例,其协议层结构如下:

CSI/DSI的物理层(Phy Layer)由专门的WorkGroup负责制定,其目前的标准是D-PHY。D-PHY 采用1对源同步的差分时钟和1~4对差分数据线来进行数据传输。数据传输采用DDR方式,即在时钟的上下边沿都有数据传输。 D- PHY的物理层支持HS(High Speed)和LP(Low Power)两种工作模式。HS模式下采用低压差分信号,功耗较大,但是可以传输很高的数据速率(数据速率为80M~1Gbps); LP模式下采用单端信号,数据速率很低(<10Mbps),但是相应的功耗也很低。两种模式的结合保证了MIPI总线在需要传输大量数据(如图像)时可以高速传输,而在不需要大数据量传输时又能够减少功耗。下图是用示波器捕获的MIPI信号,可以清楚地看到HS和LP信号。

[精品教程] 主板刷BIOS详细图文教程

BIOS是英文"Basic Input Output System"的缩略语,直译过来后中文名称就是"基本输入输出系统"。其实,它是一组固化到计算机内主板上一个ROM芯片上的程序,它保存着计算机最重要的基本输入输出的程序、系统设置信息、开机上电自检程序和系统启动自举程序。其主要功能是为计算机提供最底层的、最直接的硬件设置和控制。BIOS设置程序是储存在BIOS芯片中的,只有在开机时才可以进行设置。CMOS主要用于存储BIOS设置程序所设置的参数与数据,而BIOS设置程序主要对计算机的基本输入输出系统进行管理和设置,使系统运行在最好状态下,使用BIOS设置程序还可以排除系统故障或者诊断系统问题。无论是解决现在主板上已经存在的问题,还是要支持新型号的CPU,学会如何刷主板BIOS 是这一切的先决条件,虽然说刷主板BIOS是一件有危险的事情,一旦出现意外很可能会刷坏BIOS,让主板无法启动,不过在笔者看来,只要操作的当,并且刷BIOS过程中没有发生断电一类的意外,刷BIOS还是一件比较简单的事情,今天就让我们一起来体验一下。 下载BIOS文件: 要刷新主板的BIOS,那肯定首先要拿到的是该主板最新的BIOS文件,这个文件去哪里找呢?当然是上主板厂商的官方网站去找,而一些类似驱动之家的网站上也有提供,不过相对而言,在官方网站上更容易找到,同时也是最新的。台系厂商,因为在大陆的网站建设上可能有一定的滞后,因此如果在大陆的简体中文的网站上没有找到最新的BIOS的话,不妨到台湾地区的官方网站上去寻找。 启动U盘制作: 虽然有部分品牌的主板上集成有BIOS刷新工具,不过更多的主板是没有的。刷新主板BIOS一般来说在都是在DOS系统下进行,并且现在的U盘价格非常的便宜,制作一个启动U 盘也是很方便的,当然,如果是用启动光盘启动到DOS系统也是可以的,这里的要求并不严格。 解压BIOS压缩包: 现在,将下载下来的BIOS压缩包解压缩,一般来说,下载下来的BIOS文件压缩包中,都会顺带提供有刷BIOS的工具软件,从文件体积上我们就可以很容易的分辨出BIOS文件,BIOS文件解压缩后都为1024KB的大小,而exe后缀的文件即为厂商提供的刷新BIOS的工具软件。当然,也有的厂商提供的是后缀为bat的批处理文件,提供了批处理文件的BIOS 刷新更加的简单。当然,也有一些主板品牌没有提供刷新工具,这就需要用户自己去下载工具了。 一般来说,主板BIOS主要为Phoenix、AMI、Award这三个公司出品,需要用户自己去下载刷新工具。而Phoenix已经收购了Award,现在Award生产的BIOS只能在一些旧的主板上见到了。关于区分BIOS生产厂商,在BIOS设置界面中的上端可以看到,例如下图的这个就是Phoenix公司生产。