FPGA实验报告

FPGA实验报告专业:电子信息科学与技术

注:以下所有设计均选用DE2-115开发板

FPGA 器件选用Cyclone IV E:EP4CE115F29C7 所有设计均在开发板上已通过硬件验证

8位全加器

1. 源代码

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity adder8 is

port (a,b: in std_logic_vector(7 downto 0);

cin: in std_logic;

dout: out std_logic_vector(7 downto 0);

cout: out std_logic);

end entity adder8;

architecture behav of adder8 is

signal data: std_logic_vector(8 downto 0);

begin

data<=('0'&a)+('0'&b)+("00000000"&cin);

cout<=data(8);

dout<=data(7 downto 0);

end behav;

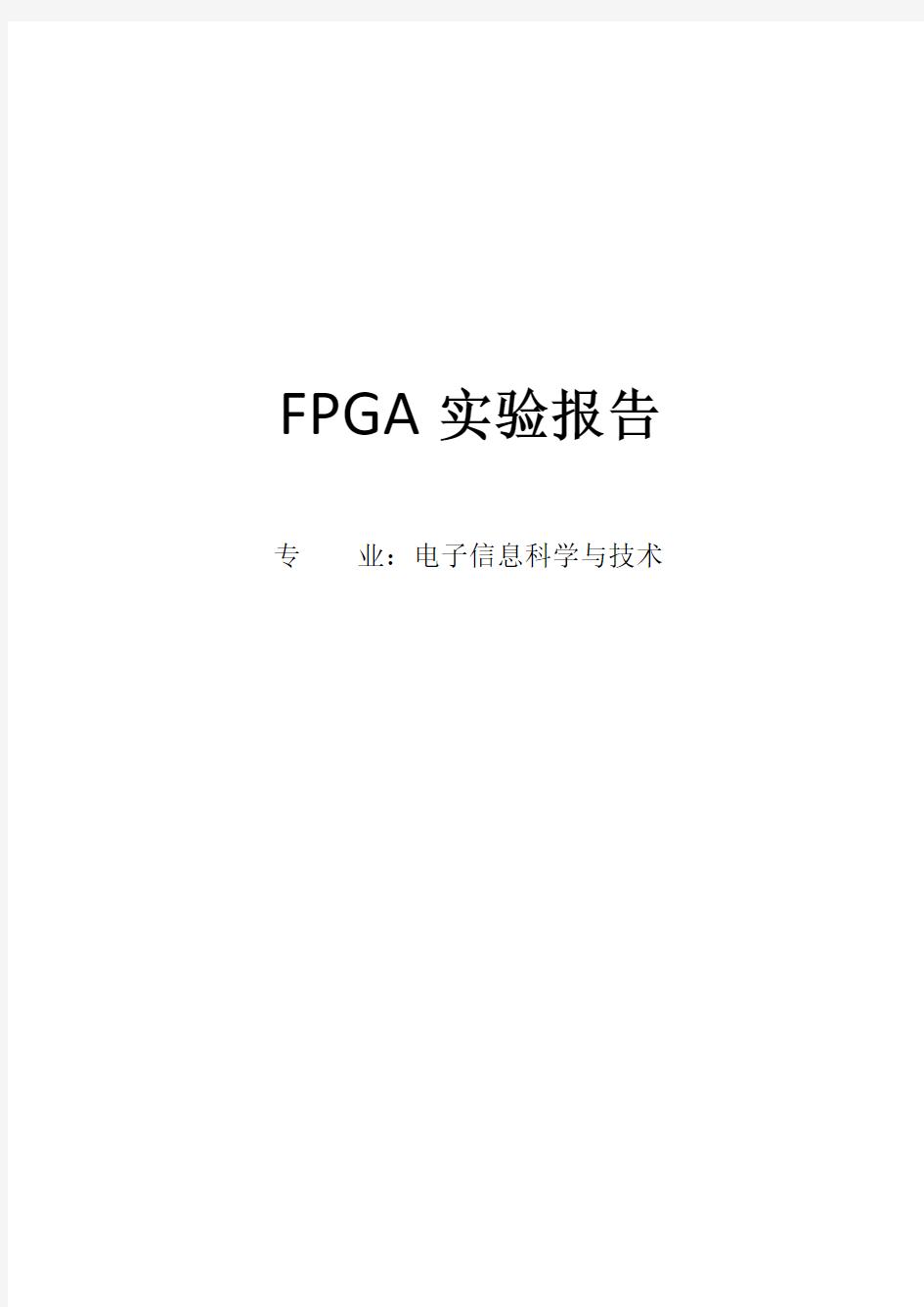

2. 仿真结果

3. 引脚分配

通过DE2-115上9个LEDG,17个拨动开关对应八位全加器中所有输入输出。其中LEDG[8]表示进位输出cout,LEDG[7]~LEDG[0]对应dout(7 downto

0),SW[7]~SW[0]对应a(7 downto 0),SW[15]~SW[8]对应b(7 downto 0),SW[16]对应

低位进位输入端cin。具体引脚分配在工程文件中。

智能抢答器

1.设计要求

设计一个4人参加的智力竞赛抢答器,每人有1个对应的按钮。在主持人的主持下,参赛者通过抢先按下按钮获得答题资格,同时七段数码管会显示抢答成功者的号码。

2. 基本功能

4人抢答器,要求抢答开始后4人抢答,抢答结果在数码管上显示,复位后下一次抢答开始

3. 设计模块

抢答模块

源代码

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity qdq1 is

port

(

qout: out std_logic_vector(3 downto 0);

host : in std_logic; ----CONNECT TO RESET

answer : in std_logic_vector(3 downto 0);

light : out std_logic_vector(3 downto 0)

);

end qdq1;

architecture rtl of qdq1 is

signal lock:std_logic;

begin

process (host,answer,lock)

begin

if(host='0')then

light<="0000";

lock<='0';

qout<="0000";

elsif (lock='0')then

case answer is

when "0001"=>light<="0001";qout<="0001";lock<='1';

when "0010"=>light<="0010";qout<="0010";lock<='1';

when "0100"=>light<="0100";qout<="0100";lock<='1';

when "1000"=>light<="1000";qout<="1000";lock<='1';

when others=>light<="0000";

end case;

end if;

end process;

end rtl;

显示模块

源代码

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity decode7 is

port(hex:out std_logic_vector(6 downto 0);

qin: in std_logic_vector(3 downto 0);

rest: in std_logic);

end decode7;

architecture behav of decode7 is

begin

process(qin)

begin

if rest ='0' then

hex(6 downto 0)<="1000000";

else

case qin is

when "0001"=>hex(6 downto 0)<="1111001";

when "0010"=>hex(6 downto 0)<="0100100";

when "0100"=>hex(6 downto 0)<="0110000";

when "1000"=>hex(6 downto 0)<="0011001";

when others=>hex(6 downto 0)<="1111111";

end case;

end if;

end process;

end behav;

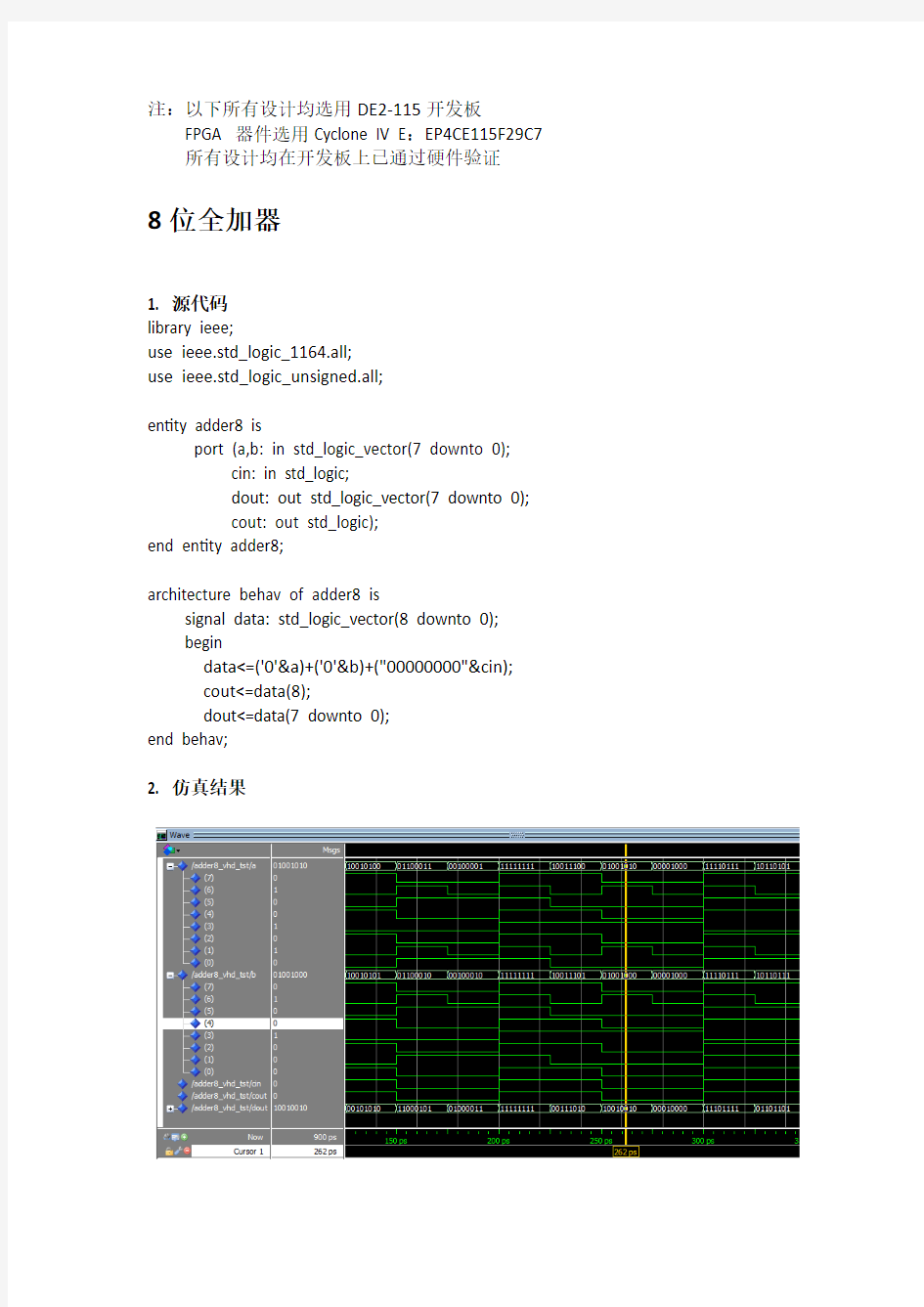

顶层模块设计采用原理图输入

4. 引脚分配

SW[0]对应host(主持人),SW[4]~SW[1]对应四个回答者a(3 downto 0), LEDG(3)~LEDG(0)对应显示a(3 downto 0)的显示状态。七段数码管对应显示四个回答者的相应编号。具体引脚分配在工程文件中。

数字钟

1.功能说明

能进行正常的时、分、秒计时功能,并分别由相应数码管上显示时(24hour)、分(60min)、秒(60s)的时间,且能具有校时功能。

2.设计思路

先设计出60进制(分,秒),24进制计数器(时),分频器,2选1选择器,七段数码管译码这些子模块,再进行顶层模块综合设计。

3.模块设计

-------------------------------

--60进制模块源代码---

-------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity fen60 is

port(clk: in std_logic;

rst: in std_logic; --复位

qout1: out std_logic_vector(3 downto 0);

qout2: out std_logic_vector(3 downto 0);

carry: out std_logic);

end fen60;

architecture behav of fen60 is

signal tem1: std_logic_vector(3 downto 0);

signal tem2: std_logic_vector(3 downto 0);

begin

process(clk,rst)

begin

if(rst='1') then

tem1<="0000";

tem2<="0000";

elsif (clk'event and clk='1') then

if tem1="1001" then

tem1<="0000";

if tem2="0101" then

tem2<="0000";

carry<='1';

else

tem2<=tem2+1;

carry<='0';

end if;

else

tem1<=tem1+1;

end if;

end if;

qout1<=tem1;

qout2<=tem2;

end process;

end behav;

--------------------------

---24进制源代码---

--------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity fen24 is

port(clk: in std_logic;

rst: in std_logic;

qout1: out std_logic_vector(3 downto 0);

qout2: out std_logic_vector(3 downto 0);

carry: out std_logic);

end fen24;

architecture behav of fen24 is

signal tem1: std_logic_vector(3 downto 0);

signal tem2: std_logic_vector(3 downto 0);

begin

process(clk,rst)

begin

if(rst='1') then

tem1<="0010";

tem2<="0001";

elsif (clk'event and clk='1') then

if tem2="0010" and tem1="0011" then

tem1<="0000";

tem2<="0000";

else

carry<='0';

if tem1="1001" then

tem1<="0000";

tem2<=tem2+1;

else

tem1<=tem1+1;

end if;

end if;

end if;

qout1<=tem1;

qout2<=tem2;

end process;

end behav;

---------------------

-----分频器------

---------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity fp1hz is

port(clk:in std_logic;

clk1hz:out std_logic);

end fp1hz;

architecture behav of fp1hz is

signal cnt:integer range 0 to 49999999; begin

process(clk)

begin

if clk'event and clk='1' then

if cnt=49999999 then

cnt<=0;

else

cnt<=cnt+1;

end if;

if cnt<25000000 then

clk1hz<='1';

else

clk1hz<='0';

end if;

end if;

end process;

end behav;

------------------------------

-----2选1选择器------

-----------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity mux21 is

port(

a : in std_logic;

b : in std_logic;

c : out std_logic;

ctrol: in std_logic);

end mux21;

architecture behav of mux21 is

signal tem: std_logic;

begin

process(ctrol)

begin

if ctrol='0' then

tem<=a;

else

tem<=b;

end if;

c<=tem;

end process;

end behav;

-----------------------------

----七段数码管译码---

-----------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity decode7 is

port(hex:out std_logic_vector(6 downto 0);

qin: in std_logic_vector(3 downto 0));

end decode7;

architecture behav of decode7 is

begin

process(qin)

begin

case qin is

when "0000"=>hex(6 downto 0)<="1000000";

when "0001"=>hex(6 downto 0)<="1111001";

when "0010"=>hex(6 downto 0)<="0100100";

when "0011"=>hex(6 downto 0)<="0110000";

when "0100"=>hex(6 downto 0)<="0011001";

when "0101"=>hex(6 downto 0)<="0010010";

when "0110"=>hex(6 downto 0)<="0000010";

when "0111"=>hex(6 downto 0)<="1111000";

when "1000"=>hex(6 downto 0)<="0000000";

when "1001"=>hex(6 downto 0)<="0010000";

when others=>hex(6 downto 0)<="1111111";

end case;

end process;

end behav;

顶层模块设计采用原理图输入:

4. 引脚分配

SW[0]对应复位,SW[1]、SW[2]分别对应校分,校时。HEX[5]~HEX[0]分别对应时十位数、时个位数、分十位数、分个位数、秒十位数、秒个位数。当复位引脚rst 有效时,时钟复成12:00:00。具体引脚分配在工程文件中。

广告灯的设计

1.功能说明

可实现8个LED的闪烁广告灯控制。显示规律为左向流水、右向流水、拉幕式、闭幕式,隔灯闪烁、高四灯-低四灯闪烁几次如此重复循环,可实现闪烁的快慢控制。

2.设计思路

采用分模块设计的思想,先设计分频,显示等子模块,再设计顶层模块并综合。

3.模块设计

----------------------------------

----50MHZ分频为1HZ----

---------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity fp is

port(clk:in std_logic;

clk1hz:out std_logic);

end fp;

architecture behav of fp is

signal cnt:integer range 0 to 49999999;

begin

process(clk)

begin

if clk'event and clk='1' then

if cnt=49999999 then

cnt<=0;

else

cnt<=cnt+1;

end if;

if cnt<25000000 then

clk1hz<='1';

else

clk1hz<='0';

end if;

end if;

end process;

end behav;

---------------------

-----2 分频-------

---------------------

library ieee;

use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity fp1 is

port(clk:in std_logic;

clkhz:buffer std_logic); end fp1;

architecture behav of fp1 is

signal cnt: integer range 0 to 1; begin

process(clk)

begin

if clk'event and clk='1' then

if cnt=1 then

cnt<=0;

else

cnt<=cnt+1;

end if;

if cnt<1 then

clkhz<='1';

else

clkhz<='0';

end if;

end if;

end process;

end behav;

------------------------------

-----LED 显示模块------

------------------------------

library ieee;

use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all;

entity show is

port(clk:in std_logic;

aout:out std_logic_vector(0 to 7)); end show;

architecture behav of show is

begin

process(clk)

variable cnt:integer range 0 to 23;

begin

if (clk'event and clk='1') then

if (cnt>24) then

cnt:=0;

else

cnt:=cnt+1;

end if;

case cnt is

----左向流水-----

when 0=> aout<="00000001";

when 1=> aout<="00000010";

when 2=> aout<="00000100";

when 3=> aout<="00001000";

when 4=> aout<="00010000";

when 5=> aout<="00100000";

when 6=> aout<="01000000";

----------------------

----右向流水-----

when 7=> aout<="10000000";

when 8=> aout<="01000000";

when 9=> aout<="00100000";

when 10=> aout<="00010000";

when 11=> aout<="00001000";

when 12=> aout<="00000100";

when 13=> aout<="00000010";

when 14=> aout<="00000001";

---------------------

----全亮全灭----

when 15=> aout<="11111111";

when 16=> aout<="00000000";

---------------------------------

----高四灯-低四灯闪烁--

when 17=> aout<="11110000";

when 18=> aout<="00001111";

when 19=> aout<="11110000";

when 20=> aout<="00001111";

-----------------------

----隔灯闪烁------

when 21=> aout<="10101010";

when 22=> aout<="01010101";

when 23=> aout<="00000000";

------------------

when others=> null;

end case;

end if;

end process;

end behav;

顶层模块采用原理图输入

4. 引脚分配

LEDG[0]~LEDG[7]对应aout (0 to 7);SW[0]控制闪烁时间间隔,SW[0]为‘0’时,闪烁间隔为1 s ,SW[0]为‘1’时,闪烁间隔为2 s ,具体引脚分配在工程文件中。

结语:

通过综合实验的思考和设计,对一个项目的整体设计有了进一步认识,加深了对VHDL语言的了解,提高了编程能力。同时,锻炼了独立发现问题解决问题的能力,提高了个人素质。利用硬件描述语言VHDL编程,借助Altera公司

的quartus II及modlesim软件环境下进行了编译及仿真测试,通过FPGA芯片实现了几个实际可行的的控制系统,如数字时钟,设计由于采用了EDA技术,不但大大缩短了开发研制周期,提高了设计效率,而且使系统具有设计灵活,实现简单,性能稳定的特点。

这是一次颇有收获的实训,这次的实训中,我们更进一步体会到自主学习和团队合作的乐趣与必要性。为了完成项目,在网络上找到了许多相关资料,大大扩充自己的知识面,使许多以前想解决却无法解决的困难迎刃而解,这才知道老师的良苦用心。相信以后的我不管是做网络亦或是从事软、硬件开发,都会有一个扎实的基础和良好的开发习惯的。

通过这次课程设计真正体会到了课本上的知识是在做解决实际的问题时,是远远不够的,实际问题不是像理论知识那样,更多的是需要自己动手去操作,遇到问题时参考资料,咨询老师或是其他方式去解决问题,在此次设计过程中提升了如何解决问题的能力,找对方法,多动手实践才能解决问题。

不管这样,这次课程设计终于顺利完成了,我学也到很多实用的知识,学到了很多课内学不到的东西,比如独立思考解决问题,出现差错的随机应变,和与人合作共同提高,都受益非浅。在此,感谢老师的细心指导!

若需工程文件夹可联系:1927377679