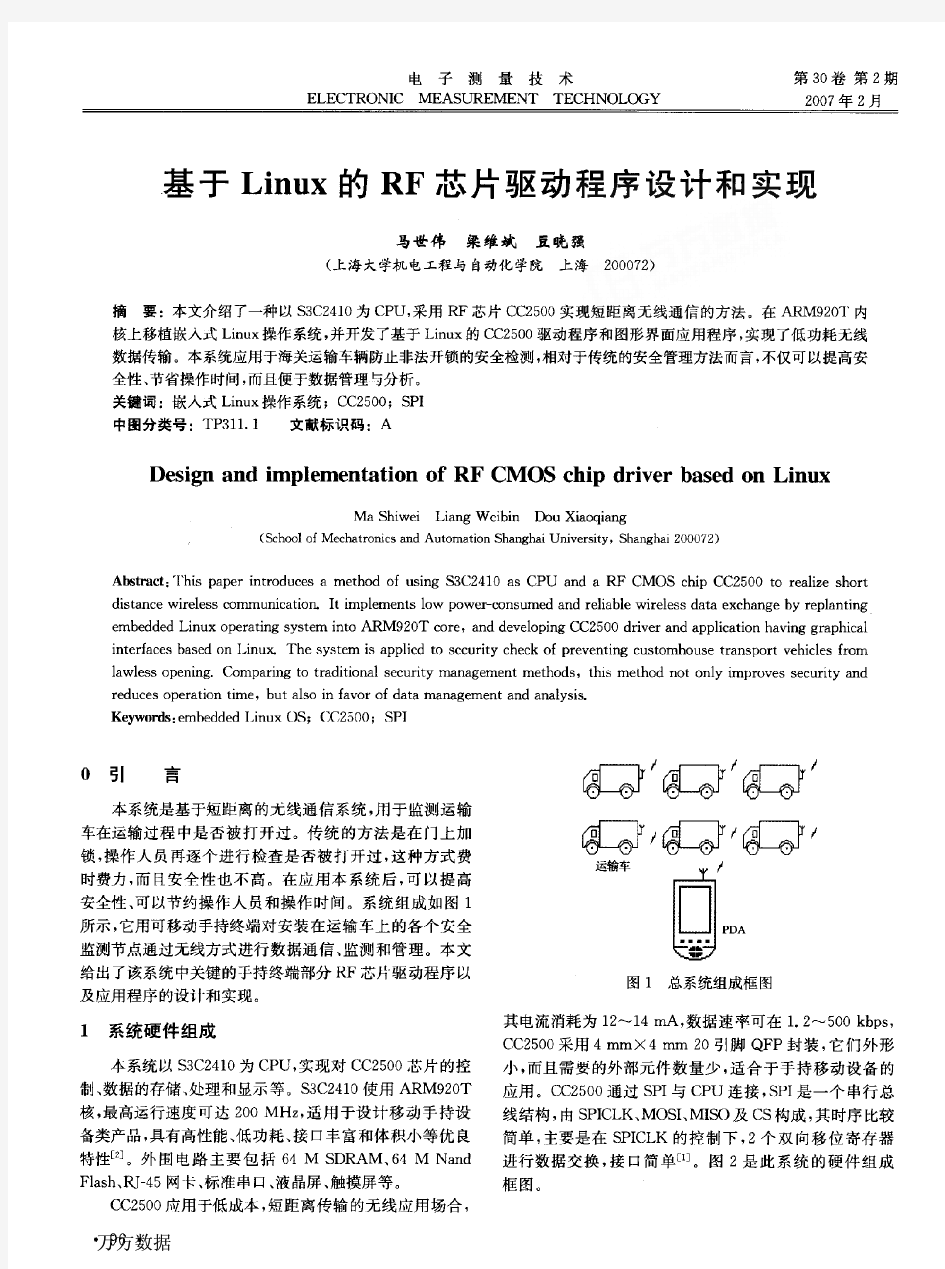

基于Linux的RF芯片驱动程序设计和实现

射频电路调试测试流程

射频电路调试测试流程(准备阶段) 射频电路的调试作为通信整机研发工作中的重要一环,工作量非常大,几乎所有电路都需要调试,为了提高效率,需要对调试环境、调试方法等进行规范。 环境准备如下 1、防静电 佩戴“静电手环”,并良好接地,若着化纤、羊毛、羽绒服装,外层需加穿防静电服,或防辐射服;小功率、低电压、高频率、小封装的器件均ESD敏感,最容易被ESD击穿的射频器件:RF开关,其次是LNA;所有仪器,开机使用前必须将机壳良好接地;2、电源 稳压电源接入负载前,先校准输出电压,电压等于负载的额定电压; 3、仪器保护 为安全起见:只要射频功率大于20dBm,射频信号源(30dBm)、频谱分析仪(27dBm)、信号源分析仪(23dBm)输入端必须级联同轴衰减器,一般情况下,5W 5dB衰减器为常态配置,若测试功放模块需根据实际输出功率大小配置合适的衰减器; 4、仪器设置 射频信号源:Keysight输出功率<13dBm,R&S输出功率<18dBm,若超出,输出功率可能小于显示值,需实测并进行补偿; 频谱分析仪:屏幕显示的有效动态范围,FSV约70dB,FSW约80dB;仪器的线性输入功率<-3dBm,超出会恶化待测IM3(ACLR)、谐波,应选择合适的内部/外部衰减值; 矢量网络分析仪:仪器的IF带宽决定噪声,测无源器件的带外抑制,应适当降低IF带宽;调测任何电路,必须保证输出功率 摘要:近年来,射频(RF)无线通信技术的迅速发展增加了人们对低电压高性能射频前端的需求,无线通讯系统中的关键模块-RFIC 成为当前的研究热点,如:蜂窝式个人通信与基站、无线接入系统、卫星通信、全球卫星定位系统、无线局域网等。经过三代移动通信的发展,通信系统发展成了支持多媒体的通信系统,系统的速度更快,误码率更低。射频收发机是通信系统的前端部分,负责信号的接收和发射部分,是无线通信系统中不可缺少的一部分,它决定了通信距离和影响着通信质量通信系统的发展也带动了射频收发机的发展。本论文探讨了收发机的基本结构,射频收发机的发展,然后介绍了射频收发机的一些关键指标,然后根据重要指标计算出射频系统的主要技术指标,最后仿真整个收发机的主要技术指标。 关键词:移动通信;射频收发机;系统指标 RF transceiver system design based on wireless communication In recent years,the rapid development of radio frequency (RF) wireless communication increase the RF front-end needs of low-voltage and high-performance.The key modules-RFIC of Wireless communication systems become research focus,such as cellular personal communications and base station, wireless access systems, Satellite Communications,GPS, wireless lan,etc. After the development of three generations of mobile communications, communications system developed into a multimedia communication system and the system has faster rate and lower BER. RFtransceiver which is front of the communication system is responsible for receiving and transmitting the signal part and that is an integral part the wireless communication system. RF transceiver determines the distance of communication and affects the communication s quality. The development of communication system has also led to thedevelopment of the RF transceiver. The paper discussed transceiver's basic structure and radio frequency transceiver's development and some key indicators. Then according to these important target, it has calculated the radio frequency system's major technique target. Finally it simulated entire transceiver's major technique target. Keywords: mobile communication RF transceiver system specifications 1引言 射频是指该频率的载波功率能通过天线发射出去(反之亦然),以交变的电磁场形式在自由空间以光速传播,碰到不同介质时传播速率发生变化,也会发生电磁波反射、折射、绕射、穿透等,引起各种损耗。在金属线传输时具有趋肤效应现象[1]。 该频率在各种无源和有源电路中R, L, C各参数反映出是分布参数。因此说所谓射频RF (Radio Frequency)是指频率较高,可用于发射无线电频率,一般常指几十到几百兆赫的频 1 前言 (2) 2 工程概况 (2) 3 正文 (2) 3.1零中频接收系统结构性能和特点 (3) 3.2基于ADS2009对零中频接收系统设计与仿真 (3) 3.3超外差接收系统结构性能和特点 (12) 3.4基于ADS2009对超外差接收系统设计与仿真 (13) 4 有关说明 (16) 5 心得体会 (18) 6 致谢 (18) 7 参考文献 (19) 射频是一种频谱介于75kHz-3000GHz之间的电波,当频谱范围介于20Hz-20kHz之间时,这种低频信号难以直接用天线发射,而是要利用无线电技术先经过转换,调制达到一定的高频范围,才可以借助无线电电波传播。射频技术实质是一种借助电磁波来传播信号的无线电技术。 无线电技术应用最早从18世纪下半段开始,随着应用领域的扩大,世界已经对频谱进行了多次分段波传播。当前,被广泛采用的频谱分段方式是由电气和电子工程师学会所规定的。随着科学技术的不断发展,射频所含频率也不断提高。到目前为止,经过两个多世纪的发展,射频技术也已经在众多领域的到应用。特别是高频电路的应用。其中在通信领域,射频识别是进步最快的重要方面。 工程概况 近年来随着无线通信技术的飞速发展,无线通信系统产品越来越普及,成为当今人类信息社会发展的重要组成部分。射频接收机位于无线通信系统的最前端,其结构和性能直接影响着整个通信系统。优化设计结构和选择合适的制造工艺,以提高系统的性能价格比,是射频工程师追求的方向。由于零中频接收机具有体积小、成本低和易于单片集成的特点,已成为射频接收机中极具竞争力的一种结构,在无线通信领域中受到广泛的关注。本文在介绍超外差结构和零中频结构性能和特点的基础上,对超外差结构和零中频结构进行设计与仿真。 正文 下面设计一个接收机系统,使用行为级的功能模块实现收信机的系统级仿真。 集成电路版图设计 班级12级微电子姓名陈仁浩学号2012221105240013 摘要:介绍了集成电路版图设计的各个环节及设计过程中需注意的问题,然后将IC版图设计与PCB版图设计进行对比,分析两者的差异。最后介绍了集成电路版图设计师这一职业,加深对该行业的认识。 关键词: 集成电路版图设计 引言: 集成电路版图设计是实现集成电路制造所必不可少的设计环节,它不仅关系到集成电路的功能是否正确,而且也会极大程度地影响集成电路的性能、成本与功耗。近年来迅速发展的计算机、通信、嵌入式或便携式设备中集成电路的高性能低功耗运行都离不开集成电路掩模版图的精心设计。一个优秀的掩模版图设计者对于开发超性能的集成电路是极其关键的。 一、集成电路版图设计的过程 集成电路设计的流程:系统设计、逻辑设计、电路设计(包括:布局布线验证)、版图设计版图后仿真(加上寄生负载后检查设计是否能够正常工作)。集成电路版图设计是集成电路从电路拓扑到电路芯片的一个重要的设计过程,它需要设计者具有电路及电子元件的工作原理与工艺制造方面的基础知识,还需要设计者熟练运用绘图软件对电路进行合理的布局规划,设计出最大程度体现高性能、低功耗、低成本、能实际可靠工作的芯片版图。集成电路版图设计包括数字电路、模拟电路、标准单元、高频电路、双极型和射频集成电路等的版图设计。具体的过程为: 1、画版图之前,应与IC 工程师建立良好沟通在画版图之前,应该向电路设计者了解PAD 摆放的顺序及位置,了解版图的最终面积是多少。在电路当中,哪些功能块之间要放在比较近的位置。哪些器件需要良好的匹配。了解该芯片的电源线和地线一共有几组,每组之间各自是如何分布在版图上的? IC 工程师要求的工作进度与自己预估的进度有哪些出入? 2、全局设计:这个布局图应该和功能框图或电路图大体一致,然后根据模块的面积大小进行调整。布局设计的另一个重要的任务是焊盘的布局。焊盘的安排要便于内部信号的连接,要尽量节省芯片面积以减少制作成本。焊盘的布局还应该便于测试,特别是晶上测试。 3、分层设计:按照电路功能划分整个电路,对每个功能块进行再划分,每一个模块对应一个单元。从最小模块开始到完成整个电路的版图设计,设计者需要建立多个单元。这一步就是自上向下的设计。 4、版图的检查: (1)Design Rules Checker 运行DRC,DRC 有识别能力,能够进行复杂的识别工作,在生成最终送交的图形之前进行检查。程序就按照规则检查文件运行,发现错误时,会在错误的地方做出标记,并且做出解释。 1引言 近几年来,无线射频识别技术越来越受各国重视。随着供应链管理、集装箱、工业、科研和医药等行业对3m以上射频识别技术的需求不断增加,国内外已经把研究的热点转向超高频段和微波频段。射频电路的设计主要围绕着低成本、低功耗、高集成度、高工作频率和轻重量等要求进行。本文对915 M Hz射频收发系统做了进一步的研究。 ADS(Advanced Design System)软件是Agilent 公司开发的,可以支持从模块到系统的设计,能够完 915MHz射频收发系统的 ADS设计与仿真 李宝山,张香泽 (内蒙古科技大学信息工程学院,内蒙古包头014010) 摘要:针对无线通信环境中的应用,使用A D S软件设计了一种915M H z射频收发系统。射频收发系统中的关键模块均根据实际的集成射频模块的参数设计。使用A D S软件对设计进行功率增益预算仿真、S参数仿真。仿真结果表明,设计的射频收发系统符合实际的无线通信环境的要求。 关键词:A D S;915M H z收发系统;射频模块;增益 ADS Design and Simulation of915MHz RF Transceiver system LI Bao-shan,ZHANG Xiang-ze (School of Information Engineering,Inner Mongolia University of Science and Technology,Baotou014010,China) Abstract:The design and simulation of915M Hz RF Transceiver system using Advanced Design System(ADS)for wireless communication application is presented.The key modules in RF system are designed by using the parameters ofactual integrated RF modules.Some simulations have been done by using ADS,such as Budget simulation,S parameter simulation.The simulation results show that this RF transceiver system with real wireless communication demand. Keywords:ADS;915MHz RF Transceiver system;RF module;gain 无线通信射频收发系统设计研究 射频是一种特定频率的电磁波信号,它可以在自由空间中传播,射频通信技术具有宽频带、高信息容量、体积小、可用频谱多、干扰小等特点,在无线通信系统中应用广泛,日常生活中有线电视信号就是通过由射频通信系统传送的。射频收发系统处理线通信系统中信号的接收和发射,它位于无线通信系统的最前端,关系到通信的质量。研究射频收发系统工作原理优化其设计方案,可有效提高无线通信质量。 一、射频收发系统的构成及工作原理 射频收发系统根据它的应用目的和使用环境的不同,会有不同的组成部分。但从射频收发系统的工作原理来看,射频发射机、射频接收机、天线是系统的基本组成部分。(一)射频发射机的构成及工作原理。射频发射机是通过调制、功率放大、上变频、滤波等手段把低频的基本频带信号转换为对应的高频信号,并把处理后的信号经天线发出。天线、滤波器、数模转换器、调制器、混频器、放大器、本振器等组成射频发射机系统。调制器通过数字调制或模拟调制的方式将低频信号向高频段传播;本振器通过数字分频电路、鉴相器电路,锁相环电路等将频率送至混频器;滤波器可以对不同的信号进行分离,得到特定频率的信号或消除干扰信号,滤波器种类繁多,实际使用时可根据需要处理信号的形式选用模拟滤波器或数字滤波器;数模转换器主要作用是完成数字信号到模拟信号的转换;混频器主要作用是实现频率变化,常用的有双平衡混频器和三平衡混频器。放大器是把信号通过幅度放大器增大或降低,在经由功率放大器将信号功率放大用以满足天线发射需要。(二)射频接收机的构成及工作原理。射频接收机主要作用是从天线接收的众多信号中选出基本频带所需的有用信号并放大。射频接收机的信号选择能力关系到信号的接收质量,影响无线通信射频收发系统的运行状况。射频接收机把天线接收到信号传送至低噪声放大器,通过两次下变频,将信号变为满足需要的基本频带信号。射频接收机主要性能指标要求包括:接收微弱信号的灵敏度要求,降低系统噪声系数要求,相似频率信号的选择能力要求及射频接收机接收信号大小比的动态范围要求,射频接收机的性能指标关系到无线通信射频收发系统运行质量。 集成电路版图设计笔试面试大全 1. calibre语句 2. 对电路是否了解。似乎这个非常关心。 3. 使用的工具。 , 熟练应用UNIX操作系统和L_edit,Calibre, Cadence, Virtuoso, Dracula 拽可乐(DIVA),等软件进行IC版图 绘制和DRC,LVS,ERC等后端验证 4. 做过哪些模块 其中主要负责的有Amplifier,Comparator,CPM,Bandgap,Accurate reference,Oscillator,Integrated Power MOS,LDO blocks 和Pad,ESD cells以及top的整体布局连接 5. 是否用过双阱工艺。 工艺流程见版图资料 在高阻衬底上同时形成较高的杂质浓度的P阱和N阱,NMOS、PMOS分别做在这两个阱中,这样可以独立调节两种沟道MOS管的参数,使CMOS电路达到最优特性,且两种器件间距离也因采用独立的阱而减小,以适合于高密度集成,但是工艺较复杂。 制作MOS管时,若采用离子注入,需要淀积Si3N4,SiO2不能阻挡离子注入,进行调沟或调节开启电压时,都可以用SiO2层进行注入。 双阱CMOS采用原始材料是在P+衬底(低电阻率)上外延一层轻掺杂的外延层P-(高电阻率)防止latch-up效应(因为低电阻率的衬底可以收集衬底电流)。 N阱、P阱之间无space。 6. 你认为如何能做好一个版图,或者做一个好版图需要注意些什么需要很仔细的回答~答:一,对于任何成功的模拟版图设计来说,都必须仔细地注意版图设计的floorplan,一般floorplan 由设计和应用工程师给出,但也应该考虑到版图工程师的布线问题,加以讨论调整。总体原则是 模拟电路应该以模拟信号对噪声的敏感度来分类。例如,低电平信号节点或高阻抗节点,它们与输入信号典型相关,因此认为它们对噪声的敏感度很高。这些敏感信号应被紧密地屏蔽保护起来,尤其是与数字输出缓冲器隔离。高摆幅的模拟电路,例如比较器和输出缓冲放大器应放置在敏感模拟电路和数字电路之间。数字电路应以速度和功能来分类。显而易见,因为数字输出缓冲器通常在高速时驱动电容负载,所以应使它离敏感模拟信号最远。其次,速度较低的逻辑电路位于敏感模拟电路和缓冲输出之间。注意到敏感模拟电路是尽可能远离数字缓冲输出,并且最不敏感的模拟电路与噪声最小的数字电路邻近。 芯片布局时具体需考虑的问题,如在进行系统整体版图布局时,要充分考虑模块之间的走线,避免时钟信号线对单元以及内部信号的干扰。模块间摆放时要配合压焊点的分布,另外对时钟布线要充分考虑时延,不同的时钟信号布线应尽量一致,以保证时钟之间的同步性问题。而信号的走线要完全对称以克服外界干扰。 二(电源线和地线的布局问题 RFID相关射频芯片基本介绍与应用 (一)RC530 概述:RC530是NXP 公司出品的应用与13.56MHz非接触式通信中高集成读卡IC系列中的一员,该芯片完全集成了在13.56MHz下所有类型的被动非接触式通信方式和协议。MFRC530支持ISO14443A所有的层。RC530的外围电路入图所示。该电路由接收电路和单片机接口电路两部分组成。由于RC530内部接收部分使用一个受益于副载波双边带的概念装入卡响应的调整。推荐使用内部产生的VMID电势作为RX脚的输入电势。为了提供一个稳定的参考电压,必须在VIMD脚接一个对地的电容C9,RX和VMID必须连接一个分压IC卡将回复自己UID,如果没有碰撞阅读器将收到完整的电路由R9,R10构成,而且天线与分压器间还需要用一个电容C10串接。由于IC卡工作在13.56Mhz下。石英晶体在产生用于驱动RC530和天线的13.56Mhz时钟时,还会产生更高频率的谐波。因此必须加上由 L1,L2,C11,C13组成的低通滤波电路。 (二)MF RC531 概述MF RC531 是应用于13.56MHz 非接触式通信中高集成读写卡芯片系列中的一员。该读写卡芯片系列利用了先进的调制和解调概念,完全集成了在13.56MHz 下所有类型的被动非接触式通信方式和协议。芯片管脚兼容MF RC500、MF RC530 和SL RC400。MF RC531 支持ISO/IEC14443A/B 的所有层和MIFARE? 经典协议,以及与该标准兼容的标准。支持高速MIFARE?非接触式通信波特率。内部的发送器部分不需要增加有源电路就能够直接驱动近操作距离的天线(可达100mm)。接收器部分提供一个坚固而有效的解调和解码电路,用于ISO14443A 兼容的应答器信号。数字部分处理ISO14443A 帧和错误检测(奇偶&CRC)。此外,它还支持快速CRYPTO1 加密算法,用于验证MIFARE 系列产品。与主机通信模式有8 位并行和SPI 模式,用户可根据不同的需求选择不同的模式,这样给读卡器/终端的设计提供了极大的灵活性。 特性 高集成度的调制解调电路; 采用少量外部器件,即可输出驱动级接至天线; 最大工作距离100mm; 支持ISO/IEC14443 A/B 和MIFARE? 经典协议; 支持非接触式高速通信模式,波特率可达424kb/s; 采用Crypto1 加密算法并含有安全的非易失性内部密匙存储器;? 管脚兼容MF RC500、MF RC530 和SL RC400; 与主机通信的2 种接口:并行接口和SPI,可满足不同用户的需求 自动检测微处理器并行接口类型; 灵活的中断处理; 64 字节发送和接收FIFO 缓冲区; 带低功耗的硬件复位; 可编程定时器; 唯一的序列号; 用户可编程初始化配置; 面向位和字节的帧结构; 数字、模拟和发送器部分经独立的引脚分别供电; 内部振荡器缓存器连接13.56MHz 石英晶体; linux驱动程序的编写 一、实验目的 1.掌握linux驱动程序的编写方法 2.掌握驱动程序动态模块的调试方法 3.掌握驱动程序填加到内核的方法 二、实验内容 1. 学习linux驱动程序的编写流程 2. 学习驱动程序动态模块的调试方法 3. 学习驱动程序填加到内核的流程 三、实验设备 PentiumII以上的PC机,LINUX操作系统,EL-ARM860实验箱 四、linux的驱动程序的编写 嵌入式应用对成本和实时性比较敏感,而对linux的应用主要体现在对硬件的驱动程序的编写和上层应用程序的开发上。 嵌入式linux驱动程序的基本结构和标准Linux的结构基本一致,也支持模块化模式,所以,大部分驱动程序编成模块化形式,而且,要求可以在不同的体系结构上安装。linux是可以支持模块化模式的,但由于嵌入式应用是针对具体的应用,所以,一般不采用该模式,而是把驱动程序直接编译进内核之中。但是这种模式是调试驱动模块的极佳方法。 系统调用是操作系统内核和应用程序之间的接口,设备驱动程序是操作系统内核和机器硬件之间的接口。设备驱动程序为应用程序屏蔽了硬件的细节,这样在应用程序看来,硬件设备只是一个设备文件,应用程序可以像操作普通文件一样对硬件设备进行操作。同时,设备驱动程序是内核的一部分,它完成以下的功能:对设备初始化和释放;把数据从内核传送到硬件和从硬件读取数据;读取应用程序传送给设备文件的数据和回送应用程序请求的数据;检测和处理设备出现的错误。在linux操作系统下有字符设备和块设备,网络设备三类主要的设备文件类型。 字符设备和块设备的主要区别是:在对字符设备发出读写请求时,实际的硬件I/O一般就紧接着发生了;块设备利用一块系统内存作为缓冲区,当用户进程对设备请求满足用户要求时,就返回请求的数据。块设备是主要针对磁盘等慢速设备设计的,以免耗费过多的CPU时间来等待。 1 字符设备驱动结构 Linux字符设备驱动的关键数据结构是cdev和file_operations结构体。 集成电路版图设计实验报告 班级:微电子1302班 学号:1306090226 姓名:李根 日期:2016年1月10日 一:实验目的: 熟悉IC设计软件Cadence Layout Editor的使用方法,掌握集成电路原理图设计,原理图仿真以及版图设计的流程方法以及技巧。 二:实验内容 1.Linux常用命令及其经典文本编辑器vi的使用 ①:了解Linux操作系统的特点。 ②:熟练操作如何登录、退出以及关机。 ③:学习Linux常用的软件以及目录命令。 ④:熟悉经典编辑器vi的基本常用操作。 2.CMOS反相器的设计和分析 ①:进行cmos反相器的原理图设计。 ②:进行cmos反相器的原理图仿真。 ③:进行cmos反相器的版图设计。 3.CMOS与非门的设计和分析 ①:进行cmos与非门的原理图设计。 ②:进行cmos与非门的原理图仿真。 ③:进行cmos与非门的版图设计 4.CMOS D触发器的设计和分析 ①:进行cmosD触发器的原理图设计。 ②:进行cmosD触发器的原理图仿真。 ③:进行cmosD触发器的版图设计。 5.对以上的学习进行总结 ①:总结收获学习到的东西。 ②:总结存在的不足之处。 ③:展望集成电路版图设计的未来。 三:实验步骤(CMOS反相器) 1.CMOS反相器原理图设计 内容:首先建立自己的Library,建立一个原理图的cell,其次进行原理图通过调用库里面的器件来绘制原理图,然后进行检错及修正,具体操作如下:在Terminal视窗下键入icfb,打开CIW; Tool→Library Manager; File→New→Library; 在name栏填上Library名称; 选择Compile a new techfile; 键入~/0.6um.tf; File→New→Cell view,在cell name键入inv,tool选择schematic,单击OK; 点击Schematic视窗上的指令集Add→Instance,出现Add Instance视窗; 通过Browse analogLib库将要用到的元件添加进来; 基于无线通信射频收发机系统的设计 李夏 11720925 靳立兴 11720929 2011年11月20号 摘要:近年来,射频(RF)无线通信技术的迅速发展增加了人们对低电压高性能射频前端的需求,无线通讯系统中的关键模块-RFIC 成为当前的研究热点,如:蜂窝式个人通信与基站、无线接入系统、卫星通信、全球卫星定位系统、无线局域网等。经过三代移动通信的发展,通信系统发展成了支持多媒体的通信系统,系统的速度更快,误码率更低。射频收发机是通信系统的前端部分,负责信号的接收和发射部分,是无线通信系统中不可缺少的一部分,它决定了通信距离和影响着通信质量通信系统的发展也带动了射频收发机的发展。本论文探讨了收发机的基本结构,射频收发机的发展,然后介绍了射频收发机的一些关键指标,然后根据重要指标计算出射频系统的主要技术指标,最后仿真整个收发机的主要技术指标。 关键词:移动通信;射频收发机;系统指标 RF transceiver system design based on wireless communication In recent years,the rapid development of radio frequency (RF) wireless communication increase the RF front-end needs of low-voltage and high-performance.The key modules-RFIC of Wireless communication systems become research focus,such as cellular personal communications and base station, wireless access systems, Satellite Communications,GPS, wireless lan,etc. After the development of three generations of mobile communications, communications system developed into a multimedia communication system and the system has faster rate and lower BER. RFtransceiver which is front of the communication system is responsible for receiving and transmitting the signal part and that is an integral part the wireless communication system. RF transceiver determines the distance of communication and affects the communication s quality. The development of communication system has also led to thedevelopment of the RF transceiver. The paper discussed transceiver's basic structure and radio frequency transceiver's development and some key indicators. Then according to these important target, it has calculated the radio frequency system's major technique target. Finally it simulated entire transceiver's major technique target. Keywords: mobile communication RF transceiver system specifications 基于RF收发器Si4432A的无线射频收发系统设计 本文设计了一种基于无线收发芯片Si4432和C8051F930单片机的无线射频收发系统。该系统由发送模块和接收模块组成。发送模块主要将要发送的数据经C8051F930处理后,通过Si4432发送出去;在接收模块中,Si4432则将数据正确接收后通过液晶显示出来,从而实现短距离的无线通信。该系统实现了低功耗、小体积、高灵敏度条件下的高质量无线数据传输。 1 无线收发芯片Si443 2 Si4432芯片是Silicon Labs公司推出的一款高集成度、低功耗、多频段的EZRadioPRO系列无线收发芯片。其工作电压为1.9~3.6 V,20引脚QFN封装(4 mm4 mm),可工作在315/433/868/915 MHz四个频段;内部集成分集式天线、功率放大器、唤醒定时器、数字调制解调器、64字节的发送和接收数据FIFO,以及可配置的GPIO 等。Si4432在使用时所需的外部元件很少,1个30 MHz的晶振、几个电容和电感就可组成一个高可靠性的收发系统,设计简单,且成本低。Si4432的接收灵敏度达到-117 dB,可提供极佳的链路质量,在扩大传输范围的同时将功耗降至最低;最小滤波带宽达8 kHz,具有极佳的频道选择性;在240~960 MHz频段内,不加功率放大器时的最大输出功率就可达+20dBm,设计良好时收发距离最远可达2 km。Si4432可适用于无线数据通信、无线遥控系统、小型无线网络、小型无线数据终端、无线抄表、门禁系统、无线遥感监测、水文气象监控、机器人控制、无线RS485/RS232数据通信等诸多领域。 2 无线射频收发系统设计2.1 系统总体方案无线射频收发系统的结构框图如图1所示,由C8051F930单片机控制Si4432实现无线数据的收发。发送模块中的C8051F930将数据传送给Si4432进行编码处理,并以特定的格式经天线发送给接收模块。接收模块对接收到的射频信号放大、解调之后,再将数据送给主控制器C8051F930进行相应的处理,如送液晶显示等。系统提供了按键和液晶(OCM12864-9)等人机交互界面,还留有RS232接口可以实现与PC机通信。 2.2 系统硬件设计主控芯片选用Silicon Labs公司推出的单片机C8051F930。C8051F930 本讲主要概述Linux设备驱动框架、驱动程序的配置文件及常用的加载驱动程序的方法;并且介绍Red Hat Linux安装程序是如何加载驱动的,通过了解这个过程,我们可以自己将驱动程序放到引导盘中;安装完系统后,使用kudzu自动配置硬件程序。 Linux设备驱动概述 1. 内核和驱动模块 操作系统是通过各种驱动程序来驾驭硬件设备,它为用户屏蔽了各种各样的设备,驱动硬件是操作系统最基本的功能,并且提供统一的操作方式。正如我们查看屏幕上的文档时,不用去管到底使用nVIDIA芯片,还是ATI芯片的显示卡,只需知道输入命令后,需要的文字就显示在屏幕上。硬件驱动程序是操作系统最基本的组成部分,在Linux内核源程序中也占有较高的比例。 Linux内核中采用可加载的模块化设计(LKMs ,Loadable Kernel Modules),一般情况下编译的Linux内核是支持可插入式模块的,也就是将最基本的核心代码编译在内核中,其它的代码可以选择是在内核中,或者编译为内核的模块文件。 如果需要某种功能,比如需要访问一个NTFS分区,就加载相应的NTFS模块。这种设计可以使内核文件不至于太大,但是又可以支持很多的功能,必要时动态地加载。这是一种跟微内核设计不太一样,但却是切实可行的内核设计方案。 我们常见的驱动程序就是作为内核模块动态加载的,比如声卡驱动和网卡驱动等,而Linux最基础的驱动,如CPU、PCI总线、TCP/IP协议、APM(高级电源管理)、VFS等驱动程序则编译在内核文件中。有时也把内核模块就叫做驱动程序,只不过驱动的内容不一定是硬件罢了,比如ext3文件系统的驱动。 理解这一点很重要。因此,加载驱动时就是加载内核模块。下面来看一下有关模块的命令,在加载驱动程序要用到它们:lsmod、modprob、insmod、rmmod、modinfo。 lsmod 集成电路CAD 课程设计报告 一.设计目的: 1.通过本次实验,熟悉软件的特点并掌握使用软件的流程和设计方法; 2.了解集成电路工艺的制作流程、简单集成器件的工艺步骤、集成器件区域的层 次关系,与此同时进一步了解集成电路版图设计的λ准则以及各个图层的含义和设计规则; 3.掌握数字电路的基本单元CMOS 的版图,并利用CMOS 的版图设计简单的门电路, 然后对其进行基本的DRC 检查; 4. 掌握C)B (A F +?=的掩模板设计与绘制。 二.设计原理: 1、版图设计的目标: 版图 (layout ) 是集成电路从设计走向制造的桥梁,它包含了集成电路尺寸、 各层拓扑定义等器件相关的物理信息数据。版图设计是创建工程制图(网表)的精确的物理描述过程,即定义各工艺层图形的形状、尺寸以及不同工艺层的相对位置的过程。其设计目标有以下三方面: ① 满足电路功能、性能指标、质量要求; ② 尽可能节省面积,以提高集成度,降低成本; ③ 尽可能缩短连线,以减少复杂度,缩短延时,改善可能性。 2、版图设计的内容: ①布局:安排各个晶体管、基本单元、复杂单元在芯片上的位置。 ②布线:设计走线,实现管间、门间、单元间的互连。 ③尺寸确定:确定晶体管尺寸(W、L)、互连尺寸(连线宽度)以及晶体管与互连之间的相对尺寸等。 ④版图编辑(Layout Editor ):规定各个工艺层上图形的形状、尺寸和位置。 ⑤布局布线(Place and route ):给出版图的整体规划和各图形间的连接。 ⑥版图检查(Layout Check ):设计规则检验(DRC,Design Rule Check)、电气规则检查(ERC,Electrical Rule Check)、版图与电路图一致性检验(LVS,Layout Versus Schematic )。 三.设计规则(Design Rul e ): 设计规则是设计人员与工艺人员之间的接口与“协议”,版图设计必须无条件的服从的准则,可以极大地避免由于短路、断路造成的电路失效和容差以及寄生效应引起的性能劣化。设计规则主要包括几何规则、电学规则以及走线规则。其中几何设计规则通常有两类: ①微米准则:用微米表示版图规则中诸如最小特征尺寸和最小允许间隔的绝对尺寸。 ②λ准则:用单一参数λ表示版图规则,所有的几何尺寸都与λ成线性比例。 设计规则分类如下: 1.拓扑设计规则(绝对值):最小宽度、最小间距、最短露头、离周边最短距离。 2.λ设计规则(相对值):最小宽度w=mλ、最小间距s=nλ、最短露头t=lλ、离周边最短距离d=hλ(λ由IC制造厂提供,与具体的工艺类型有关,m、n、l、h为比例因子,与图形类形有关)。 ①宽度规则(width rule):宽度指封闭几何图形的内边之间的距离。 ②间距规则(Separation rule):间距指各几何图形外边界之间的距离。 集成电路设计综合实验报告 班级:微电子学1201班 姓名: 学号: 日期:2016年元月13日 一.实验目的 1、培养从版图提取电路的能力 2、学习版图设计的方法和技巧 3、复习和巩固基本的数字单元电路设计 4、学习并掌握集成电路设计流程 二.实验内容 1. 反向提取给定电路模块(如下图所示),要求画出电路原理图,分析出其所完成的逻 辑功能,并进行仿真验证;再画出该电路的版图,完成DRC验证。 2. 设计一个CMOS结构的二选一选择器。 (1)根据二选一选择器功能,分析其逻辑关系。 (2)根据其逻辑关系,构建CMOS结构的电路图。 (3)利用EDA工具画出其相应版图。 (4)利用几何设计规则文件进行在线DRC验证并修改版图。 三.实验原理 1. 反向提取给定电路模块 方法一:直接将版图整体提取(如下图)。其缺点:过程繁杂,所提取的电路不够直观, 不易很快分析出其电路原理及实现功能。 直接提取的整体电路结构图 方法二:将版图作模块化提取,所提取的各个模块再生成symbol,最后将symbol按版图连接方式组合成完整电路结构(如下图)。其优点:使电路结构更简洁 直观、结构严谨、层次清晰,更易于分析其原理及所实现的功能。 CMOS反相器模块CMOS反相器的symbol CMOS传输门模块 CMOS传输门的symbol CMOS三态门模块 CMOS三态门的symbol CMOS与非门模块 CMOS与非门的symbol 各模块symbol按版图连接方式组合而成的整体电路 经分析可知,其为一个带使能端的D锁存器,逻辑功能如下: ①当A=1,CP=0时,Q=D,Q—=; ②当A=1,CP=1时,Q、Q—保持; 《集成电路版图设计》 学院:_____________ 专业班级:_____________ 学号:_____________ 学生姓名:_____________ 指导教师:_____________ 摘要 什么是集成电路?把组成电路的元件、器件以及相互间的连线放在单个芯片上,整个电路就在这个芯片上,把这个芯片放到管壳中进行封装,电路与外部的连接靠引脚完成。 什么是集成电路设计?根据电路功能和性能的要求,在正确选择系统配置、电路形式、器件结构、工艺方案和设计规则的情况下,尽量减小芯片面积,降低设计成本,缩短设计周期,以保证全局优化,设计出满足要求的集成电路。 《集成电路版图设计》基于Cadence软件的集成电路版图设计原理、编辑和验证的方法。本次实验是基于Cadence版图设计软件平台,采用L50C7工艺库,设计一个运算放大器,并且,为了防止电路中各元件间产生闩锁效应,在实际生产流片中每个元件都应该添加保护环,以防止各元件间电流之间产生各种影响。并且增加电路的稳定性和可靠性。 电路的验证采用的是Calibre验证工具,对电路版图进行了DRC验证和LVS验证。 关键词:Calibre,运算放大器 目录 一、电路设计流程 (1) 二、版图的制作流程 (2) 三、二级运算放大器的原理图 (3) 四、器件尺寸的计算 (4) 五、二级运算放大器原理图 (5) 六、二级运算放大器版图 (9) 心得体会 (11) 参考文献 (12) 一、电路设计流程 二、版图的制作流程 由于设计目标已经电路的构造课本已经讲述的十分详细。 所以我讲接着阐述版图的制作过程。首先将电路图转为相应的版图, 意思就是把相对 应的器件进行布局布线。因制造工艺精度有限,所以版图必须满足一定的规则要求。 按照设计规则布局布线后,接着就要对它进行检查。由于版图是人工布局布线,因此 或多或少的存在一些错误。这时就需要软件来进行“设计规则检查”(DRC )。软件所依 据的是DRC 文件,它与画版图时使用的规则是一致的,只不过规则文件是给版图设计 者参考使用的,而DRC 文件是由软件编写的。 当版图没有了DRC 错误,完全符合设计规则之后,再依靠LVS 文件,将其与电路原理 图进行比较。若有不同之处,LVS 将进行报错,经过修改之后还要重复DRC 、LVS 过程。 若两者相同,说版图与原理图一致。到这一步就完成了版图的制作了。完成版图之后, 还可以利用工具提取版图中的寄生参数,对包含这些寄生参数的电路再次进行仿真, 从而更准确确定电路的性能。 最后把图形格式的版图文件转换为通用二进制文件(GDS 文件),提交给生产厂制造。 射频芯片测试简介 射频/无线芯片相信各位射频工程师们都用的挺多的了,本文会介绍几种基本测试供大家参考,如果有写得不对的地方还请大家批评指正!射频/无线系统会同时包含一个发射器和接收器分别用于发送和接收信号。我们先介绍发射器的测试基础,接下来再介绍接收器的测试基础。 发射器测试基础 如图1所示,数字通信系统发射器由以下几个部分构成: CODEC(编码/解码器) 符号编码 基带滤波器(FIR) IQ调制 上变频器(Upconverter) 功率放大器 CODEC使用数字信号处理方法(DSP)来编码声音信号,以进行数据压缩。它还完成其它一些功能,包括卷积编码和交织编码。卷积编码复制每个输入位,用这些冗余位来进行错误校验并增加了编码增益。交织编码能让码位错误分布比较均匀,从而使得错误校验的效率更高。符号编码把数据和信息转化为I/Q信号,并把符号定义成某个特定的调制格式。基带滤波和调制整形滤波器通过修整I/Q调制信号的陡峭边沿来提高带宽的使用效率。 IQ调制器使得I/Q信号相互正交(积分意义上),因此它们之间不会相互干扰。IQ调制器的输出为是IQ信号的组合,就是一个单一的中频信号。该中频信号经过上变频器转换为射频信号后,再通过放大后进行发射。 图1、通用数字通信系统发射器的简单模块图 先进的数字信号处理和专用应用芯片技术提高了数字系统的集成度。现在一块单一的芯片就集成了从ADC转换到中频调制输出的大部分功能。因此,模块级和芯片级的射频测试点会减少很多,发射器系统级和天线端的测试和故障分析就变得更加重要。 发射器的主要测试内容 信道内测试 信道内测试采用时分复用或者码分复用的方法来测试无线数字电路。复用指的是频率或者空间上的复用等。在时分多址(TDMA)技术中,一个信道可以定义为在一系列重复出现的帧里面特定的频段和时隙,而在码分多址(CDMA)技术中,信道定义为特定的码段和频段。信道内和信道外这两个术语指的是我们所感兴趣的频段(频率信道),而不是指频率带宽内信道的时隙或者码段。 发射器信道带宽是最先进行的测试,它决定了发射器发射信号的频谱特性。通过频谱的形状和特性可以发现设计上的许多错误,并能大概推算出系统符号速率的错误率。 载波频率测试用于测试可能引起相邻频段信道干扰或影响接收器载波恢复的频率误差。在大多数调制方式中,载波频率应处于频谱的中心。可以通过计算3dB带宽来判断中心频率。 信道功率测试用于测试有用信号在频率带宽内的平均能量。它通常定义为有用信号能量在信号频率带宽内的平均值,实际的测量方法随着不同的标准会有所不同。无线系统必须保证每个环节消耗的能量最少,这样的目的主要有两个:一是可以减少系统的整体干扰,二是能延长便携系统电池的使用寿命。因此,必须严格地控制输出功率。在CDMA系统中,为了达到最大的容量,系统总的干扰容限也严格限制了每个单个移动单元的功率。精确发射功率控制对系统的容量,覆盖范围和信号质量至关重要。 占用带宽跟信道功率密切相关,定义为给定总调制信号功率的百分比所覆盖多少频谱。 时间测试常用于TDMA系统中的突发信号测试。这些测试主要用来评估载波包络是否能满足预期的要求,它们包括了突发信号宽度,上升时间,下降时间、开启时间、关闭时间、峰值功率、发射功率、关闭功率以及占空比等。时间测试可以保证相邻频率信道之间的干扰以及信号开启或者关闭的时隙切换时的干扰最小。 调制品质的测试通常涉及到发射信号的精确解调并与理想的数学计算出来的发射信号或参考信号进行比较。实际的测量随着不同的调制方式和不同的标准会有不同的方法。 误差矢量幅度(EVM)是应用最广泛的数字通信系统调制品质参数,它采样发射器的输出端的输出信号,获得实际信号的轨迹。通常把输出信号解调后得到一个参考信号。矢量误差是指某个时间理想的参考信号与实际所测的信号的差别,是一个包含幅度分量和相位分量的复数。通常,EVM会采用最大的符号幅度分量或者平均符号功率的平方根。 I/Q偏置(固有偏置origin offsets)是由I/Q信号的直流偏置引起的,可能会导致载波反基于无线通信射频收发机系统的设计毕业设计

射频接收系统的设计与仿真

集成电路版图设计论文

915MHz射频收发系统的ADS设计与仿真

无线通信射频收发系统设计研究

集成电路版图设计笔试面试大全

RFID相关射频芯片基本介绍与应用

linux驱动程序的编写

集成电路版图设计报告

基于无线通信射频收发机系统的设计

基于RF收发器Si4432A的无线射频收发系统设计

Linux驱动框架及驱动加载

集成电路版图设计报告

集成电路版图设计(反向提取与正向设计)

集成电路版图设计

射频芯片测试简介

- 基于S3C2410A_D转换Linux驱动程序设计_饶少锋

- linux驱动程序进入内核

- 设备驱动程序设计与实现

- Linux设备驱动程序设计完全教程

- Linux设备驱动编程模型(基本编)

- LINUX设备驱动程序(4)

- 基于Linux系统的HHARM9电机驱动程序设计

- Linux驱动试题

- 第四章 Linux驱动程序设计.ppt

- Linux平台下IPMI驱动程序设计与实现

- 6-1 Linux驱动程序

- linux驱动

- 基于ARMLinux平台的CAN设备驱动程序设计与实现

- linux驱动程序的编写

- Linux驱动程序设计.ppt

- Linux驱动程序设计

- Linux驱动框架及驱动加载

- 编写嵌入式Linux设备驱动程序的实例教程