微电子器件复习题

PN结:

1.突变PN结低掺杂侧的掺杂浓度越高,则势垒区的长度就越小,内建电场的最大值越大,内建电势V bi就越大,反向饱和电流I0就越小,势垒电容C T就越大,雪崩击穿电压就越小。P27

2.在PN结的空间电荷区中,P区一侧带负电荷,N区一侧带正电荷。内建电场的方向是从N 区指向P区。3.当采用耗尽近似时,N型耗尽区中的泊松方程为。由此方程可以看出,掺杂浓度越高,则内建电场的斜率越大。

6.当对PN结外加正向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度大;当对PN结外加反向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度小。

7.PN结的正向电流很大,是因为正向电流的电荷来源是多子;PN结的反向电流很小,是因为反向电流的电荷来源是少子。8.PN结的正向电流由空穴扩散电流电流、电子扩散电流电流和势垒区复和电流电流三部分所组成。

9.PN结的直流电流电压方程的分布为。

10.薄基区二极管是指PN结的某一个或两个中性区的长度小于该区的少子扩散长度。在薄基区二极管中,少子浓度的分布近似为线性;薄基区二极管相对厚基区二极管来说,其它参数都相同,则PN结电流会大的多。

11.小注入条件是指注入某区边界附近的非平衡少子浓度远小于该区的平衡多子浓度。

12.大注入条件是指注入某区边界附近的非平衡少子浓度远大于该区的平衡多子浓度。

13.势垒电容反映的是PN结的微分电荷随外加电压的变化率。PN结的掺杂浓度越高,则势垒电容就越大;外加反向电压越高,则势垒电容就越小。

14.扩散电容的物理含义为中性区中非平衡载流子随外加电压的变化率;外加正向电压越高,则势垒电容就越大。

15.雪崩击穿和齐纳击穿的条件分别是和。

16.在PN结开关管中,在外加电压从正向变为反向后的一段时间内,会出现一个较大的反向电流。引起这个电流的原因是存储在N 区中的非平衡载流子电荷。这个电荷的消失途径有两条,即和。

1.简述PN结耗尽区(空间电荷区)的形成机制。P9

答:P 区与N区接触后,由于存在浓度差的原因,结面附近的空穴将从浓度高的P区向浓度低的N区扩散,在P区留下不易扩散的带负电的电离受主杂质,结果使得在结面的P区一侧出现负的空间电荷;同样地,结面附近的电子从浓度高的N区向浓度低的P区扩散,在N区留下带正电的电离施主杂质,使结面的N区一侧出现正的空间电荷。

2.简要叙述PN结势垒电容和扩散电容的形成机理及特点。P56,P64

PN结的扩散电容是因为外加电压的变化,结的界面两边少数载流子的积累或抽取形成的。

势垒电容是由于结两边空间电荷区宽度随外加电压的变化而变化形成的。

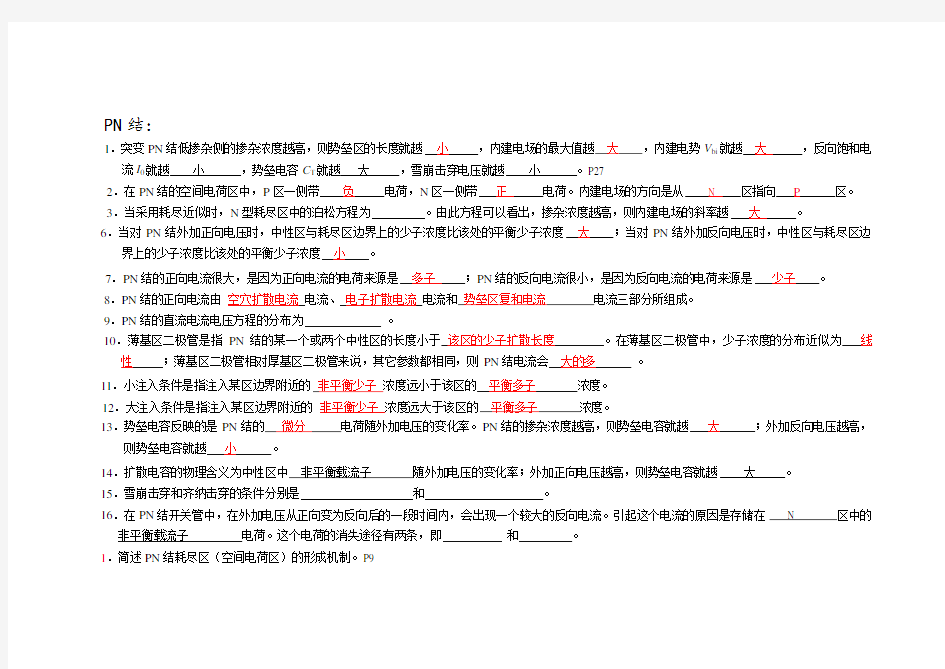

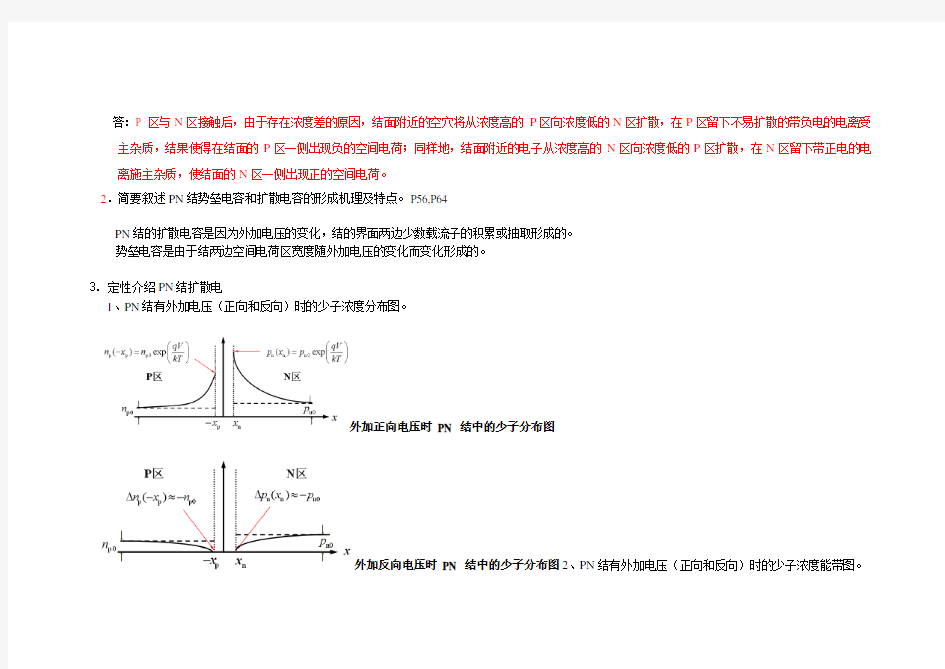

3.定性介绍PN结扩散电

1、PN结有外加电压(正向和反向)时的少子浓度分布图。

外加正向电压时PN 结中的少子分布图

外加反向电压时PN 结中的少子分布图2、PN结有外加电压(正向和反向)时的少子浓度能带图。

双极晶体管:

17.晶体管的饱和状态是指发射结 正偏 ,集电结 正偏 。

18.晶体管的共基极直流短路电流放大系数α是指发射结正偏、 集电 结零偏时的集电极电流与 发射 极电流之比。

19.晶体管的共发射极直流短路电流放大系数β是指发射结正偏、 集电 结零偏时的集电极电流与 基 极电流之比。

20.晶体管的注入效率是指 从发射区注入基区的少子电流

I pE 电流与 总的发射极电流I E 电流之比。为了提高注入效率,应当使 发射 区掺杂浓度远大于 基 区掺杂浓度。

21.晶体管的基区输运系数是指 基区中到达集电极结的少子电流I pC 电流与 从发射结刚注入基区的少子电流I pE 电流之比。

为了提高基区输运系数,应当使 基区宽度W B 远小于其扩散长度。

22.晶体管中的少子在渡越 基区 的过程中会发生 复合 ,从而使到达集电结的少子比从发射结注入基区的少子 小 。

23.I CS 是指 基极和发射极 结短路、 集电 结反偏时的集电极电流。

24.I ES 是指 基极和集电极 结短路、 发射 结反偏时的发射极电流。

25.发射区重掺杂效应是指当发射区掺杂浓度太高时,不但不能提高 注入效率 ,反而会使其 下降 。造成发射区重掺杂效应的原因是 发射区禁带变窄 和 俄歇复合增强 。P99

26.若用同γ和异γ分别代表同质结晶体管和异质结晶体管的注入效率,则同γ < 异γ;常用的HBT 用SiGe 制作 基 区,用Si 制作 发射

区。P101

27.设半导体材料的方块电阻为100Ω,长度和宽度分别为160μm 和40μm ,则沿长度方向上的电阻为 ,沿宽度方向上的电阻为 。

28.当集电结反偏增加时,集电结耗尽区宽度会 增宽 基区宽度 变窄 ,从而使集电极电流 增大 ,这就是基区宽度调变效应(即厄尔利效应)。

29.当ωβ降到1时的频率称为 特征频率f T 。当p max K 降到1时的频率称为 最高振荡频率f M 。

30. f T 代表的是共发射极揭发的晶体管有电流放大能力的频率极限, f M 代表晶体管有功率放大能力的频率极限。

4.共基极放大区晶体管的电流输运过程。

5.什么是双极型晶体管的基区宽度调变效应(厄尔利效应)?如何抑制该效应?P107

答:当V CE增大时,集电结反偏(V BC = V BE–V CE ) 增大,集电结耗尽区增宽,使中性基区的宽度变窄,基区少子浓度分布的梯度增大,从而使I C 增大。这种现象称为基区宽度调变效应,也称为厄尔利效应。

6.写出晶体管的特征频率f T的表达式,说明改善晶体管频率特性的主要措施。

3、分别画出均匀基区NPN晶体管在放大状态、饱和状态和截止状态时的能带图。

4、分别画出均匀基区NPN晶体管在放大状态、饱和状态和截止状态时的少子分布图。

Mos 晶体管:

31.N 沟道MOSFET 的衬底是 P 型半导体,源区和漏区是 N+ 型半导体,沟道中的载流子是 电子 P297

32.P 沟道MOSFET 的衬底是 N 型半导体,源区和漏区是 P+ 型半导体,沟道中的载流子是 空穴 。P297

33.由于电子的迁移率n μ比空穴的迁移率p μ 大 ,所以在其它条件相同时, N 沟道MOSFET 的Dsat I 比 P 沟道MOSFET 的大。为了使两种MOSFET 的Dsat I 相同,应当使N 沟道MOSFET 的沟道宽度 < P 沟道MOSFET 的。

34.由于栅氧化层中通常带 正 电荷,所以 P 型区比 N 型区更容易发生反型。

35.要提高N 沟道MOSFET 的阈电压V T ,应使衬底掺杂浓度N A 增大 。P303

36.要提高N 沟道MOSFET 的阈电压V T ,应使栅氧厚度 增大 。P303

37.在实际的工艺生产中,通常采用 改变衬底杂质浓度 和 改变栅氧化层 来调节阈值电压。P305

38.对于一般的MOSFET ,当沟道长度加倍,而其它尺寸、掺杂浓度、偏置条件等都不变时,其下列参数发生什么变化:Dsat I 减小 、on R 增加 、m g 减小 、T f 。

39.在P 沟道MOSFET 中,V T < 0的称为 增强 型;V T > 0的称为 耗尽 型。P297

40.为了提高MOSFET 的跨导,从器件制造角度,应提高 β,即 提高

Z L , 提高 迁移率 μ , 减小 栅氧化层的厚度 T OX 。从电路使用角度,应 提高 V GS 。P324

7.什么是MOSFET 的阈电压V T ?写出V T 的表达式,写出影响V T 的因素。(以N 沟道MOSFET 为例)

8.什么是有效沟道长度调制效应?如何抑制有效沟道长度调制效应?

9.什么是MOSFET 的跨导g m ?写出g m 的表达式,并讨论提高g m 的措施。

微电子器件_刘刚前三章课后答案

课后习题答案 1.1 为什么经典物理无法准确描述电子的状态?在量子力学 中又是用什么方法来描述的? 解:在经典物理中,粒子和波是被区分的。然而,电子和光子是微观粒子,具有波粒二象性。因此,经典物理无法准确描述电子的状态。 在量子力学中,粒子具有波粒二象性,其能量和动量是通过这样一个常数来与物质波的频率ω和波矢建立联系的,即 c h p h E ====υω υ 上述等式的左边描述的是粒子的能量和动量,右边描述的则是粒子波动性的频率ω和波矢。 1.2 量子力学中用什么来描述波函数的时空变化规律? 解:波函数ψ是空间和时间的复函数。与经典物理不同的是,它描述的不是实在的物理量的波动,而是粒子在空间的概率分布,是一种几率波。如果用()t r ,ψ表示粒子的德布洛意波的振幅,以()()()t r t r t r ,,,2 ψψψ*=表示波的强度,那么,t 时刻在r 附近的小体积元z y x ???中检测到粒子的概率正比于()z y x t r ???2,ψ。

1.3 试从能带的角度说明导体、半导体和绝缘体在导电性能上的差异。 解:如图1.3所示,从能带的观点 来看,半导体和绝缘体都存在着禁 带,绝缘体因其禁带宽度较大 (6~7eV),室温下本征激发的载流子 近乎为零,所以绝缘体室温下不能 导电。半导体禁带宽度较小,只有1~2eV ,室温下已经有一定数量的电子从价带激发到导带。所以半导体在室温下就有一定的导电能力。而导体没有禁带,导带与价带重迭在一起,或者存在半满带,因此室温下导体就具有良好的导电能力。 1.4 为什么说本征载流子浓度与温度有关? 解:本征半导体中所有载流子都来源于价带电子的本征激发。由此产生的载流子称为本征载流子。本征激发过程中电子和空穴是同时出现的,数量相等,i n p n ==00。对于某一确定的半导体材料,其本征载流子浓度为kT E V C i g e N N p n n ==002 式中,N C ,N V 以及Eg 都是随着温度变化的,所以,本征载流子浓度也是随着温度变化的。 1.5 什么是施主杂质能级?什么是受主杂质能级?它们有何异同?

832微电子器件-电子科技大学2015硕士入学考试真题

电子科技大学 2015年攻读硕士学位研究生入学考试试题电子科技大学2016年硕士研究生入学考试初试自命题科目及代码汇总 ?111单独考试政治理论 ?241法语(二外) ?242德语(二外) ?243日语(二外) ?244英语(二外仅日语方向) ?288单独考试英语 ?601数学分析 ?602高等数学 ?613分子生物学 ?615日语水平测试 ?616公共管理综合 ?621英语水平测试 ?622心理学综合 ?623新闻传播理论 ?625宪法学 ?688单独考试高等数学 ?689西方行政史 ?690中国近现代史 ?691政治学原理 ?692数学物理基础?694生物学综合 ?694生物学综合 ?695口腔综合 ?804行政法与行政诉讼法学 ?805新闻传播实务 ?806行政管理综合 ?808金融学基础 ?809管理学原理 ?811大学物理 ?812地理信息系统基础 ?813电磁场与电磁波 ?814电力电子技术 ?815电路分析基础 ?818固体物理 ?820计算机专业基础 ?821经济学基础 ?824理论力学 ?825密码学基础与网络安全 ?830数字图像处理 ?831通信与信号系统 ?832微电子器件 ?834物理化学 ?835线性代数 ?836信号与系统和数字电路 ?839自动控制原理 ?840物理光学 ?845英美文学基础知识及运用 ?846英语语言学基础知识及运用 ?847日语专业基础知识及应用 ?852近代物理基础 ?853细胞生物学 ?854国际政治学 ?855辩证唯物主义和历史唯物主 义 ?856测控通信原理 ?857概率论与数理统计 ?858信号与系统 ?859测控通信基础 ?860软件工程学科基础综合

微电子器件__刘刚前三章课后答案(DOC)

课后习题答案 1.1 为什么经典物理无法准确描述电子的状态?在量子力学 中又是用什么方法来描述的? 解:在经典物理中,粒子和波是被区分的。然而,电子和光子是微观粒子,具有波粒二象性。因此,经典物理无法准确描述电子的状态。 在量子力学中,粒子具有波粒二象性,其能量和动量是通过这样一个常数来与物质波的频率ω和波矢k 建立联系的,即 k n c h p h E ====υ ω υ 上述等式的左边描述的是粒子的能量和动量,右边描述的则是粒子波动性的频率ω和波矢k 。 1.2 量子力学中用什么来描述波函数的时空变化规律? 解:波函数ψ是空间和时间的复函数。与经典物理不同的是,它描述的不是实在的物理量的波动,而是粒子在空间的概率分布,是一种几率波。如果用()t r ,ψ表示粒子的德布洛意波的振幅,以 ()()()t r t r t r ,,,2 ψψψ*=表示波的强度,那么,t 时刻在r 附近的小体 积元z y x ???中检测到粒子的概率正比于()z y x t r ???2,ψ。

1.3 试从能带的角度说明导体、半导体和绝缘体在导电性能上的差异。 解:如图1.3所示,从能带的观点来看,半导体和绝缘体都存在着禁带,绝缘体因其禁带宽度较大(6~7eV),室温下本征激发的载流子近乎为零,所以绝缘体室温下不 能导电。半导体禁带宽度较小,只有1~2eV ,室温下已经有一定数量的电子从价带激发到导带。所以半导体在室温下就有一定的导电能力。而导体没有禁带,导带与价带重迭在一起,或者存在半满带,因此室温下导体就具有良好的导电能力。 1.4 为什么说本征载流子浓度与温度有关? 解:本征半导体中所有载流子都来源于价带电子的本征激发。由此产生的载流子称为本征载流子。本征激发过程中电子和空穴是同时出现的,数量相等,i n p n ==00。对于某一确定的半导体材料,其本征载流子浓度为kT E V C i g e N N p n n ==002 式中,N C ,N V 以及Eg 都是随着温度变化的,所以,本征载流子浓度也是随着温度变化的。 1.5 什么是施主杂质能级?什么是受主杂质能级?它们有何异同?

微电子工艺习题总结(DOC)

1. What is a wafer? What is a substrate? What is a die? 什么是硅片,什么是衬底,什么是芯片 答:硅片是指由单晶硅切成的薄片;芯片也称为管芯(单数和复数芯片或集成电路);硅圆片通常称为衬底。 2. List the three major trends associated with improvement in microchip fabrication technology, and give a short description of each trend. 列出提高微芯片制造技术相关的三个重要趋势,简要描述每个趋势 答:提高芯片性能:器件做得越小,在芯片上放置得越紧密,芯片的速度就会提高。 提高芯片可靠性:芯片可靠性致力于趋于芯片寿命的功能的能力。为提高器件的可靠性,不间断地分析制造工艺。 降低芯片成本:半导体微芯片的价格一直持续下降。 3. What is the chip critical dimension (CD)? Why is this dimension important? 什么是芯片的关键尺寸,这种尺寸为何重要 答:芯片的关键尺寸(CD)是指硅片上的最小特征尺寸; 因为我们将CD作为定义制造复杂性水平的标准,也就是如果你拥有在硅片某种CD的能力,那你就能加工其他所有特征尺寸,由于这些尺寸更大,因此更容易产生。 4. Describe scaling and its importance in chip design. 描述按比例缩小以及在芯片设计中的重要性 答:按比例缩小:芯片上的器件尺寸相应缩小是按比例进行的 重要性:为了优电学性能,多有尺寸必须同时减小或按比例缩小。 5. What is Moore's law and what does it predict? 什么是摩尔定律,它预测了什么 答:摩尔定律:当价格不变时,集成电路上可容纳的晶体管数,月每隔18个月便会增加1倍,性能也将提升1倍。 预言在一块芯片上的晶体管数大约每隔一年翻一番。 第二章 6. What is the advantage of gallium arsenide over silicon? 砷化镓相对于硅的优点是什么 答:优点:具有比硅更高的电子迁移率;减小寄生电容和信号损耗的特性;集成电路的速度比硅电路更快;材料的电阻率更大。 7. What is the primary disadvantage of gallium arsenide over silicon? 砷化镓相对于硅的主要缺点是什么 答:主要缺点:缺乏天然氧化物;材料的脆性;成本比硅高10倍;有剧毒性在设备,工艺和废物清除设施中特别控制。

微电子器件与IC设计基础第二版第1章习题

第一章 思考题: 1.1简单解释原子能级和晶体能带之间的联系和区别。 答:在孤立原子中,原子核外面的电子受到这个原子核所带正电荷的作用,按其能量的大小分布在不同的电子轨道上绕核运转。 原子中不同轨道上电子能量的大小 用彼此有一定间隔的横线段组成的 能级图来表示(见图1.1b)。能级的 位置越高,表示该能级上电子的能量 就越大。原子结合成晶体后,一个原 子核外的电子除了受到这个原子核 所带正电荷以及核外电子所带负电 荷的作用以外,还要受到这个原子周 围其它原子所带正负电荷的作用。也 就是说,晶体中的电子是在原子核的 正电荷形成的周期性势场中作如图 1.1(a)中箭头所示的共有化运动。 正因为如此,原来描述孤立原子中电 子能量大小的能级就被分裂成为一 系列彼此相距很近的准连续的能级, 其形状好似一条条反映电子能量大小的带子,故称之为能带,见图1.1(b)。 1.2以硅为例,解释什么是施主杂质和施主能级?什么是受主杂质和受主能级? 答:以硅为例,见图1.2(a), 如果在单晶硅中掺入Ⅴ族元素 的杂质磷(P+),磷原子()P将 取代Ⅳ族的硅(Si)原子的位置 而成为所谓的施主杂质。因为 磷原子外层有五个价电子,它 和周围的四个硅原子形成共价 键后还多出一个电子,这个多 余的电子受到磷原子核的微弱 束缚力而绕着该原子核做一定 半径的圆周运动,它只需要吸 收很小的能量(百分之几个电 子伏特)就能挣脱磷原子核的 束缚而成为可以在整个晶体中 运动的准自由电子,原来的磷 原子则成为了磷离子()+P,称 之为正电中心。从电子能量大小的观点来看,导带底能量E C表示导带中速度为零的电子所

微电子器件基础题13页word文档

“微电子器件”课程复习题 一、填空题 1、若某突变PN 结的P 型区的掺杂浓度为163 A 1.510cm N -=?,则室温下该区的平衡多子浓度p p0与平衡少子浓度n p0分别为( )和( )。 2、在PN 结的空间电荷区中,P 区一侧带(负)电荷,N 区一侧带(正)电荷。内建电场的方向是从(N )区指向(P )区。 3、当采用耗尽近似时,N 型耗尽区中的泊松方程为( )。由此方程可以看出,掺杂浓度越高,则内建电场的斜率越( )。 4、PN 结的掺杂浓度越高,则势垒区的长度就越(短),内建电场的最大值就越(大),内建电势V bi 就越(大),反向饱和电流I 0就越(小),势垒 电容C T 就越( ),雪崩击穿电压就越(低)。 5、硅突变结内建电势V bi 可表为( ),在室温下的典型值为 (0.8)伏特。 6、当对PN 结外加正向电压时,其势垒区宽度会(减小),势垒区的势垒 高度会(降低)。 7、当对PN 结外加反向电压时,其势垒区宽度会(变宽),势垒区的势垒 高度会(增高)。 8、在P 型中性区与耗尽区的边界上,少子浓度n p 与外加电压V 之间的关 系可表示为( )。若P 型区的掺杂浓度173A 1.510cm N -=?,外加电压V = 0.52V ,则P 型区与耗尽区边界上的少子浓度n p 为( )。 9、当对PN 结外加正向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度(高);当对PN 结外加反向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度(低)。 10、PN 结的正向电流由(空穴扩散Jdp )电流、(电子扩散电流Jdn )电流和(势垒区复合电流Jr )电流三部分所组成。 11、PN 结的正向电流很大,是因为正向电流的电荷来源是(多子);PN 结的反向电流很小,是因为反向电流的电荷来源是(少子)。 12、当对PN 结外加正向电压时,由N 区注入P 区的非平衡电子一边向前扩散,一边(复合)。每经过一个扩散长度的距离,非平衡电子浓度降到原来的( )。 13、PN 结扩散电流的表达式为( )。这个表达式在正 向电压下可简化为( ),在反向电压下可简化为( )。 14、在PN 结的正向电流中,当电压较低时,以(复合)电流为主;当电 压较高时,以(扩散)电流为主。 15、薄基区二极管是指PN 结的某一个或两个中性区的长度小于(少子扩 散长度)。在薄基区二极管中,少子浓度的分布近似为(线性)。

832微电子器件考试大纲详细

考试科目832微电子器件考试形式笔试(闭卷) 考试时间180分钟考试总分150分 一、总体要求 主要考察学生掌握“微电子器件”的基本知识、基本理论的情况,以及用这些基本知识和基本理论分析问题和解决问题的能力。 二、内容 1.半导体器件基本方程 1)半导体器件基本方程的物理意义 2)一维形式的半导体器件基本方程 3)基本方程的主要简化形式 2.PN结 1)突变结与线性缓变结的定义 2)PN结空间电荷区的形成

4)耗尽区宽度、内建电场与内建电势的计算5)正向及反向电压下PN结中的载流子运动情况6)PN结的能带图 7)PN结的少子分布图 8) PN结的直流伏安特性 9)PN结反向饱和电流的计算及影响因素 10)薄基区二极管的特点

11)大注入效应 12)PN结雪崩击穿的机理、雪崩击穿电压的计算及影响因素、齐纳击穿的机理及特点、热击穿的机理13)PN结势垒电容与扩散电容的定义、计算与特点 14)PN结的交流小信号参数与等效电路 15)PN结的开关特性与少子存储效应

2)基区输运系数与发射结注入效率的定义及计算 3)共基极与共发射极直流电流放大系数的定义及计算 4)基区渡越时间的概念及计算 5)缓变基区晶体管的特点 6)小电流时电流放大系数的下降 7)发射区重掺杂效应 8)晶体管的直流电流电压方程、晶体管的直流输出特性曲线图

9)基区宽度调变效应 10)晶体管各种反向电流的定义与测量 11)晶体管各种击穿电压的定义与测量、基区穿通效应12)方块电阻的概念及计算

13)晶体管的小信号参数 14)晶体管的电流放大系数与频率的关系、组成晶体管信号延迟时间的四个主要时间常数、高频晶体管特征频率的定义、计算与测量、影响特征频率的主要因素

微电子器件 课程基本要求

微电子器件 钟智勇 办公室:<微电子楼>217室 电话:83201440 E mail: zzy@https://www.wendangku.net/doc/dd5307320.html, -mail:zzy@uestc edu cn 8:00--10:00 周二晚上8:00 答疑时间:周二晚上 答疑时间:

教材与参考书 1、教材与参考书 教材: 教材 微电子器件(第3版),陈星弼,张庆中,2011年 参考书 参考书: 1.半导体器件基础,B.L.Anderson, R.L.Anderson, 清华大学出版社,2008年 2.半导体器件基础,Robert F. Pierret, 电子工业出版社,2004年 2半导体器件基础Robert F Pierret电子工业出版社 3.集成电路器件电子学(第三版),Richard S. Muller,电子工业出版社, 2004年 4.半导体器件物理与工艺(第二版),施敏,苏州大学出版社,2002年 5.半导体物理与器件(第三版),Donald A. Neamen, 清华大学出版社, 2003年 6. Physics of Semiconductor Devices( 3th Edition), S M Sze, Wiley- Interscience, 2007

2、学时、成绩构成与考核 总学时数:72学时 其中课堂讲授:60学时,实验:12 学时 成绩构成: 70分期中考试:分平时:10分实验:10 期末考试:70 分、期中考试:10分、平时:10 分、实验:10 分考试形式:闭卷考试

3、课程要求 1、网上只公布教材的标准课件与参阅资料,请做好笔记! 网址:网络学堂:http://222.197.183.243/wlxt/course.aspx?courseid=0311下载密码i 下载密码:micro 2、请带计算器与作业本上课! 请带计算器与作业本上课! 3、鼓励学生学习,以下情况加分(最高加分为5分): 鼓励学生学习以下情况加分(最高加分为 3.1 完成调研作业并在期末做presentation(ppt)者 3.2 在黑板上完成课堂练习者 3.3 指出教材错误及对教学/教材提出建设性意见者

√增强载流子迁移率是新一代微电子器件和电路发展的重要方向

增强载流子迁移率是新一代微电子器件和电路发展的重要方向 (作者:Xie Meng-xian,电子科技大学微固学院) (1)集成电路发展状况: 作为微电子技术的主体——集成电路,它的发展已经经历了若干个重要阶段,从小规模、中规模,到大规模、乃至超大规模、特大规模等。微电子技术的这种长足的进步,在很大程度上就是在不断努力地缩短场效应器件的沟道长度,这主要是通过改善微电子工艺技术、提高加工水平来实现的。尽管现在沟道长度已经可以缩短到深亚微米、乃至于纳米尺寸了,但是要想再继续不断缩短沟道长度的话,将会受到若干因素的限制,这一方面是由于加工工艺能力的问题,另一方面是由于器件物理效应(例如短沟道效应、DIBL效应、热电子等)的问题。因此,在进一步发展微电子技术过程中,再单只依靠缩短沟道长度就很不现实、甚至也可能了,则必须采用新的材料、开发新的工艺和构建新的器件结构,才能突破因缩短沟道所带来的这些限制。 实际上,从集成电路的发展趋势来看,大体上可以划分为三大阶段: ①K时代(Kbit,KHz):微细加工的时代(不断缩短有效尺寸)~“微米时代”; ②M时代(Mbit,MHz):结构革命的时代(不断改进器件和电路结构)~“亚微米时代”; ③G时代(Gbit,GHz):材料革命的时代(不断开发新材料、新技术)~“10纳米时代”。 现在已经开始进入G时代,因此,在不断开发新技术的同时,特别值得注意的是新材料的开发;不仅要开发新型的半导体材料(例如宽禁带半导体、窄禁带半导体、大极性半导体等),而且也要开发各种新型的辅助材料(例如高K、低K介质材料,Cu电极材料,新型表面钝化材料等)。器件和电路研究者应该多加注意新材料的开发应用;而新材料研究者应该多加注意往器件和电路的应用上下功夫。 在新的材料和工艺技术方面现在比较受到重视的是高介电常数(高K)材料和Cu互连技术。当沟道长度缩短到一定水平时,为了保持栅极的控制能力,就必须减小栅极氧化层厚度(一般,选取栅氧化层厚度约为沟道长度的1/50),而这在工艺实施上会遇到很大的困难(例如过薄的氧化层会出现针孔等缺陷);因此就采用了高介电常数的介质材料(高K材料)来代替栅极氧化物,以减轻制作极薄氧化层技术上的难度。另外,沟道长度缩短带来芯片面积的减小,这相应限制了金属连线的尺寸,将产生一定的引线电阻,这就会影响到器件和电路的频率、速度;因此就采用了电导率较高一些的Cu来代替Al作为连线材料,以进一步改善器件和电路的信号延迟性能。可见,实际上所有这些高K材料和Cu互连等新技术的采用都是不得已而为之的,并不是从半导体材料和器件结构本身来考虑的。 显然,为了适应器件和电路性能的提高,最好的办法是另辟途径,应该考虑如何进一步发挥半导体材料和器件结构的潜力,并从而采用其他更有效的技术措施来推动集成电路的发展。现在已经充分认识到的一种有效的技术措施就是着眼于半导体载流子迁移率的提高(迁移率增强技术)。 (2)迁移率增强技术: 迁移率(μ)是标志载流子在电场作用下运动快慢的一个重要物理量,它的大小直接影响到半导体器件和电路的工作频率与速度。 对于双极型晶体管而言,高的载流子迁移率可以缩短载流子渡越基区的时间,使特征频率(f T)提高,能够很好的改善器件的频率、速度和噪音等性能。 对于场效应晶体管而言,提高载流子迁移率则具有更加重要的意义。因为MOSFET的最大输出电流——饱和漏极电流I DS可表示为:

电子科技大学《微电子器件》课程教学大纲

电子科技大学 《微电子器件》课程教学大纲 课程编号:65030145适用专业:电子科学与技术 集成电路设计与集成系统 学时数:72(含实验12)学分数:4.5 先修课程:《半导体物理》 考核方式:考试 执笔者:张庆中编写日期:2006年4月 一、课程性质和任务 本课程的授课对象是“电子科学与技术(微电子技术方向)”专业和“集成电路设计与集成系统”专业的本科生,属于专业方向选修课。本课程的目的是使学生掌握二极管、双极型与场效应晶体管的基本理论,这些内容都是本领域高级专业技术人员所必须掌握的。本课程同时也是本专业其它后续课程如《集成电路原理》等的先修课程。 二、课程教学内容和要求 1、理论教学(60学时) 基本半导体方程(3学时): 掌握一维形式的泊松方程、电子与空穴的电流密度方程、电子与空穴的连续性方程,掌握基本半导体方程的主要简化形式。 PN结(18学时): 了解突变结与线性缓变结、PN结的平衡状态,理解空间电荷区的形成,了解耗尽近似的适用性(自学),掌握内建电场与扩散电势差、PN结在正向及反向电压下的能带图、少子分布与伏安特性,理解正向导通电压、大注入效应,掌握PN结的击穿特性、PN结的势垒电容与扩散电容、交流小信号参数与等效电路、PN结的开关特性。 这部分内容的重点是PN结空间电荷区的形成、耗尽层宽度与扩散电势差的推导与计算、PN结伏安特性的推导、势垒电容与扩散电容的概念及其计算、PN结的交流小信号参数与等效电路、少子存储效应、雪崩击穿的概念及击穿电压的计算。 这部分内容的难点是PN结内建电场的计算、少子分布的推导与少子分布图、大注入时的内建电场与Webster效应、扩散电容表达式的推导、雪崩倍增因子的推导等。 双极型晶体管(25学时): 了解均匀基区与缓变基区,理解晶体管的基区输运系数与发射结注入效率,掌握晶体管的直流电流放大系数,理解发射区重掺杂效应,

电子科技大学《微电子器件》课程重点与难点

重点与难点 第1章半导体器件基本方程 一般来说要从原始形式的半导体器件基本方程出发来求解析解是极其困难的,通常需要先对方程在一定的具体条件下采用某些假设来加以简化,然后再来求其近似解。随着半导体器件的尺寸不断缩小,建立新解析模型的工作也越来越困难,一些假设受到了更大的限制并变得更为复杂。简化的原则是既要使计算变得容易,又要能保证达到足够的精确度。如果把计算的容易度与精确度的乘积作为优值的话,那么从某种意义上来说,对半导体器件的分析问题,就是不断地寻找具有更高优值的简化方法。要向学生反复解释,任何方法都是近似的,关键是看其精确程度和难易程度。此外,有些近似方法在某些条件下能够采用,但在另外的条件下就不能采用,这会在后面的内容中具体体现出来。 第2章PN结 第2.1节PN结的平衡状态 本节的重点是PN结空间电荷区的形成、内建电势的推导与计算、耗尽区宽度的推导与计算。 本节的难点是对耗尽近似的理解。要向学生强调多子浓度与少子浓度相差极其巨大,从而有助于理解耗尽近似的概念,即所谓耗尽,是指“耗尽区”中的载流子浓度与平衡多子浓度或掺杂浓度相比可以忽略。

第2.2节PN结的直流电流电压方程 本节的重点是对PN结扩散电流的推导。讲课时应该先作定性介绍,让学生先在大脑中建立起物理图象,然后再作定量的数学推导。当PN结上无外加电压时,多子的扩散趋势正好被高度为qV bi的势垒所阻挡,电流为零。外加正向电压时,降低了的势垒无法阻止载流子的扩散,于是构成了流过PN结的正向电流。正向电流的电荷来源是P区空穴和N区电子,它们都是多子,所以正向电流很大。外加反向电压时,由于势垒增高,多子的扩散变得更困难。应当注意,“势垒增高”是对多子而言的,对各区的少子来说,情况恰好相反,它们遇到了更深的势阱,因此反而更容易被拉到对方区域去,从而构成流过PN结的反向电流。反向电流的电荷来源是少子,所以反向电流很小。 本节的难点是对有外加电压时势垒区两旁载流子的运动方式的理解、以及电子(空穴)电流向空穴(电子)电流的转化。 第2.3节准费米能级与大注入效应 本节的重点是PN结在外加正向电压和反向电压时的能带图、大注入条件及大注入条件下的PN结电流公式。 本节的难点是大注入条件下自建场的形成原因。要向学生说明,大注入自建场的推导与前面进行过的非均匀掺杂内建场的推导在本质上是相同的,都是令多子电流密度方程为零而解出电场,这也是分析微电子器件时的一种常用方法。 第2.4节PN结的击穿 本节的重点是利用雪崩击穿临界电场和通过查曲线来求得雪崩击穿电压的方法,以及PN结的实际结构(高阻区的厚度和结深)对击穿电压的影响,这些都是实际工程中的常见问题。

(完整word版)微电子器件与IC设计基础_第2版,刘刚,陈涛,课后答案.doc

课后习题答案 1.1 为什么经典物理无法准确描述电子的状态?在量子力学中又是用什么方法来描述的? 解:在经典物理中,粒子和波是被区分的。然而,电子和光子是微观粒子,具有波粒二象性。因此,经典物理无法准确描述电子的状态。 在量子力学中,粒子具有波粒二象性,其能量和动量是通过这样一个常数来与物质波的频率和波矢 k 建立联系的,即 E h h p n k c 上述等式的左边描述的是粒子的能量和动量,右边描述的则是粒子波动性的频率和波矢k。 1.2量子力学中用什么来描述波函数的时空变化规律? 解:波函数是空间和时间的复函数。与经典物理不同的是,它描述的不是实在的物理量 的波动,而是粒子在空间的概率分布,是一种几率波。如果用r , t 表示粒子的德布洛意 r ,t 2 r , t 表示波的强度,那么,t 时刻在 r 附近的小体积元 波的振幅,以r ,t x y z 中检测到粒子的概率正比于 2 r ,t x y z 。 1.3 试从能带的角度说明导体、半导体和绝缘体在导电性能上的差异。 解:如图 1.3 所示,从能带的观点来看,半导体和 绝缘体都存在着禁带,绝缘体因其禁带宽度较大 (6~7eV) ,室温下本征激发的载流子近乎为零,所 以绝缘体室温下不能导电。半导体禁带宽度较小, 只有1~2eV ,室温下已经有一定数量的电子从价 带激发到导带。所以半导体在室温下就有一定的 导电能力。而导体没有禁带,导带与价带重迭在 一起,或者存在半满带,因此室温下导体就具有 良好的导电能力。 1.4 为什么说本征载流子浓度与温度有关? 解:本征半导体中所有载流子都来源于价带电子的本征激发。由此产生的载流子称为本征载流子。本征激发过程中电子和空穴是同时出现的,数量相等,n0 p0 n i。对于某一确定 的半导体材料,其本征载流子浓度为 2 n0 p0 N C N V e E g kT n i 式中, N C,N V以及 Eg 都是随着温度变化的,所以,本征载流子浓度也是随着温度变化的。

最新微电子器件基础题

微电子器件基础题

“微电子器件”课程复习题 一、填空题 1、若某突变PN 结的P 型区的掺杂浓度为163A 1.510cm N -=?,则室温下该区的平衡多子浓度p p0与平衡少子浓度n p0分别为( )和( )。 2、在PN 结的空间电荷区中,P 区一侧带(负)电荷,N 区一侧带(正)电 荷。内建电场的方向是从(N )区指向(P )区。 3、当采用耗尽近似时,N 型耗尽区中的泊松方程为( )。由此方程可以看出,掺杂浓度越高,则内建电场的斜率越( )。 4、PN 结的掺杂浓度越高,则势垒区的长度就越(短),内建电场的最大值就 越(大),内建电势V bi 就越(大),反向饱和电流I 0就越(小),势垒电容C T 就越( ),雪崩击穿电压就越(低)。 5、硅突变结内建电势V bi 可表为( ),在室温下的典型值为(0.8)伏 特。 6、当对PN 结外加正向电压时,其势垒区宽度会(减小),势垒区的势垒高度 会(降低)。 7、当对PN 结外加反向电压时,其势垒区宽度会(变宽),势垒区的势垒高度 会(增高)。 8、在P 型中性区与耗尽区的边界上,少子浓度n p 与外加电压V 之间的关系可 表示为( )。若P 型区的掺杂浓度173 A 1.510cm N -=?,外加电压V = 0.52V ,则P 型区与耗尽区边界上的少子浓度n p 为( )。 9、当对PN 结外加正向电压时,中性区与耗尽区边界上的少子浓度比该处的平 衡少子浓度(高);当对PN 结外加反向电压时,中性区与耗尽区边界上的少子浓度比该处的平衡少子浓度(低)。 10、PN 结的正向电流由(空穴扩散Jdp )电流、(电子扩散电流Jdn )电流和 (势垒区复合电流Jr )电流三部分所组成。 11、PN 结的正向电流很大,是因为正向电流的电荷来源是(多子);PN 结的 反向电流很小,是因为反向电流的电荷来源是(少子)。 12、当对PN 结外加正向电压时,由N 区注入P 区的非平衡电子一边向前扩散,一边(复合)。每经过一个扩散长度的距离,非平衡电子浓度降到原来的( )。 13、PN 结扩散电流的表达式为( )。这个表达式在正向电压下可简 化为( ),在反向电压下可简化为( )。 14、在PN 结的正向电流中,当电压较低时,以(复合)电流为主;当电压较 高时,以(扩散)电流为主。 15、薄基区二极管是指PN 结的某一个或两个中性区的长度小于(少子扩散长 度)。在薄基区二极管中,少子浓度的分布近似为(线性)。 16、小注入条件是指注入某区边界附近的(非平衡少子)浓度远小于该区的 (平衡多子)浓度,因此该区总的多子浓度中的(非平衡)多子浓度可以忽略。 17、大注入条件是指注入某区边界附近的(非平衡少子)浓度远大于该区的 (平衡多子)浓度,因此该区总的多子浓度中的(平衡)多子浓度可以忽略。

微电子器件工艺

《微电子器件工艺》课程设计报告 班级:电子09-2 学号: 0906040206 姓名:高春旭 指导教师:白立春

N阱硅栅结构的CMOS集成电工艺设计 一.基本要求 设计如下电路的工艺流程 (1)设计上图所示电路的生产工艺流程: (2)每一具体步骤需要画出剖面图; (3)每一个步骤都要求说明,例如进行掺杂时,是采用扩散还是离子注入,需要 解释原因,又如刻蚀,采用的是干法刻蚀,还是湿法刻蚀,这类问题都须详细说明. (4)在设计时,要考虑隔离,衬底选择等问题. (5)要求不少于5页,字迹工整,画图清楚. 二、设计的具体实现 2.1 工艺概述 n阱工艺为了实现与LSI的主流工艺增强型/耗层型(E/D)的完全兼容,n 阱CMOS工艺得到了重视和发展。它采用E/D NMOS的相同的p型衬底材料制备NMOS器件,采用离子注入形成的n阱制备PMOS器件,采用沟道离子注入调整两种沟遭器件的阈值电压。 n阱CMOS工艺与p阱CMOS工艺相比有许多明显的优点。首先是与E/D NMOS工艺完全兼容,因此,可以直接利用已经高度发展的NMOS 工艺技术;其次是制备在轻掺杂衬底上的NMOS的性能得到了最佳化--保持了高的电子迁移率,低的体效应系数,低的n+结的寄生电容,降低了漏结势垒区的电场强度,从而降低了电子碰撞电离所产生的电流等。这个优点对动态CMOS电路,如时钟CMOS电路,多米诺电路等的性能改进尤其明显。

这是因为在这些动态电路中仅采用很少数目的PMOS器件,大多数器件是NMOS 型。另外由于电子迁移率较高,因而n阱的寄生电阻较低;碰撞电离的主要来源—电子碰撞电离所产生的衬底电流,在n阱CMOS中通过较低寄生电阻的衬底流走。而在p阱CMOS中通过p阱较高的横向电阻泄放,故产生的寄生衬底电压在n阱CMOS中比p阱要小。在n阱CMOS中寄生的纵向双极型晶体管是PNP型,其发射极电流增益较低,n阱CMOS结构中产生可控硅锁定效应的几率较p阱为低。由于n阱 CMOS的结构的工艺步骤较p阱CMOS简化,也有利于提高集成密度.例如由于磷在场氧化时,在n阱表面的分凝效应,就可以取消对PMOS的场注入和隔离环。杂质分凝的概念:杂质在固体-液体界面上的分凝作用 ~ 再结晶层中杂质的含量决定于固溶度→ 制造合金结(突变结);杂质在固体-固体界面上也存在分凝作用 ~ 例如,对Si/SiO2界面:硼的分凝系数约为3/10,磷的分凝系数约为10/1;这就是说,掺硼的Si经过热氧化以后, Si表面的硼浓度将减小,而掺磷的Si 经过热氧化以后, Si表面的磷浓度将增高)。 n阱CMOS基本结构中含有许多性能良好的功能器件,对于实现系统集成及接口电路也非常有利。图A (a)和(b)是p阱和n阱CMOS结构的示意图。 N阱硅栅CMOS IC的剖面图 N离子注入 2.2 现在COMS工艺多采用的双阱工艺制作步骤主要表现为以下几个步骤:

微电子工程学复习题

第一章: 1、电子器件微型化和大规模集成的含义是什么?其具有怎样的实际意义。 答:电子器件微型化主要是指器件的最小尺寸,也就是特征尺寸变小了。大规模集成是指在单个芯片上所继承的电子器件数量越来越多。 电子器件微型化和大规模集成的意义: 1)提高速度和降低功耗只有提高集成度,才能减少电子系统内部的连线和最大限度地减少封装管壳对速度的影响。提高速度和提高集成度是统一的,前者必须通过后者来实现。同时采用低功耗、高速度的电路结构(器件结构) 2)提高成品率与可靠性大规模集成电路内部包含的大量元件都已彼此极其紧密地集成在一块小晶片上,因此不像中、小规模集成电路组成的电子系统那样,由于元件与元件,或电路与电路之间装配不紧密,互连线长且暴露在外,易受外界各种杂散信号的干扰,所以说大规模集成电路提高了系统可靠性。 为了提高为电子器件的成品率,需要在少增加电路芯片面积的前提下尽可能容纳更多的电子元件,也就是采取提高元件密度的集成方法。 3)低成本大规模集成电路制造成本和价格比中、小规模集成电路大幅度下降是因为集成度和劳动生产率的不断提高。 综上所述,大规模和超大规模集成电路的微型化、低成本、高可靠和高频高速四大特点,正是电子设备长期追求的技术指标和经济指标,而这四大特点中后三个特点皆源于微型化的特点。因此这四大特点是统一的、不可分割的。 2、超大规模集成电路面临哪些挑战? 答:首先是大直径的硅材料, 随着集成电路技术的发展,硅单晶直拉生产技术,在单晶尺寸、金属杂质含量、掺杂元素和氧分布的均匀性及结晶缺陷等方面得到了不断的改进。目前,通常使用的硅单晶抛光片的直径已达到300mm,400mm硅单晶片的制造也已经开始。如何控制400mm晶体中点缺陷将是面临的重大挑战。 其次是光刻技术:在微电子制造技术中,最为关键的是用于电路图形生成和复制的光刻技术。更短波长光源、新的透镜材料和更高数字孔径光学系统的加工技术,成为首先需要解决的问题;同时,由于光刻尺寸要小于光源波长,使得移相和光学邻近效应矫正等波前工程技术成为光学光刻的另一项关键技术。 最后是器件工艺。当器件的沟道长度缩小到0.1um时,已开始逼近传统的半导体物理的极限。随之而来的是栅氧化层不断减薄,SiO2作为传统的栅氧化层已经难以保证器件的性能。同时随着半导体器件工艺的特征尺寸不断地缩小,芯片内部的多层内连线工艺也逐渐成为半导体工艺发展的挑战。 3、阐述微电子学概念及其重要性。 答:微电子学是研究在固体(主要是半导体)材料上构成的微小型化电路、子系统及系统的电子学分支。 微电子学作为电子学的一门分支学科,主要是研究电子或离子在固体材料中的运动规律及其应用,并利用它实现信号处理功能的科学。 微电子学是以实现电路和系统的集成为目的的,故实用性极强。微电子学中所实现的电路和系统又称为集成电路和集成系统。 微电子学是信息领域的重要基础学科,在信息领域中,微电子学是研究并实现信息获取、传输、存储、处理和输出的科学,是研究信息载体的科学,构成了信息科学的基石。其发展水平直接影响着整个信息技术的发展。 微电子科学技术是信息技术中的关键之所在,其发展水平和产业规模是一个国家经济实力的重要标志。

2014年电子科技大学微电子器件考研真题

电子科技大学 2014年攻读硕士学位研究生入学考试试题 考试科目:832 微电子器件 注:所有答案必须写在答题纸上,写在试卷或草稿纸上均无效。 一、填空题(共48分,每空1.5分) 1、PN结二极管用途广泛,在作为变容二极管使用时,主要利用其()向偏置的 ()电容;在作为温度传感器使用时,主要利用其正向导通压降会随温度的升高而()。 2、一个P+N型的二极管,电子和空穴的寿命分别为τn和τp,在外加正向直流电压V1时电流 为I1,当外加电压反向为-V2时,器件会经历一段反向恢复过程,这主要是由正向导通时存储在()型中性区中的非平衡少子造成的,该非平衡少子的总量为 ()。 3、防止PN结发生热击穿,最有效的措施是降低器件的()。同时,禁带宽带越 ()的半导体材料,其热稳定性越好。(第二个空填“大”或“小”) 4、双极型晶体管的基区宽度调变效应越严重,其厄尔利电压越(),共发射极增量输 出电阻越()。(填“大”或“小”) 5、已知双极型晶体管的基区度越时间和基区少子寿命分别为τb和τB,则1/τB表示的物理 意义为(),因此τb/τB可以表示 ()。 6、MOSFET的亚阈区摆幅S反应了在亚阈区中()的控制能力。 栅氧化层越厚,则S越(),该控制能力越()。(第二个空填“大”或“小”,第三个空填“强”或“弱”) 7、当金属和P型半导体形成金-半接触时,如果金属的功函数大于半导体的功函数,半导体表 面将形成(),该结构()单向导电性。(从以下选项中选择) A 电子阻挡层 B 电子反阻挡层C空穴阻挡层 D 空穴反阻挡层 E 具有 F 不具有 微电子器件试题共6页,第1页

8、MOSFET的跨导是()特性曲线的斜率,而漏源电导是()特性曲 线的斜率。在模拟电路中,MOSFET一般工作在()区,此时理想情况下漏源电导应为零,但实际上由于()和(),漏源电导通常为正的有限值。 9、短沟道MOSFET中采用偏置栅结构或漏端轻掺杂结构,是为了降低漏端附近的电场强度, 从而抑制()效应,防止器件电学特性退化。 10、如果以SiGe来制作BJT的发射区,Si来制作BJT的基区,则与全部采用Si材料的双极 型晶体管相比,其共基极电流放大系数α将()。(填“增大”、“减小”或“不变”) 11、根据恒场等比例缩小法则,当MOSFET的沟道长度缩小K倍时,其阈值电压变为之前的 (),总电容变为之前的(),最高工作频率变为之前的()。 12、研究发现硅-二氧化硅系统中,存在四种形式的电荷或能量状态,包括Na+、K+等可动离 子、()、()以及二氧化硅层中的电离陷阱电荷,通常它们都带正电,因此()型MOSFET的衬底表面更容易反型。 13、PMOS的衬底相对于源端应该接()电位。当|V BS|增加时,PMOS的阈值电压绝对值 将(),该效应叫做()。(第二个空填“增大”、“减小” 或“不变”) 二、简答与作图题(共57分) 1、如图所示,一块掺杂浓度为N D的无限长均匀N型半导体材料,在x的负半轴有一束光稳定地照射在半导体表面,产生体密度为G0的电子-空穴对。(9分) (1)写出该半导体材料在x正半轴的少子扩散方程。(只考虑少子在x方向的运动) (2)如果要通过上述扩散方程求解x正半轴的少子分布,应该采用什么样的边界条件?(3)如果该半导体材料在x正半轴的长度缩短为W(W远小于少子扩散长度),又应该采用什么样的边界条件求解? 微电子器件试题共6页,第2页

微电子学概论复习题

微电子概论习题 第一章绪论 1.画出集成电路设计与制造的主要流程框架。 2.集成电路分类情况如何? 3.微电子学的特点是什么? 4.列举出你见到的、想到的不同类型的集成电路及其主要作用。 5.用你自己的话解释微电子学、集成电路的概念。 6.简单叙述微电子学对人类社会的作用。 第二章半导体物理和器件物理基础 1.什么是半导体?特点、常用半导体材料 2.掺杂、施主/受主、P型/N型半导体 3.能带、导带、价带、禁带 4.半导体中的载流子、迁移率 5.PN结,为什么会单向导电,正向特性、反向特性,PN结击穿有几种 6.双极晶体管工作原理,基本结构,直流特性 7.MOS晶体管基本结构、工作原理、I-V方程、三个工作区的特性 8.MOS晶体管分类 9.载流子的输运有哪些模式?对这些输运模式进行简单的描述。 10.讨论PMOS晶体管的工作原理,写出PMOS管的电流电压方程。 第三章大规模集成电路基础 1.集成电路制造流程、特征尺寸 2.CMOS集成电路特点 3.MOS开关、CMOS传输门特性 4.CMOS反相器特性(电压传输特性、PMOS和NMOS工作区域) 5.CMOS组合逻辑:基本逻辑门、复合门 6.反相器、二输入与非、或非门 7.闩锁效应起因? 第四章集成电路制造工艺 1.集成电路工艺主要分为哪几大类,每一类中包括哪些主要工艺,并简述各工艺的主要作用2.简述光刻的工艺过程 第五章集成电路设计 1.层次化、结构化设计概念,集成电路设计域和设计层次 2.什么是集成电路设计?

3.集成电路设计流程,三个设计步骤 ?系统功能设计 ?逻辑和电路设计 ?版图设计 4.模拟电路和数字电路设计各自的特点和流程 5.版图验证和检查包括哪些内容?如何实现? 6.版图设计规则概念,为什么需要指定版图设计规则,版图设计规则主要内容以及表示方法。7.集成电路设计方法分类 全定制、半定制、PLD 8.标准单元/门阵列的概念,优点/缺点,设计流程 9.PLD设计方法的特点,FPGA/CPLD的概念 10.试述门阵列和标准单元设计方法的概念和它们之间的异同点。 11.标准单元库中的单元的主要描述形式有哪些?分别在IC设计的什么阶段应用? 12.集成电路的可测性设计是指什么? 第六章集成电路设计的EDA系统 1.ICCAD主要有哪几类,主要作用 2.VHDL语言的用途 3.VHDL设计要素:实体、结构体、配置、程序包和库,各自的概念和作用 4.VHDL并行信号赋值语句的硬件行为模型 5.VHDL描述电路的风格 6.信号、变量的区别 7.什么是进程语句,什么是敏感量表 8.什么是事件,什么是模拟周期 9.如何用VHDL产生信号激励,时钟激励 10.什么是综合?综合过程有几个步骤。 11.什么是电路模拟?其在IC设计中的作用 12.SPICE主要可以完成哪些主要的电路分析 13.试述器件模拟和工艺模拟的基本概念。 14.试述面向事件的模拟算法的基本思路。 15.列出逻辑模拟中的主要延迟模型,并给出简单说明。 16.用SPICE模拟软件模拟一个E/D NMOS反相器的直流输出特性,请写出相应的输入文件。 第七章几种重要的特种微电子器件 1.光电器件主要包括哪几类? 2.半导体发光器件的基本原理是什么? 第八章微机电系统 1.MEMS工艺与微电子工艺技术有哪些区别。 2、列举几种你所知道的MEMS器件,并简述其用途。

- 《微电子器件》第三版习题讲解

- 微电子器件期末复习题 含答案

- 17_功率半导体器件基础教学大纲

- 微电子器件期末试题知识分享

- 微电子器件期末复习题含答案

- 微电子器件复习题

- 电子科技大学微电子器件

- 微电子器件复习题

- 大学微电子器件期末考试要点归纳总结

- 华侨大学本科考试卷 微电子器件与电路(16集成)2017-2018期末测试卷A卷

- 清华大学半导体器件张莉期末考题

- 半导体器件期末考试

- 贵州省高一上学期化学期末考试试卷D卷

- 最新微电子工艺学试卷(A卷)及参考答案

- 电子科技大学中山学院微电子器件期末复习重点(陈卉版)

- 新人教版四年级语文上册-单元期中期末专项练习-第八组达标检测B卷及答案

- 微电子技术概论期末试题

- (完整版)电子科技大学微电子器件习题

- 半导体器件期末考试

- 《微电子器件》第三版习题答案