按键控制加法计数器

按键控制加法计数器

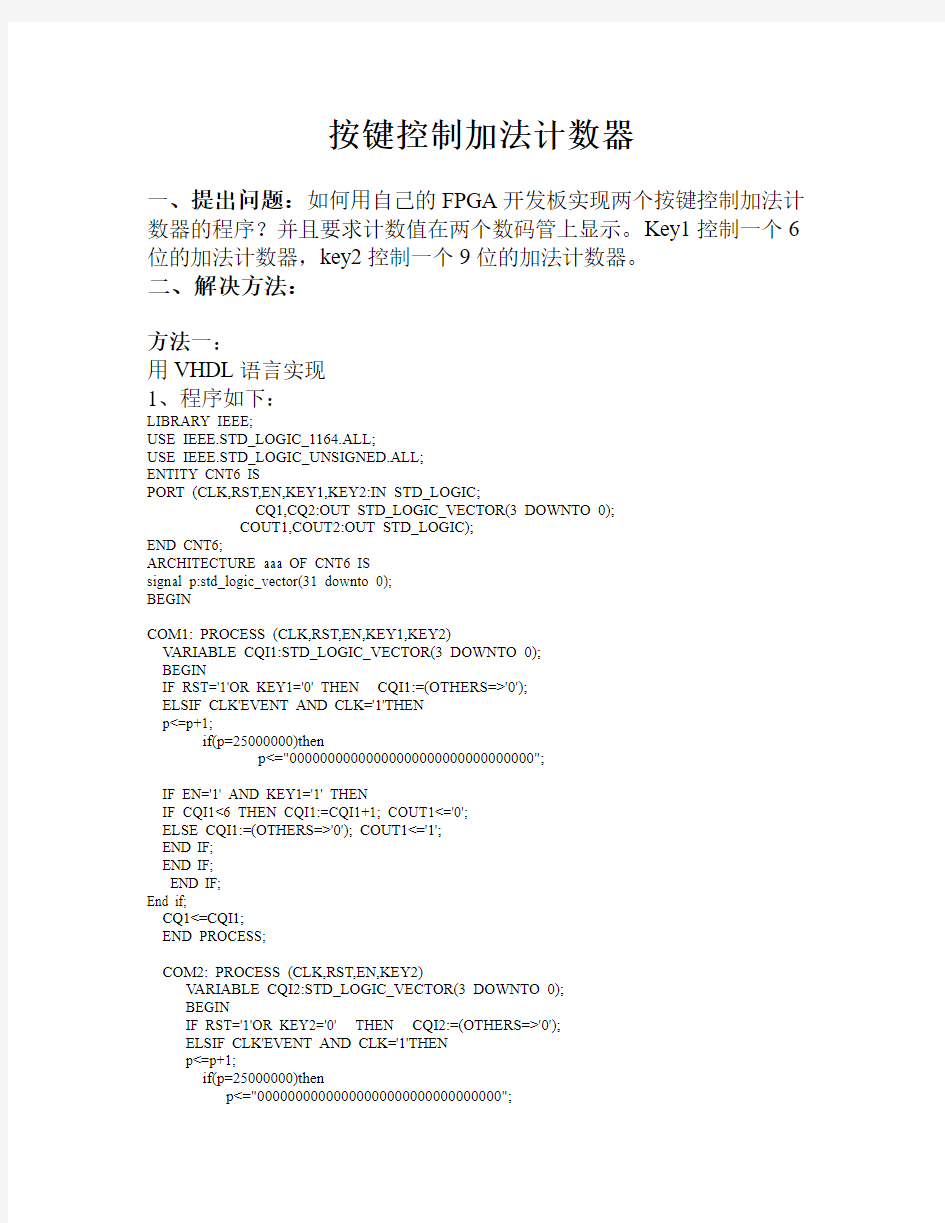

一、提出问题:如何用自己的FPGA开发板实现两个按键控制加法计数器的程序?并且要求计数值在两个数码管上显示。Key1控制一个6位的加法计数器,key2控制一个9位的加法计数器。

二、解决方法:

方法一:

用VHDL语言实现

1、程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT6 IS

PORT (CLK,RST,EN,KEY1,KEY2:IN STD_LOGIC;

CQ1,CQ2:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUT1,COUT2:OUT STD_LOGIC);

END CNT6;

ARCHITECTURE aaa OF CNT6 IS

signal p:std_logic_vector(31 downto 0);

BEGIN

COM1: PROCESS (CLK,RST,EN,KEY1,KEY2)

VARIABLE CQI1:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

IF RST='1'OR KEY1='0' THEN CQI1:=(OTHERS=>'0');

ELSIF CLK'EVENT AND CLK='1'THEN

p<=p+1;

if(p=25000000)then

p<="00000000000000000000000000000000";

IF EN='1' AND KEY1='1' THEN

IF CQI1<6 THEN CQI1:=CQI1+1; COUT1<='0';

ELSE CQI1:=(OTHERS=>'0'); COUT1<='1';

END IF;

END IF;

END IF;

End if;

CQ1<=CQI1;

END PROCESS;

COM2: PROCESS (CLK,RST,EN,KEY2)

VARIABLE CQI2:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

IF RST='1'OR KEY2='0' THEN CQI2:=(OTHERS=>'0');

ELSIF CLK'EVENT AND CLK='1'THEN

p<=p+1;

if(p=25000000)then

p<="00000000000000000000000000000000";

IF EN='1' AND KEY2='1' THEN

IF CQI2<9 THEN CQI2:=CQI2+1;COUT2<='0';

ELSE CQI2:=(OTHERS=>'0');COUT2<='1';

END IF;

END IF;

END IF;

End if;

CQ2<=CQI2;

END PROCESS;

END aaa;

2.程序分析:采用两个进程分别实现6进制加法计数器和9进制加法计数器,这连个计数器均是异步清零、同步使能的。当一个clock时钟来临时且使能en='1',则开始扫描按键是否被按下,当key1被按下时,com1的敏感信号发生跳变,开始运行6进制加法计数器(采用if 条件判断语句,判断是否记满,记满则清0,进位为1,否则继续计数);当key2被按下时同key1。

3. 编译硬件耗用统计报告:

综合报告显示:所占用的总逻辑单元为16个,总的组合功能为16个,专用逻辑寄存器9个。

4.时序仿真图:

仿真波形显示了我们所要的结果,key1为1时,cout1计数,key2为1时,cout2计数。即通过两个按键分别控制了两个计数器计数。

方法二:用Verilog语言实现

1.编写程序如下

module counter(clk,clear,s,q1,q2,c1,c2,key1,key2);

output[3:0] q1,q2;

output c1,c2;

input clk,clear,s,key1,key2;

reg[3:0] q1,q2;

always @(posedge clk)

begin

if (clear)

q1 <= 0;

else

begin

if (s & key1)

begin

if (q1==4'b0101) q1<={4{1'b0}};

else q1=q1+1;

end

end

end

assign c1=((q1==4'b0101)&1);

always @(posedge clk)

begin

if (clear)

q2<=0;

else

begin

if (s & key2)

begin

if (q2==4'b1000) q2<={4{1'b0}};

else q2=q2+1;

end

end

end

assign c2=((q2==4'b1000)&1);

endmodule

2.程序分析:通过行为实例来实现,关键词是always,类似于VHDL 语言中的进程语句,通过无限循环扫描clk上升沿,执行任务。当检测到上升沿时,判断是否有清零信号,若无,并且使能端s与按键同时有效,则开始计数,判断计数溢出,若溢出则清零,并进位,否则继续计数。该程序用的assign连续赋值语句给进位赋值,通过检测溢出,若溢出则为真,与1相与后得到进位的值。

3.编译硬件耗用统计报告:

报告显示:该程序占用的组合逻辑单元为12个,专用逻辑寄存器为8个。

4.时序仿真图:

仿真波形显示了我们所要的结果,key1为1时,cout1计数,key2为1时,cout2计数。即通过两个按键分别控制了两个计数器计数。

三.方案综合比较:

1.程序比较:方法一与方法二均实现了同步使能,以及按键控制加法计数器的功能,但方法一实现的是异步清零,方法二实现的是同步清零。考虑到实际情况,异步清零更适合于应用。

2.编译硬件耗用统计报告:方法一使用到了16个组合逻辑单元,9个专用寄存器;方法二使用到了12个组合逻辑单元,8个专用寄存器。比较之后发现verilog使用的硬件资源少于vhdl,所以在编写小规模的程序时,用verilog更为节约硬件资源。

3. 时序仿真图:两者的时序仿真效果差别不大,并且都验证了程序的正确性。

四.实际电路测试:刚开始时,我们将仿真成功的程序下载到FPGA实验板上,发现没有现象,于是我们在此基础上加上适当的延迟时间,得到了想要达到的效果,分别用两个按键控制数码管显示,用发光二极管显示进位。当key1按下时,数码管1开始6进制计数,溢出时led1点亮,key2按下时,数码管2开始9进制计数,溢出时led2点亮。

五.心得与体会:通过本次实验,我们对计数器有了更为深刻的理解,对于多进程的使用也更加熟练了,通过仿真、下载到显示,每一个步骤都充满了乐趣与挑战,我们知道,学习的浪潮只会越推越高,只停驻于课本,是远远不够的,翻阅大量的资料书籍,并且结合课本基础知识方是良策。从一开始,我们就知道,学习不是一个人的学习,大的前提不说,小组合作显得尤为重要,而在这一点上,我们做得很好,且不论做出来的成果如何,但至少我们一起在共同进步,学习氛围也极其良好,遇到不懂的相互讨论,然后共同寻找解决的方

案,这样下来,我们的心情都很愉悦,学习劲头也很足,我们知道,挑战很大,可是信心十足!大家一起加油吧!

同步二进制加法计数器

同步二进制加法计数器 F0302011 5030209303 刘冉 计数器是用来累计时钟脉冲(CP脉冲)个数的时序逻辑部件。它是数字系统中用途最广泛的基本部件之一,几乎在各种数字系统中都有计数器。它不仅可以计数,还可以对CP 脉冲分频,以及构成时间分配器或时序发生器,对数字系统进行定时、程序控制操作。此外,还能用它执行数字运算。 1、计数器的特点: 在数字电路中,把记忆输入CP脉冲个数的操作叫做计数,能实现计数状态的电子电路称为计数器。特点为(1)该电路一般为Moore型电路,输入端只有CP信号。 (2)从电路组成看,其主要组成单元是时钟触发器。 2、计数器分类 1) 按CP脉冲输入方式,计数器分为同步计数器和异步计数器两种。 同步计数器:计数脉冲引到所有触发器的时钟脉冲输入端,使应翻转的触发器在外接的CP脉冲作用下同时翻转。 异步计数器:计数脉冲并不引到所有触发器的时钟脉冲输入端,有的触发器的时钟脉冲输入端是其它触发器的输出,因此,触发器不是同时动作。 2) 按计数增减趋势,计数器分为加法计数器、减法计数器和可逆计数器三种。 加法计数器:计数器在CP脉冲作用下进行累加计数(每来一个CP脉冲,计数器加1)。 3) 按数制分为二进制计数器和非二进制计数器两类。 二进制计数器:按二进制规律计数。最常用的有四位二进制计数器,计数范围从0000到1111。 异步加法的缺点是运算速度慢,但是其电路比较简单,因此对运算速度要求不高的设备中,仍不失为一种可取的全加器。同步加法优点是速度快,虽然只比异步加法快千分之一甚至几千分之一秒,但对于计数器来讲,却是十分重要的。所以在这个高科技现代社会中,同步二进制计数器应用十分广泛。 下图为三位二进制加法计数器的电路图。 图1 三位二进制计数器 图示电路为对时钟信号计数的三位二进制加法计数器或称为八进制加法计数器。 该电路的经典分析过程: 1.根据电路写出输出方程、驱动方程和状态方程 2. 求出状态图 3.检查电路能否自启动 4.文字叙述逻辑功能 解:

汇编语言实现十进制加减计算器

课程设计 题目十进制数加减计算器学院计算机科学与技术 专业计算机科学与技术 班级计算机0808班 姓名何爽 指导教师袁小玲 2010 年12 月31 日

课程设计任务书 学生姓名:何爽专业班级:计算机0808班 指导教师:袁小玲工作单位:计算机科学与技术学院 题目: 十进制数加减计算器的设计 初始条件: 理论:学完“汇编语言程序设计”、“课程计算机概论”、“高级语言程序设计”和“数字逻辑”。 实践:计算机学院科学系实验中心提供计算机和软件平台。如果自己有计算机可以在其上进行设计。 要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求) (1)十进制数加减计算器的设计。 (2)程序应有操作提示、输入和输出,界面追求友好,最好是菜单式的界面。 (3)设计若干用例(测试数据),上机测试程序并分析(评价)所设计的程序。 (4)设计报告格式按附件要求书写。课程设计报告书正文的内容应包括: 在正文第一行写课程设计题目; 1.需求说明(要求、功能简述)或问题描述; 2.设计说明(简要的分析与概要设计); 3.详细的算法描述; 4.源程序与执行结果(含测试方法和测试结果); 5.使用说明; 6.总结,包括设计心得(设计的特点、不足、收获与体会)和展望(该 程序进一步改进扩展的设想)。 时间安排: 设计时间一周:周1:查阅相关资料。 周2:系统分析,设计。 周3~4:编程并上机调试。 周5:撰写课程设计报告。 设计验收安排:20周星期五8:00起到计算机学院科学系实验中心进行上机验收。 设计报告书收取时间:20周的星期五下午5:00之前。 指导教师签名: 2010年12月31日 系主任(或责任教师)签名: 2010年12月31日

按键实现0~9999计数器 单片机

按键调节数码管显示 功能:通过按键加减数码管所显示的数字 按下k1加1,最大加到9999 按下k2减1,最小减到0 按下k3清零复位 C语言程序 //---------------------------------------------------------------------- //名称:按键调节数码管显示 //---------------------------------------------------------------------- //功能:通过按键加减数码管所显示的数字 // 按下k1加1,最大加到9999 // 按下k2减1,最小减到0 // 按下k3清零复位 //---------------------------------------------------------------------- //姓名:陈润源 //地点:内江职业技术学院 //时间:2019年4月6日21:40:41 //---------------------------------------------------------------------- #include

sbit k3 = P1^2; //复位 void key(void); void display(void); uchar code table[]={0xc0,0xf9,0xa4,0xb0,0x99, 0x92,0x82,0xf8,0x80,0x90}; //数组 char m=99,n=98; //显示初值,m,n的值决定开机显示数值 //**************************************** //延时程序 //**************************************** void delayms(uint xms) { uint i,j; for(i=xms;i>0;i--) for(j=110;j>0;j--); } //*********************************************** //显示程序 //*********************************************** void display(void) { P2=0X08; P0=table[m%10]; //显示个位 delayms(5); P2=0X04; P0=table[m/10]; //显示十位 delayms(5); P2=0X02; P0=table[n%10]; //显示百位 delayms(5); P2=0X01; P0=table[n/10]; //显示千位 delayms(5); } //*************************************************** //按键处理 //*************************************************** void key() { if(k1==0) //检测按键是否被按下 { //延时消抖 delayms(10); if(k1==0) //再次检测是否真正按下按键 { m++; //m自加一 if(m>=100) //如果m加到100则n加一 (限制m的取值范围) 个位、十位最大显示99 {

做一个五进制的加减法计数器

做一个五进制的加减法 计数器 标准化管理部编码-[99968T-6889628-J68568-1689N]

一、做一个五进制的加减法计数器,输入控制端为1时,做加法,为0时, 做减法,用JK触发器实现。 第一步:根据要求进行逻辑抽象,得出电路的原始状态图。 取输入数据变量为X,检测的输出变量为Z,该电路的功能是五进制计 数器。当X=1时,计数器作加“1”运算,设初态为S 0。状态由S 做加1运 算,状态转为S 1,输出为0;状态S 1 做加1运算,转为状态S 2 ,输出为0;状 态S 2做加1运算,转为状态S 3 ,输出为0;状态S 3 做加1运算,转为状态S 4 , 输出为0;当状态S 4继续做加1运算时,状态由S 4 转到S ,输出为1。当X=0 时,计数器作减“1”运算。状态由S 做减1运算,此时产生借位,状态转为 S 4,输出为1;状态S 4 做减1运算,转为状态S 3 ,输出为0;状态S 3 做减1运 算,转为状态S 2,输出为0;状态S 2 做减1运算,转为状态S 1 ,输出为0;状 态S 1做减1运算,状态由S 1 转为状态S ,输出为0。 由此得出状态转换图:第二步:状态编码。 该电路是五进制计数器,有五种不同的状态,分别用S 0、S 1 、S 2 、S 3 、 S 4 表示五种状态,这五种状态不能作状态化简。在状态编码时,依据 2n+1 洛阳理工学院 十 进 制 4 位 加 法 计 数 器 系别:电气工程与自动化系 姓名:李奇杰学号:B10041016 十进制4位加法计数器设计 设计要求: 设计一个十进制4位加法计数器设计 设计目的: 1.掌握EDA设计流程 2.熟练VHDL语法 3.理解层次化设计的内在含义和实现 设计原理 通过数电知识了解到十进制异步加法器的逻辑电路图如下 Q3 则可以通过对JK触发器以及与门的例化连接实现十进制异步加法器的设计 设计内容 JK JK触发器的VHDL文本描述实现: --JK触发器描述 library ieee; use ieee.std_logic_1164.all; entity jk_ff is port( j,k,clk: in std_logic; q,qn:out std_logic ); end jk_ff; architecture one of jk_ff is signal q_s: std_logic; begin process(j,k,clk) begin if clk'event and clk='0' then if j='0' and k='0' then q_s <= q_s; elsif j='0' and k='1' then q_s <= '0'; elsif j='1' and k='0' then q_s <= '1'; elsif j='1' and k='1' then q_s <= not q_s; end if; end if; end process; q <= q_s; qn <= not q_s; end one; 元件门级电路: 与门VHDL文本描述实现: --与门描述library ieee; use ieee.std_logic_1164.all; 目录 <一>、前言 (1) 一、设计题目 (2) 二、题目功能及要求 (2) 三、总体方案设计 (2) 四、单元电路设计 (2) (一)、电路的结构设计 (2) (二)、元器件参数设计 (6) 五、整体电路分析 (6) 六、元器件明细 (7) 七、设计结果验证 (7) 八、电路的使用说明书 (8) 九、心得体会 (8) 十、参考资料 (8) 前言 一转眼,大二已经结束了,在这一学年里我们学了电路、模拟电子技术和数字电子技术等许多课程,学习和掌握了电子方面的很多理论知识。 为了让我们更好的掌握所学的电子理论知识,并将理论联系到实际中,学校特地的为我们安排了这次的电子线路实训。让我们在掌握了模电、数电理论的基础上,进行理论联系实际和体会电子技术应用的初级训练。在实训的过程中,我们自己设计自己焊接,运用课堂上所学的理论知识对实际问题进行分析和解决,并弄懂所做电路的工作原理,搞清电路中各元器件的功能、作用,同时学习查阅资料,自学一些课外知识。增强了我们分析问题和解决问题的能力,培养和训练了我们制作电子电路的基本技能,提高了我们各方面的综合能力,为我们今后更好的适应社会的需求打下了基础。 这样电子线路实训的机会是很难得,大学四年这样的机会并不多,所以我很珍惜这次的实训,非常认真的对待它。最后在自己的努力和老师的指导、同学的帮助下,我顺利的完成了这次的电子线路的实训。 一、设计题目 五进制计数器 二、题目功能及要求 设计一个五进制计数器,实现0-5的循环计数。要求用555电路来实现脉冲的产生,其他常用芯片可自己选择。 三、总体方案设计 该五进制计数器的控制系统框图如下图所示。由计数控制器、状态译码器、计数器、秒脉冲发生器和数码显示器组成。 计数控制器主要用于记录计数器的工作状态,通过译码器来控制数码显示器,脉冲发生器产生整个定时系统的时基脉冲,通过计数器实现计数。 其中脉冲发生器用555电路来实现,计数器选用十进制计数器74160,计数控制器是一个与非门,选用用74ls00,译码器则用7448来实现。 四、单元电路设计 (一)、电路的结构设计 1、脉冲发生器的设计 脉冲信号发生器用的是555定时器构成的多谐震荡器,555定时器是一种模拟和数字功能相结合的中规模集成器件,555定时器成本低,性能可靠,只需要外接几个电阻、电容,就可以实现多谐振荡器,单稳态触发器及施密特触发器等脉冲产生与变换电路。 这里用的是555构成的多谐震荡器, 其电路图如下: 课程设计报告 课程名称:单片机课程设计 题目:基于单片机的频率计数器设计 学院:环境与化学工程系:过程装备与测控工程 专业: 班级: 学号: 学生姓名: 起讫日期: 指导教师: 摘要 数字频率计是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量仪器。它是一种用十进制数字,显示被测信号频率的数字测量仪器。它的基本功能是测量正弦信号,方波信号以及其他各种单位时间内变化的物理量。本课程设计主要设计一个简易的频率计,来实现信号在0-9999HZ范围内周期变化的方波频率的测定。 该文主要介绍了基于STC89C52 单片机频率计的设计方案和实现方法,该系统主要由硬件和软件两部分组成,其中重点给出了具体硬件电路图和软件流程图以及具体工作原理。硬件部分通过洞洞板的布线设计帮助,可以确保焊接时尽量少的飞线和出错。软件通过keil μvision编译及调试,其中在P1.7口编入了一个5500HZ的方波,用以仿真调试该频率计的软硬件功能是否能够实现输出频率的功能。另外,本设计多增加了一个按键功能,通过一个按键来控制定时计数器的开始和关闭。该频率计还带有3*3的矩阵键盘,可以作为扩展应用区,通过编程实现。本设计中用的是LED共阴数码管,输出频率时采用的事动态显示的方法。 关键词:频率计;单片机;动态显示 目录 一、频率计数器的设计任务和要求 (1) 1.1 频率计数器的设计任务 (1) 1.2 设计要求及发挥部分 (1) 二、方案的总体设计 (1) 2.1 方案的设计 (1) 2.2 方案的整体框图 (2) 2.3 方案的说明 (2) 三、硬件设计 (2) 3.1 单片机的最小系统 (2) 3.1.1 上电复位电路 (2) 3.1.2 晶振电路 (3) 3.2 LED数码管显示电路 (3) 3.3 整体电路 (4) 四、软件设计 (4) 4.1 程序流程图 (5) 4.2 初始化子函数 (5) 4.3 延时子函数 (5) 4.4 中断子函数 (5) 五、系统的调试和说明 (6) 5.1 C程序的说明 (6) 5.2 C程序编译的结果 (6) 5.3 实物图 (7) 六、设计总结与心得体会 (8) 6.1设计总结 (8) 6.2 设计心得 (9) 七、参考文献 (9) 附录 (10) 十进制加减法计数器 1.实验要求 (1)在Modelsim环境中编写十进制加减法计数器程序; (2)编译无误后编写配套的测试程序; (3)仿真后添加信号,观察输出结果。 2.设计程序如下 module decade_counter #(parameter SIZE=4) (input clock,load_n,clear_n,updown, input [SIZE-1:0]load_data, output reg [SIZE-1:0]q ); always @(negedge load_n,negedge clear_n,posedge clock) if (!load_n) q<=load_data; else if (!clear_n) q<=0; else //clock??? if(updown) q<=(q+1)%10; else begin if(q==0) q<=9; else q<=q-1; end endmodule 3.测试程序如下 `timescale 1ns/1ns module test_decade_counte; reg clock,load_n,clear_n,updown; reg [3:0]load_data; wire [3:0]q; decade_counter T1(clock,load_n,clear_n,updown,load_data,q); initial begin clock=0;clear_n=0; #30 clear_n=1;load_n=0;load_data=7; #30 load_n=1;updown=0; #300 updown=1; #300 updown=0; #300 updown=1; #300 $stop; end always #10 clock=~clock; always @(q) $display("At time%t,q=%d",$time,q); endmodule 4.波形如下 5.测试结果如下 # At time 0,q= 0 # At time 30,q= 7 # At time 70,q= 6 # At time 90,q= 5 # At time 110,q= 4 # At time 130,q= 3 # At time 150,q= 2 # At time 170,q= 1 # At time 190,q= 0 # At time 210,q= 9 # At time 230,q= 8 # At time 250,q= 7 # At time 270,q= 6 # At time 290,q= 5 # At time 310,q= 4 # At time 330,q= 3 一、做一个五进制的加减法计数器,输入控制端为1时,做加法,为0时,做减法, 用J K 触发器实现。 第一步:根据要求进行逻辑抽象,得出电路的原始状态图。 取输入数据变量为X,检测的输出变量为乙该电路的功能是五进制计数器。当X=1时,计数器作加“ 1”运算,设初态为S o。状态由S o做加1运算,状态转为S i,输出为0;状态S i做加1运算,转为状态S2,输出为0;状态S2做加1运算,转为状态S3,输出为0;状态S3做加1运算,转为状态S4,输出为0;当状态S4继续做加1 运算时,状态由S4转到S0,输出为1。当X=0时,计数器作减“1”运算。状态由S0 做减1运算,此时产生借位,状态转为S4,输出为1;状态S4做减1运算,转为状态S3,输出为0;状态S3做减1运算,转为状态S2,输出为0;状态S2做减1运算,转为状态S1,输出为0;状态S1做减1运算,状态由S1转为状态 S0,输出为0。由此得出状态转换图: 第二步:状态编码。 该电路是五进制计数器,有五种不同的状态,分别用S0、S1、S2、S3、S4表示五种状态,这五种状态不能作状态化简。在状态编码时,依据2n+1 第三步:求出输出方程,状态方程和驱动方程(控制函数)。用 JK触发器构成逻辑电路,JK触发器的特性方程Q2n Q1n 00 01 Q n+1=J Q n+ K Q n。 XQ3n 00 01 11 10 1 000 0 X X X 1V X n 0000 00011110 (1) Q2n Q1n _________ (b) Q3n+1=X Q2 Q1n+ X Q3n Q2n Q1n 2n Q1n 00 01 11 10 1000 X X X 0X A X 00u0 状态转换表如下: 1 1 10 XQ3 00 01 11 10 Z=X Q n3 + X Q3 1n XQ3 《一个按键的多次击键组合判别技巧》大话篇 小匠自从上次在旧社区发表了一篇《<程序编写规范倡议书>大话篇》后,好久没有发表"高"论了.急坏了一帮MM,以为小匠退隐江湖了。 (斑竹在旁问道:“MM”不是“Mie Mie”,而是“Ma Ma”吧?) 论坛内外谣言四起,有人说小匠改行了,不做程序匠,改做泥水匠了;还有人说小匠上阿富汗反恐怖去了;其实非也,只因新板论坛启用后,小匠一直用不惯...... (斑竹在旁笑道:是“用不来”吧?) 今天,小匠再次隆重登坛献演。贴一个小程序段..... (斑竹道:我看是“蹬痰现眼”吧?) (程序匠人贴完帖子,下到后台,一边洗着手上残余的浆糊,一边哼着小曲:“如果你的‘芯’是一座作坊,我愿作那不知疲倦的程序匠,……”) (一黑客悄悄贴近匠人,将一个废弃的浆糊桶扣到匠人头上......) (匠人忙问:“斑竹,谁把灯给关了?”) (众人哈哈大笑!......) 一个按键的多次击键组合判别技巧 有时在设计中,往往要用一个按键来输入多种信息。如:单击/双击/三击、短击/长击、还有各种组合击键方式。可以用以下程序来做。如果按键闭合时间<500MS,判断为一次短击(0); 如果按键闭合时间>500MS,判断为一次长击(1); 两次击键时间间隔应<700MS,如果按键释放后700MS内无键按下,则结束读键。 读键完毕返回一个键号值KEY_NUM。其意义如下: KEY_NUM 意义 00000000 无键按下过 00000001 无意义 00000010 单次短击 00000011 单次长击 00000100 短击+ 短击 00000101 短击+ 长击 00000110 长击+ 短击 00000111 长击+ 长击 长沙学院课程设计说明书 题目同步五进制加法计数器 系(部) 电子与通信工程 专业(班级) 电气工程及其自动化 姓名黄明发 学号*********** 指导教师瞿瞾 起止日期 5.21-5.25 数字电子技术课程设计任务书(5) 系(部):电子与通信工程系专业:电气工程及其自动化指导教师:瞿曌 课题名称同步五进制加法计数器电路设计 设 计内容及要求 试用触发器设计一个同步五进制加法计数器。应检查是否具有自启动能力。 设置一个复位按钮和一个启动按钮。 采用数码管显示计数器的数值。 设计工作量1、系统整体设计; 2、系统设计及仿真; 3、在Multisim或同类型电路设计软件中进行仿真并进行演示; 4、提交一份完整的课程设计说明书,包括设计原理、仿真分析、调试过程,参考文献、设计总结等。 进度安排起止日期(或时间量)设计内容(或预期目标)备注第一天课题介绍,答疑,收集材料 第二天设计方案论证 第三天进行具体设计 第四天进行具体设计 第五天编写设计说明书 教研室 意见 年月日系(部)主 管领导意见 年月日 长沙学院课程设计鉴定表 姓名黄明发学号20100 42213 专业电气工程及其自动 化 班级 2 设计题目同步五进制加法计数器指导教师瞿瞾指导教师意见: 评定等级:教师签名:日期: 答辩小组意见: 评定等级:答辩小组长签名:日期: 教研室意见: 教研室主任签名:日期: 系(部)意见: 系主任签名:日期: 说明课程设计成绩分“优秀”、“良好”、“及格”、“不及格”四类; 目录 课程设计的目的 (4) 课程设计内容及要求 (4) 课程设计原理 (4) 课程设计方案步骤 (4) 建立状态图 (5) 建立状态表 (5) 状态图化简、分配,建立卡诺图 (5) 确定状态方程以及激励方程 (5) 绘制逻辑图,检查自启动能力 (6) 绘制逻辑电路图并仿真 (6) 观察时序电路逻辑分析仪,调节频率 (6) 课程设计的思考与疑问 (7) 课程设计总结 (8) 参考文献 (8) 实验1 十进制加减法计数器 实验地点:电子楼218 实验时间:2012年10月19日指导老师:黄秋萍、陈虞苏 实验要求:设计十进制加减法计数器,保留测试程序、设计程序、仿真结果 1.设计程序: module count(EN,CLK,DOUT,F,RST); input EN,CLK,F,RST; output [3:0]DOUT; reg [3:0]DOUT; always@(posedge CLK) begin :abc if(EN) if(!RST) if(F) begin :a DOUT=DOUT+1; if(DOUT==10) DOUT=0; end //END A else begin :b DOUT=DOUT-1; if(DOUT==15) DOUT=9; end else DOUT=0; else DOUT=DOUT; end endmodule 2.测试程序 `timescale 10ns/1ns module test_count; wire [3:0] DOUT; reg EN,F,RST,CLK; count M(EN,CLK,DOUT,F,RST); initial begin :ABC CLK=0; EN=0; RST=1; F=1; #100 EN=1; #200 RST=0; #1500 F=0; #3000 $stop; end always #50 CLK=~CLK; initial $monitor("EN=%b,F=%b,RST=%b,DOUT%D",EN,F,RST,DOUT); endmodule 3.测试结果 # EN=0,F=1,RST=1,DOUT x # EN=1,F=1,RST=1,DOUT x # EN=1,F=1,RST=1,DOUT 0 # EN=1,F=1,RST=0,DOUT 0 # EN=1,F=1,RST=0,DOUT 1 # EN=1,F=1,RST=0,DOUT 2 # EN=1,F=1,RST=0,DOUT 3 # EN=1,F=1,RST=0,DOUT 4 # EN=1,F=1,RST=0,DOUT 5 # EN=1,F=1,RST=0,DOUT 6 # EN=1,F=1,RST=0,DOUT 7 # EN=1,F=1,RST=0,DOUT 8 # EN=1,F=1,RST=0,DOUT 9 # EN=1,F=1,RST=0,DOUT 0 # EN=1,F=1,RST=0,DOUT 1 # EN=1,F=1,RST=0,DOUT 2 # EN=1,F=1,RST=0,DOUT 3 # EN=1,F=1,RST=0,DOUT 4 # EN=1,F=1,RST=0,DOUT 5 # EN=1,F=0,RST=0,DOUT 5 # EN=1,F=0,RST=0,DOUT 4 # EN=1,F=0,RST=0,DOUT 3 # EN=1,F=0,RST=0,DOUT 2 # EN=1,F=0,RST=0,DOUT 1 # EN=1,F=0,RST=0,DOUT 0 # EN=1,F=0,RST=0,DOUT 9 # EN=1,F=0,RST=0,DOUT 8 # EN=1,F=0,RST=0,DOUT 7 # EN=1,F=0,RST=0,DOUT 6 # EN=1,F=0,RST=0,DOUT 5 计控学院 College of computer and control engineering Qiqihar university 电气工程课程设计报告题目:基于单片机的光电计数器 系别电气工程系 专业班级电气123班 学生姓名宋恺 学号2012024073 指导教师李艳东 提交日期 2015年6月 24日 成绩 电气工程课程设计报告 摘要 光电计数器是利用光电元件制成的自动计数装置。其工作原理是从光源发出的一束平行光照射在光电元件(如光电管、光敏电阻等)上,每当这束光被遮挡一次时,光电元件的工作状态就改变一次,通过放大器可使计数器记下被遮挡的次数。光电计数器的应用范围非常广泛,常用于记录成品数量,例如绕线机线圈匝数的检测、点钞机纸币张数的检测、复印机纸张数量的检测,或展览会参观者人数。 光电计数器与机械计数器相比,具有可靠性高、体积小、技术频率高、能和计算机链接实现自动控制等优点。本文即介绍基于MCS-51单片机的光电技术器。 关键词:单片机;光电计数器;数码显示;自动报警 齐齐哈尔大学计控学院电气工程系课程设计报告 目录 1 设计目的及意义 (1) 2 设计内容 (1) 2.1 系统整体设计 (1) 2.1.1 实验方案 (1) 2.1.2 光电计数器结构框图 (2) 图1 光电计数器结构框图 (2) 2.2系统硬件设计 (2) 2.2.1稳压直流电源电路 (2) 2.2.2发射接收电路 (3) 2.2.3显示电路 (3) 2.2.4报警电路 (4) 2.2.5硬件系统 (4) 2.3系统软件设计 (6) 3 结论7 4 参考文献 (8) 西北师范大学知行学院 数字电子实践论文 课题:74ls161组成的十进制加法计数器 (置数法) 班级:14电本 学号:14040101114 姓名:于能海 指导老师:崔用明 目录 第1章前言 (1) 1.1 摘要 (1) 1.2 设计目的 (2) 1.3 设计内容及要求 (2) 第2章设计方案 (3) ....................................................................................................................... 错误!未定义书签。 2.1主要芯片功能介绍 (3) 2.2.1 四位二进制计数器74161介绍 (3) ............................................................................................................... 错误!未定义书签。 2.2 工作原理 (4) 第3章硬件设计 (4) 3.1 单元电路设计 (4) 3.2 总硬件电路图 (5) 第4章仿真与试验 (6) 4.1 仿真结果 (6) 4.2 调试中遇到的问题 (7) 第5章结论和体会 (8) 第1章前言 1.1 摘要在数字电路技术的课程中,计数器的功能是记忆脉冲的个数,它是数字系统中应用最广泛的基本时序逻辑构件。计数器在微型计算机系统中的主要作用就是为CPU和I/O设备提供实时时钟,以实现定时中断、定时检测、定时扫描、定时显示等定时控制,或者对外部事件进行计数。一般的微机系统和微机应用系统中均配置了定时器/计数器电路,它既可当作计数器作用,又可当作定时器使用,其基本的工作原理就是"减1"计数。计数器:CLK输入脉冲是一个非周期事件计数脉冲,当计算单元为零时,OUT输出一个脉冲信号,以示计数完毕。 本十进制加法计数器是基于74161芯片而设计的, 该十进制加法计数器设计理念是用于工厂流水线上产品计数,自动计数,方便简单。 关键词:74ls161计数器 Introduction In the course of digital circuit technology, the counter memory function is the number of pulses, it is a digital system, the most widely used basic sequential logic components. The main role of the counter in the micro-computer system is to provide real-time clock for the CPU and I / O devices to achieve the timer interrupt, timing detection, scheduled scanning, the timing display timing control, or to count external events. General computer systems and computer application systems are equipped with a timer / counter circuit, it can as a counter action, but also as a timer, the basic working principle is "minus 1" count. Counter: CLK input pulse is a non-periodic event count pulses to zero when calculating unit, OUT outputs a pulse signal, to show the count is completed. The decimal addition counter is designed based on the 74161 chip, the low potential sensor senses when to rely on external signals, sensors in an object within the sensing range, otherwise it is a high potential. Within the sensing range of the sensor when an object is moved out of date, sensor potential from high to low and then high, appears on the edge. Counter is automatically incremented and displayed on a digital control. The decimal addition counters have two seven-segment LED. It can count from 0 to 99 objects, and easy to expand. The design concept of decimal addition counter is used to count on a factory assembly line products, automatic counting, convenient and simple. Keywords:74ls161counter 在数字系统中,常需要对时钟脉冲的个数进行计数,以实现测量、运算和控制等功能。具有计数功能的电路,称为计数器。 计数器是一种非常典型、应用很广的时序电路,计数器不仅能统计输入时钟脉冲的个数,还能用于分频、定时、产生节拍脉冲等。计数器的类型很多,按计数器时钟脉冲引入方式和触发器翻转时序的异同,可分为同步计数器和异步计数器;按计数体制的异同,可分为二进制计数器、二—十进制计数器和任意进制计数器;按计数器中的变化规律的异同,可分为加法计数器、减法计数器和可逆计数器。 二进制加法计数器运用起来比较简洁方便,结构图和原理图也比其它进制的简单明了,但二进制表示一个数时,位数一般比较长。十进制是我们日常生活中经常用到的,不用转换,所以设计十进制加法计数器比设计二进制加法计数器应用广泛,加法器是以数据的累加过程,日常生活中,数据的累加普遍存在,有时候需要一种计数器对累加过程进行运算处理,所以设计十进制加法计数器应广大人们生活的需要,对我们的生活有一个积极地促进作用,解决了生活中许多问题,所以会设计十进制加法计数器使我们对数字电路的理论和实践知识的充分结合,也使我们对电子技术基础有了深刻的了解,而且增强了我们对电子技术基础产生了浓厚的兴趣,这次课程设计使我受益匪浅! 一、设计题目 (3) 二、设计目的 (3) 三、设计依据 (3) 四、设计内容 (3) 五、设计思路 (4) 六、设计方案 (7) 七、改进意见 (10) 八、设计总结 (11) 九、参考文献 (12) 一、设计题目 十进制加法计数器 二、设计目的 1.学习电子电路设计任务。 2.通过课程设计培养学生自学能力和分析问题、解决问题的能力。 3.通过设计使学生具有一定的计算能力、制图能力以及查阅手册、使用国家技术标准的能力和一定的文字表达能力。 三、设计依据 1.用JK触发器组成。 2.实现同步或异步加法计数。 四、设计内容 1.复习课本,收集查阅资料,选定设计方案; 2.绘制电气框图、电气原理图; 3.对主要元器件进行计算选择,列写元器件的规格及明细表; 4.设计总结及改进意见; 5.参考资料; 6.编写说明书。 十进制加法器设计 1课程设计的任务与要求 课程设计的任务 1、综合应用数字电路知识设计一个十进制加法器。了解各种元器件的原理及其应用。 2、了解十进制加法器的工作原理。 3、掌握multisim 软件的操作并对设计进行仿真。 4、锻炼自己的动手能力和实际解决问题的能力。 5、通过本设计熟悉中规模集成电路进行时序电路和组合电路设计的方法,掌握十进制加法器的设计方法。 课程设计的要求 1、设计一个十进制并运行加法运算的电路。 2、0-9十个字符用于数据输入。 3、要求在数码显示管上显示结果。 2十进制加法器设计方案制定 加法电路设计原理 图1加法运算原理框图 如图1所示 第一步 置入两个四位二进制数。例如(1001)2,(0011)2和(0101)2,(1000)2,同时在两个七段译码显示器上显示出对应的十进制数9,3和5,8。 第二步将置入的数运用加法电路进行加法运算。 第三步前面所得结果通过另外两个七段译码器显示。即: 加法运算方式,则(1000)2+(0110)2=(1110)2 十进制8+6=14 并在七段译码显示出14。运算方案 通过开关S1——S8接不同的高低电平来控制输入端所置的两个一位十进制数,译码显示器U8和U9分别显示所置入的两个数。数A直接置入四位超前进位加法器74LS283的A4——A1端,74LS283的B4——B1端接四个2输入异或门。四个2输入异或门的一输入端同时接到开关S1上,另一输入端分别接开关S5——S8,通过开关S5——S8控制数B的输入,通过加法器74LS283完成两个数A和B的相加。由于译码显示器只能显示0——9,所以当A+B>9时不能显示,我们在此用另一片芯片74LS283完成二进制码与8421BCD码的转换,即S>9(1001)2时加上3(0011)2,产生的进位信号送入译码器U10来显示结果的十位,U11显示结果的个位。 3十进制加法器电路设计 加法电路的实现 用两片4位全加器74LS283和门电路设计一位8421BCD码加法器。由于一位8421BCD 数A加一位数B有0到18这十九种结果。而且由于显示的关系,当大于9的时候要加六转换才能正常显示,所以设计的时候有如下的真值表: _ 等级: 课程名称单片机原理及应用 课题名称频率计数器 专业电子信息工程 班级1302 学号201301030218 姓名许聪 指导老师寻大勇等 2016年3月25日 电气信息学院 课程设计任务书 课题名称频率计数器 姓名许聪专业电子信息班级1302 学号18 指导老师寻大勇 课程设计时间2016年3月14日-2016年3月25日 教研室意见意见:审核人: 一、任务及要求 设计任务: 本课题以单片机为核心,设计和制作一个频率计数器,来完成对输入的信号进行频率计数,计数的频率结果能够显示出来。要求能够对0-250KHz的信号频率进行准确计数,计数误差不超过±1HZ。 设计要求: (1)确定系统设计方案; (2)进行系统的硬件设计; (3)完成应用程序设计; (4) 应用系统的硬件和软件的调试。 二、进度安排 第一周: 周一:集中布置课程设计任务和相关事宜,查资料确定系统总体方案。 周二~周三:完成硬件设计和电路连接 周四~周日:完成软件设计 第二周: 周一~周三:程序调试 周四~周五:设计报告撰写。周五进行答辩和设计结果检查。 三、参考资料 1、王迎旭等.单片机原理及及应用. 2版.机械工业出版社,2012 2、胡汉才.单片机原理及其接口技术.3版.清华大学出版社,2010. 3、戴灿金.51单片机及其C语言程序设计开发实例.清华大学出版社,2010 目录 第1章设计任务及要求 (1) 1.1设计任务 (1) 1.2设计要求 (1) 第2章系统方案设计 (1) 2.1 基本设计原理 (1) 2.2 方案整体框图 (2) 第3章系统硬件电路设计 (2) 3.1 复位电路 (2) 3.2晶振电路 (3) 3.3 LED数码管显示电路 (3) 第4章系统软件设计 (4) 4.1 主程序流程图 (4) 4.2 初始化模块 (5) 4.3 信号频率测量模块 (5) 4.4 数码管显示模块 (5) 十进制加法计算器设计报告 目录 1、摘要----------------------------------------------------------------------2 2、设计任务和要求--------------------------------------------------------2 3、单片机简要原理--------------------------------------------------------2 3.1 AT89C51的介绍------------------------------------------------3 3.2 单片机最小系统------------------------------------------------6 3.3 七段共阳极数码管---------------------------------------------7 4、硬件设计-----------------------------------------------------------------7 4.1 键盘电路的设计-------------------------------------------------8 4.2 显示电路的设计-----------------------------------------------9 5、软件设计------------------------------------------------------------10 5.1 系统设计------------------------------------------------------10 5.2 显示与按键设计---------------------------------------------12 6、系统调试.-------------------------------------------------------------13 6.1系统初始状态的调试------------------------------------------13 6.2键盘输入功能的调试-----------------------------------------14 6.3系统运算功能的调试------------------------------------------16 7、心得体会与总结---------------------------------------------------------16 参考文献---------------------------------------------------------------------17 附录1 系统硬件电路图--------------------------------------------------18 附录2 程序清单-----------------------------------------------------------19 -----------十进制4位加法计数器设计

电子线路实训——五进制计数器

单片机频率计数器课程设计

verilog HDL十进制加减法计数器报告

做一个五进制的加减法计数器

单片机一个按键的多次击键组合判别技巧

数字电子技术课程设计-同步五进制加法计数器-D触发器JK触发器

实验十进制加减法计数器

基于单片机的光电计数器课程设计

10进制加法计数器课程设计

十进制加法计数器

十进制加法计数器

单片机课设频率计数器

加法计算器