EDA多路选择器设计实验报告

多路选择器设计实验

一、实验目的:

进一步熟悉Quartus II的Verilog文本设计流程,组合电路的设计仿真和硬件测试。

二、实验内容:

1、根据4.1节流程,利用Quartus II完成4选1多路选择器的文本代码编辑输

入和仿真测试等步骤,给出仿真波形。

2、在实验系统上硬件测试,验证此设计的功能。

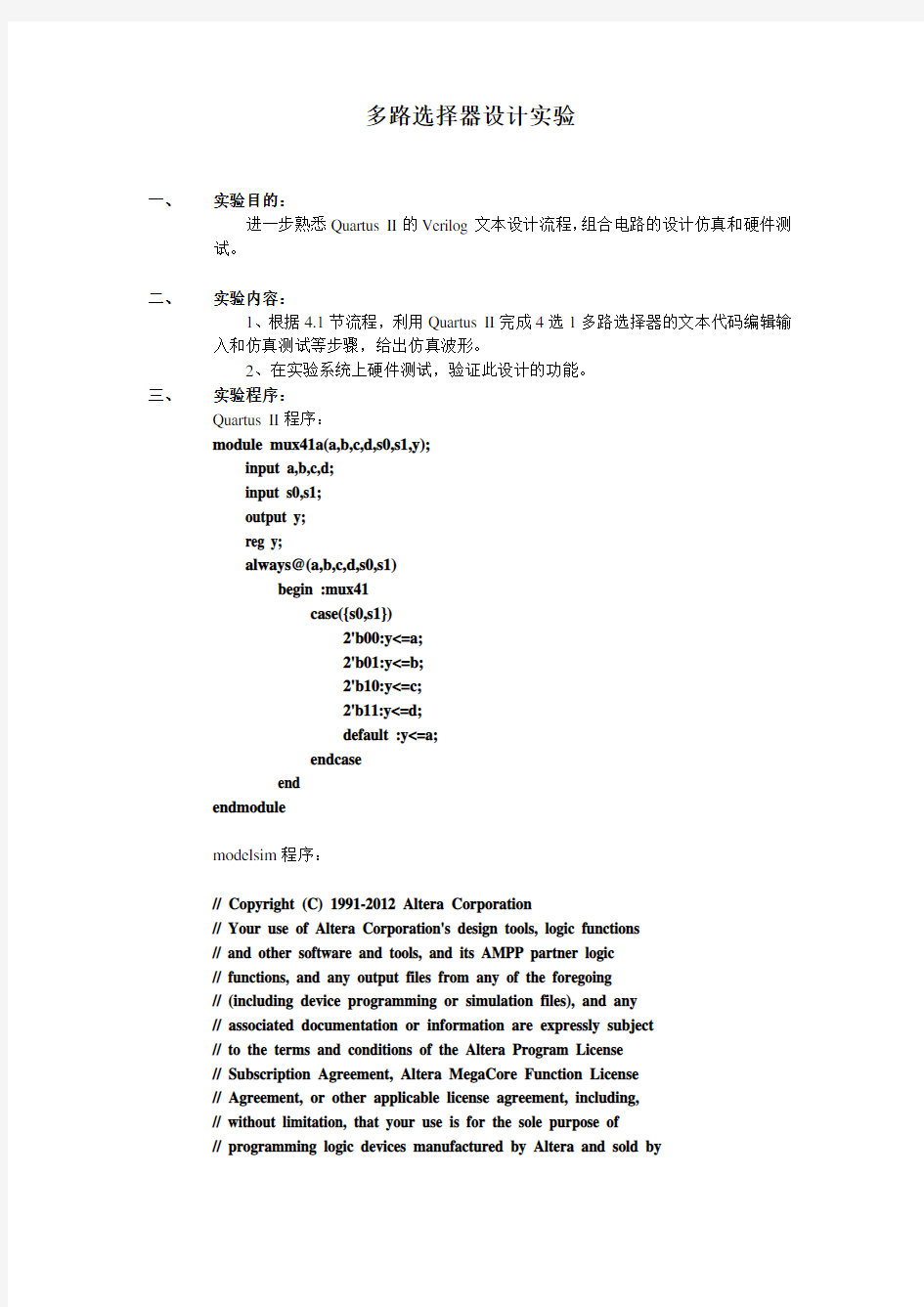

三、实验程序:

Quartus II程序:

module mux41a(a,b,c,d,s0,s1,y);

input a,b,c,d;

input s0,s1;

output y;

reg y;

always@(a,b,c,d,s0,s1)

begin :mux41

case({s0,s1})

2'b00:y<=a;

2'b01:y<=b;

2'b10:y<=c;

2'b11:y<=d;

default :y<=a;

endcase

end

endmodule

modelsim程序:

// Copyright (C) 1991-2012 Altera Corporation

// Your use of Altera Corporation's design tools, logic functions

// and other software and tools, and its AMPP partner logic

// functions, and any output files from any of the foregoing

// (including device programming or simulation files), and any

// associated documentation or information are expressly subject

// to the terms and conditions of the Altera Program License

// Subscription Agreement, Altera MegaCore Function License

// Agreement, or other applicable license agreement, including,

// without limitation, that your use is for the sole purpose of

// programming logic devices manufactured by Altera and sold by

// Altera or its authorized distributors. Please refer to the

// applicable agreement for further details.

//

*********************************************************************** ******

// This file contains a Verilog test bench template that is freely editable to

// suit user's needs .Comments are provided in each section to help the user

// fill out necessary details.

//

*********************************************************************** ******

// Generated on "10/11/2015 21:31:33"

// Verilog Test Bench template for design : mux41a

//

// Simulation tool : ModelSim-Altera (Verilog)

//

`timescale 1 us/ 1 ps

module mux41a_vlg_tst();

// constants

// general purpose registers

//reg eachvec;

// test vector input registers

reg a;

reg b;

reg c;

reg d;

reg s0;

reg s1;

// wires

wire y;

// assign statements (if any)

mux41a i1 (

// port map - connection between master ports and signals/registers .a(a),

.b(b),

.c(c),

.d(d),

.s0(s0),

.s1(s1),

.y(y)

);

initial

begin

a=0;b=0;

c=0;d=0;

s0=0;s1=0;

#20 s0=0;s1=1;

#20 s0=1;s1=0;

#20 s0=1;s1=1;

#20 $stop;

end

always #2 a=~a;

always #4 b=~b;

always #6 c=~c;

always #8 d=~d;

endmodule

四、实验步骤:

1、打开Quartus II,点击“file”中的“New Project Wizard”,新建工程到指定文

件夹中

2、点击“New”新建工作簿,写入程序

3、点击“compile design”进行编译

方法一:联合仿真

1、点击“processing”中的“start”

2、点击“file”中的“open”,找到“modelsim”,查找“.vt”文件

3、打开“mux41a”文件

4、修改文件中的程序

5、打开“Assignments”,点击“setting”,修改时间

6、点击“test benches”后再点击“New”添加“mux41a”文件

7、再进行编译

8、点击“Tools”,打开“Run Simulation Tool”,再选择“RTL Simulation”

1、在modelsim中新建“sim”文件

2、打开“modelsim”,创建工程

3、点击“create new file”,新建两个工作簿

4、分别添加相应程序进去,进行编译

5、选择library,点击work,之后再右击add→to wave→selected signals,最后选择simulate点击run→run all